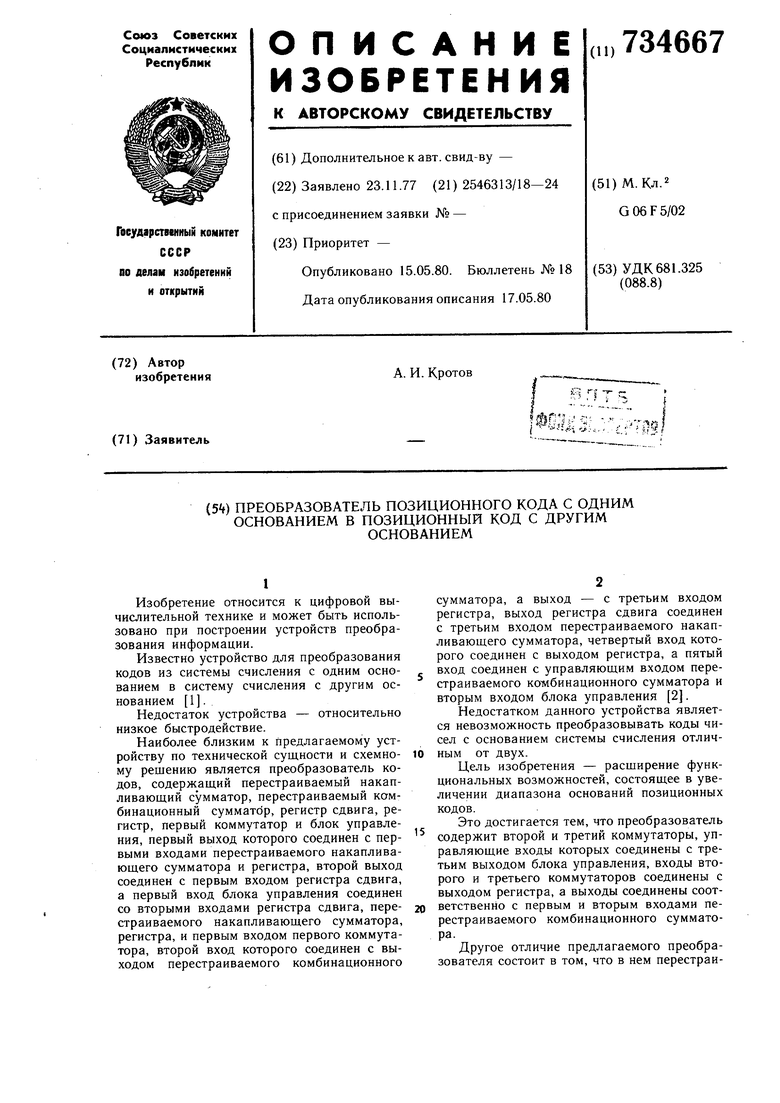

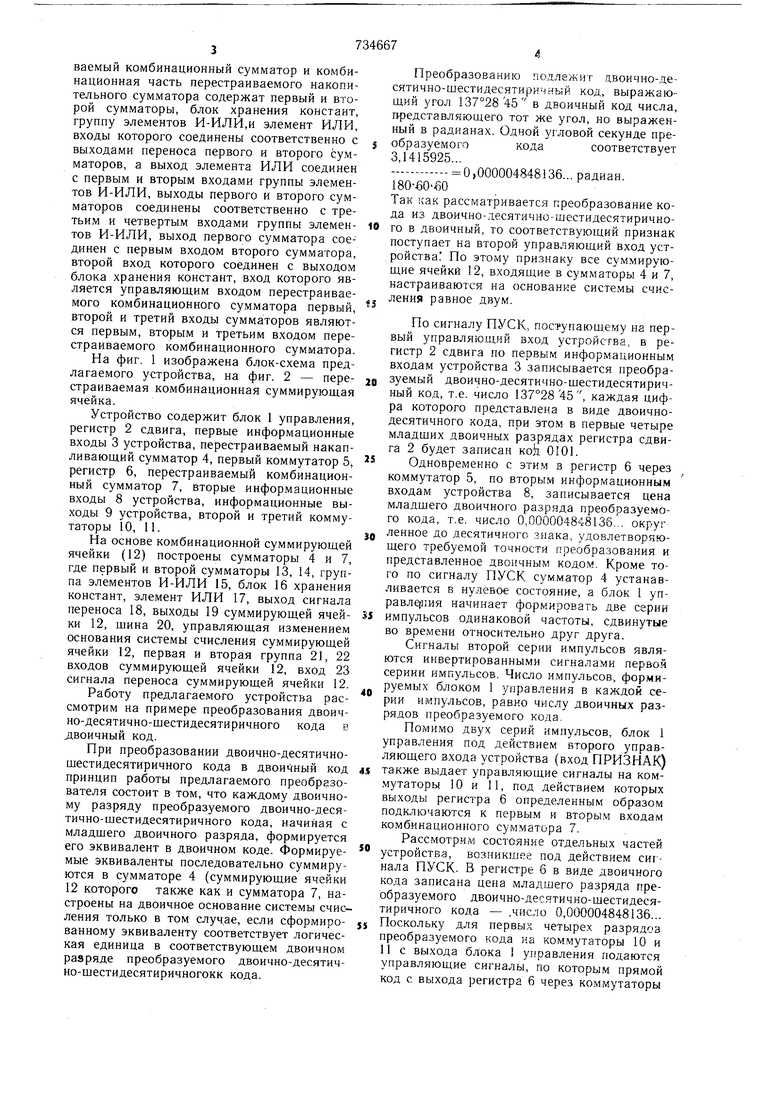

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств преобразования информации. Известно устройство для преобразования кодов из системы счисления с одним основанием в систему счисления с другим основанием 1. Недостаток устройства - относительно низкое быстродействие. Наиболее близким к Предлагаемому устройству по технической сущности и схемному решению является преобразователь кодов, содержащий перестраиваемый накапливающий сумматор, перестраиваемый комбинационный сумматор, регистр сдвига, регистр, первый коммутатор и блок управления, первый выход которого соединен с первыми входами перестраиваемого накапливающего сумматора и регистра, второй выход соединен с первым входом регистра сдвига, а первый вход блока управления соединен со вторыми входами регистра сдвига, перестраиваемого накапливающего сумматора, регистра, и первым входом первого коммутатора, второй вход которого соединен с выходом перестраиваемого комбинационного сумматора, а выход - с третьим входом регистра, выход регистра сдвига соединен с третьим входом перестраиваемого накапливающего сумматора, четвертый вход которого соединен с выходом регистра, а пятый вход соединен с управляющим входом перестраиваемого комбинационного сумматора и вторым входом блока управления 2. Недостатком данного устройства является невозможность преобразовывать коды чисел с основанием системы счисления отличным от двух. Цель изобретения - расширение функциональных возможностей, состоящее в увеличении диапазона оснований позиционных кодов. Это достигается тем, что преобразователь содержит второй и третий коммутаторы, управляющие входы которых соединены с третьим выходом блока управления, входы второго и третьего коммутаторов соединены с выходом регистра, а выходы соединены соответственно с первым и вторым входами перестраиваемого комбинационного сумматора. Другое отличие предлагаемого преобразователя состоит в том, что в нем перестраиваемый комбинационный сумматор и комбинационная часть перестраиваемого накопительного сумматора содержат первый и второй сумматоры, блок хранения констант, группу элементов И-ИЛИ,и элемент ИЛИ, входы которого соединены соответственно с выходами переноса первого и второго сумматоров, а выход элемента ИЛИ соединен с первым и вторым входами группы элементов И-ИЛИ, выходы первого и второго сумматоров соединены соответственно с третьим и четвертым входами группы элементов И-ИЛИ, выход первого сумматора соединен с первым входом второго сумматора, второй вход которого соединен с выходом блока хранения констант, вход которого является управляющим входом перестраиваемого комбинационного сумматора первый, второй и третий входы сумматоров являются первым, вторым и третьим входом перестраиваемого комбинационного сумматора. На фиг. 1 изображена блок-схема предлагаемого устройства, на фиг. 2 - перестраиваемая комбинационная суммирующая ячейка. Устройство содержит блок 1 управления, регистр 2 сдвига, первые информационные входы 3 устройства, перестраиваемый накапливающий сумматор 4, первый коммутатор 5, регистр 6, перестраиваемый комбинационный сумматор 7, вторые информационные входы 8 устройства, информационные выходы 9 устройства, второй и третий коммутаторы 10, 11. На основе комбинационной суммирующей ячейки (12) построены сумматоры 4 и 7, где первый и второй сумматоры 13, 14, группа элементов И-ИЛИ 15, блок 16 хранения констант, элемент ИЛИ 17, выход сигнала переноса 18, выходы 19 суммирующей ячейки 12, щина 20, управляющая изменением основания системы счисления суммирующей ячейки 12, первая и вторая группа 21, 22 входов суммирующей ячейки 12, вход 23 Сигнала переноса суммирующей ячейки 12. Работу предлагаемого устройства рассмотрим на примере преобразования двоично-десятично-шестидесятиричного кода в двоичный код. При преобразовании двоично-десятичнощестидесятиричного кода в двоичный код принцип работы предлагаемого преобразователя состоит в том, что каждому дйоичному разряду преобразуемого двоично-десятично-шестидесятиричного кода, начиная с младшего двоичного разряда, формируется его эквивалент в двоичном коде. Формируемые эквиваленты последовательно суммируются в сумматоре 4 (суммирующие ячейки 12 которого также как и сумматора 7, настроены на двоичное основание системы счисления только в том случае, если сформированному эквиваленту соответствует логическая единица в соответствующем двоичном разряде преобразуемого двоично-десятично-шестидесятиричногокк кода. преобразованию подлежит двоично-деятично-шестидесятирнчный код, выражающий угол 137°2845 в двоичный код числа, гфедставляющего тот же угол, но выраженный в радианах. Одной угловой секунде пребразуемогокодасоответствует3,1415925... ,000004848136... радиан. 180-60еО Так как рассматривается преобразование кода из двоично-десятично-шестидесятиричного в двоичный, то соответствующий признак поступает на второй управляющий вход устройства По этому признаку все суммирующие ячейки 12, входящие в сумматоры 4 и 7, настраиваются на основание системы счисления равное двум. По сигналу ПУСК, поступающему на первый управляющий вход устройства, в регистр 2 сдвига по первым информационным входам устройства 3 записывается преобразуемый двоично-десятично-щестидесятиричный код, т.е. число 37°2845, каждая цифра которого представлена в виде двоичнодесятичного кода, при этом в первые четыре младших двоичных разрядах регистра сдвига 2 будет записан коЬ 0101. Одновременно с этим в регистр 6 через коммутатор 5, по вторым информационным входам устройства 8, записывается цена младщего двоичного разряда преобразуемого кода, т.е. число 0,000004848136... округ ленное до десятичного знака, удовлетворяющего требуемой точности преобразования и представленное двоичным кодом. Кро.ме того по сигналу ПУСК сумматор 4 устанавливается в нулевое состояние, а блок 1 управл ния начинает формировать две серии импульсов одинаковой частоты, сдвинутые во времени относительно друг друга. Сигналы второй серии импульсов являются инвертированными сигналами первой сериии импульсов. Число импульсов, формируемых блоком 1 управления в каждой серии импульсов, равно числу двоичных разрядов преобразуемого кода. Помимо двух серий импульсов, блок 1 управления под действием второго управляющего входа устройства (вход ПРИЗНАК) также выдает управляющие сигналы на коммутаторы 10 и 11, под действием которых выходы регистра 6 определенным образом подключаются к первым и вторы.м входам комбинационного сумматора 7. Рассмотрим состояние отдельных частей устройства, возникшее под действием сигнала ПУСК. В регистре 6 в виде двоичного кода записана цена младшего разряда преобразуемого двоично-дееятично-щестидесятиричного кода - .число 0,000004848136... Поскольку для первых четырех разрядов преобразуемого кода на коммутаторы 10 и 11 с выхода блока 1 управления подаются управляющие сигналы, по которым прямой код с выхода регистра 6 через коммутаторы 10 и 11 подается соответственно на первый и второй входы комбинационного сумматора 7, то на его выходах, а соответственно на входах регистра 6 (через коммутатор 5, который на все время преобразования соединяет выходы комбинационного сумматора 7 со входами регистра 6) возникает удвоенная цена младшего двоичного разряда - число 0,000009696272..., представленное в двоичном коде, поскольку все суммирующие ячейки 12, входящие в состав сумматоров 4 и 7 настроены, на основание системы счисления равное двум. Выходы регистра 6 также соединены со входами накопительного сумматора 4. Так как в младщем разряде регистра 2 сдвига была записана логическая единица, то на входе запрета накопительного сумматора 4 присутствует сигнал разрешения сложения. По первому сигналу, поступающему со второго выхода блока I управления, сумматор 4 производит сложение цены младшего двоичного разряда с нулем, а в регистр 6 записывается удвоенная цена младшего двоичного разряда. После окончения действия первого сигнала, с первого выхода блока 1 управления поступает сигнал, по которому содержимое регистра 2 сдвигается на один разряд в сторону младших разрядов, т.е. во втором разряде станет логическая единица, а в первом - логический нуль. Логический нуль в младшем разряде регистра 2 сдвига поступает на вход запрета сложения накопительного сумматора 4 и запрещает его работу. Таки образом в результате действия второго сигнала со второго выхода блока 1 управления в накопительном сумматоре остается пена младшего двоичного разряда преобразуемого кода, а в регистр 6 запишется с выхода комбинационного сумматора 7 учетверенная первоначальная цена младшего двоичного разряда - число 0,000019392544..., представленное в двоичном коде, т.е. цена, соответствующая третьему двоичному разряду преобразуемого кода. Затем под действием сигнала с первого выхода блока 1 управления, содержимое регистра 2 сдвигается на один разряд в сторону младщих разрядов, т.е. в младшем двоичном разряде станет логическая единица и т.д. После третьего сдвига содержимого регистра 2, в регистре 6 находится в виде двоичного кода величина в восемь раз больше, чем первоначальная цена младшего двоичного разряда преобразуемого кода. Чтобы не исказился результат преобразования, в регистре 6 необходимо получать в двоичном коде величину в десять раз большую, чем первоначальная цена младшего двоичного разряда преобразуемого кода, поскольку после четвертого сдвига содержимо го регистра 2 цена его младшего двоичного разряда станет равной десяти секундам. Для этого после третьего сдвига содержимого регистра 2, в момент выдачи сигнала по второму выходу блока 1 управления, последний также выдает сигнал управления, по которому один из коммутаторов 10 или 11 начинает передавать содержимое регистра 6 на соответствующие входы комбинационного сумматора 7 со сдвигом вправо на два двоичных разряда, что соответствует уменьшению содержимого регистра 6 в четыре раза. Таким образом в регистр 6 будет записано в двоичном коде удесятиренная первоначальная цена младшего двоичного разряда преобразуемого кода. Далее блок 1 управления выдает на коммутаторы 10 и 11 управляющие сигналы, по которым содержимое регистра 6 без изменений подается на входы перестраиваемого комбинационного сумматора 7, т.е. снова производится удвоение предыдущего числа находящегося в регистре 6 и сложение этого содержимого с содержимым накопительного сумматора 4, если в младщем разряде регистра 2 сдвига находится логическая единица. После седьмого сдвига содержимого регистра 2 в регистре 6 будет находиться величина в восемьдесят раз больщая, чем первоначальная цена младшего двоичного разряда -преобразуемого кода. Так как в результате восьмого сдвига содержимого регистра 2 цена его младшего двоичного разряда станет равной одной минуте или щестидесяти секунд, то чтобы не исказился, результат преобразования в регистре 6 перед восьмым сдвигом необходимо получить в щестьдесят раз большую величину, чем первоначальная цена младшего двоичного разряда преобразуемого кода. Для этого после седьмого сдвига содержимого регистра 2, в момент выдачи сигнала по второму выходу блока управления 1, последний также выдает сигналы управления, по кторым один из коммутаторов 10 или 11 начинает передавать содержимое регистра 6 на соответствующие входы комбинационного сумматора 7 со сдвигом вправо на один двоичный разряд, а другой коммутатор начинает передавать содержимое регистра 6 на соответствующие входы комбинационного сумматора 7 со сдвигом вправо на два двоичных разряда, что соответствует уменьшению содержимого регистра 6 соответственно в два и четыре раза. Таким образом в регистр 6 будет записано в двоичном коде в щестьдесят раз больщая величина, чем первоначальная цена младшего двоичного разряда преобразуемого кода, поскольку в результате восьмого сдвига содержимого регистра 2 цена его младщего двоичного разряда станет равной одной минуте или шестидесяти секундам. Аналогичным образом для каждого следующего двоичного разряда преобразуемого дво ично-десятично-шестидесятиричного кода с учетом цены этого разряда с помощью комбинационного сумматора 7 и коммутаторов 10 и 11, управляемых от блока 1 управления, в регистре 6 образуются двоичные эквиваленты преобразуемого кода, которые складываются в накопительном сумматоре 4 при наличии логической единицы в младшем разряде регистра 2 сдвига.

Процесс преобразования кода из двоично-десятично-шестидесятиричного в двоичный занимает число периодов тактовой частоты, задаваемой блоком управления I, равное числу двоичных разрядов преобразуемого кода.

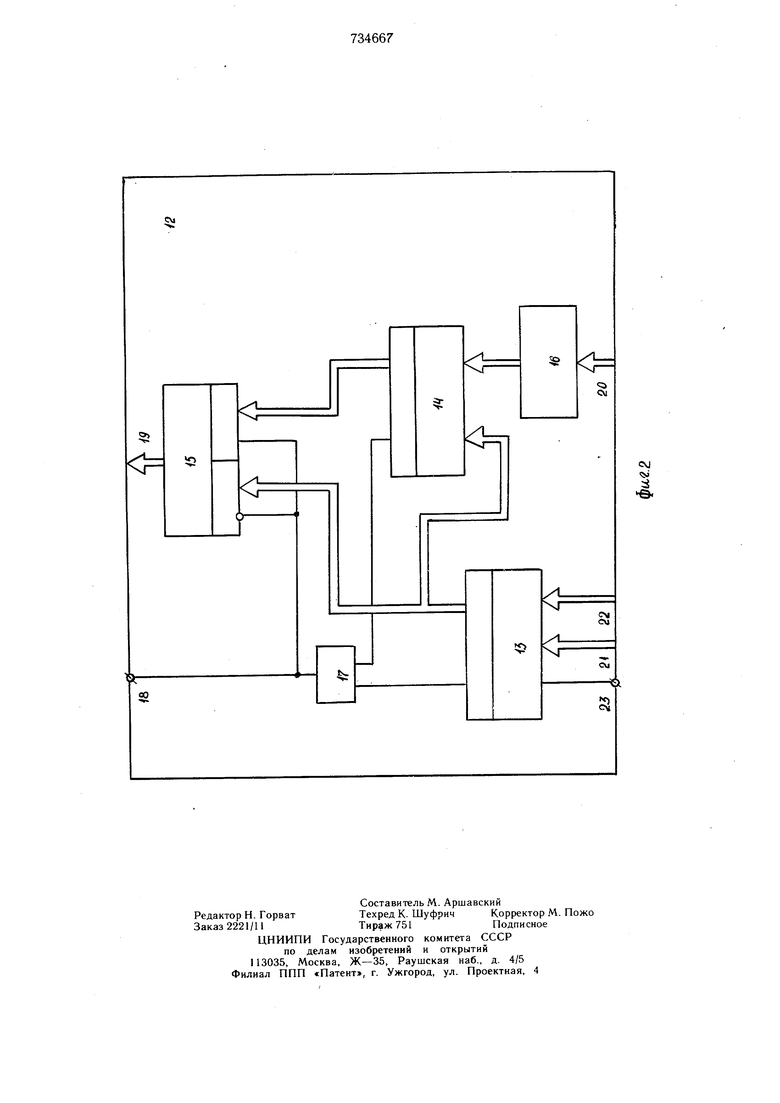

Для лучшего понимания работы предлагаемого устройства на фиг. 2 приведен пример возможной реализации перестраиваемых комбинационных суммирующих ячеек, входяших в состав сумматоров 4 и 7, поскольку накопительный сумматор 4 может быть построен на основе комбинационного сумматора и регистра памяти.

Перестраиваемая суммирующая ячейка 12 состоит из двух комбинационных суммирующих блоков 13 и 14 группы элементов И-ИЛИ 15, блока 16 логических констант и элемента ИЛИ 17. Выход элемента ИЛИ 17 соединен с первым и вторым входом группы элементов И-ИЛИ 15, управляющими соответственно подключением выходов сумматора 13 или выходов сумматора 14, через группу элементов И-ИЛИ 15 на выходы 19 суммирующей ячейки 12. Выходы суммирующего блока 13 соединены с первой группой входов суммирующего блока 14, а также с третьими входами в группы элементов И-ИЛИ 15, четвертые входы которых соединены с выходами суммирующего блока 14, вторая группа входов которого соединена с выходами блока 16 логических констант, входы которого соединены со входами 20, управляющими изменением основания системы счисления суммирующей ячейки 12. Выход сигналов переноса суммирующих блоков 13, 14 через элемент ИЛИ 17 поступает на выход 18, являющийся выходом сигнала переноса суммирующей ячейки 12.

Первая 21, вторая 22 группы входов, а также вход 23 сигнала переноса суммирующего блока 13 являются входами суммирующей ячейки 12.

Суммирующую ячейку 12 можно настроить по входам 20 на любое основание системы счисления Р, где 2 2 (п - число двоичных разрядов блоков 13 и 14). При этом блок 16 логических констант должен выдавать двоичный код коррекции числа х 2 -Р, где п-число двоичных разрядов суммирующих блоков 13 и 14, Р - основание системы сч-исления, на которую настроена суммирующая ячейка 12.

Соответственно, зная основание системы счисления, с которым должна работать перестраиваемая суммирующая ячейка 12, можно определить минимальное число п двоичных рязрядов, которые должны содержать

блоки 13 и 14; n log2p, где запись jt означает округление в сторону ближайшего большего числа, если t дробное.

В целях унификации оборудования целесообразно иметь перестраиваемую суммирующую ячейку 12, у которой суммирующие блоки 13 и 14 имеют по четыре двоичных разряда, что также удовлетворяет большинству практически встречающихся случаев преобразования кодов. В этом случае суммирующая ячейка 12 может быть настроена на работу с основанием системы счисления

0 от двух до шестнадцати.

Следует отметить, что чем на меньшее основание системы счисления должна быть построена суммирующая ячейка 12, гем больщей избыточностью в затратах оборудования она обладает. Например, для системы счисления с основанием р 2 достаточно иметь в суммирующей ячейке 2 одноразрядные, а для системы счисления с основанием Р 3 двухразрядные блоки 13 и 14, в то время как выбор был сделан на четырехразрядных бло0ках 13 и 14.

Для того, чтобы избежать ненужных затрат оборудования четырехразрядная суммируюшая ячейка 12 (т.е. ячейка, Л которой блоки 13 и 14 имеют по четыре двоичных разряда) рассматривается Для таких слу5чаев как состоящая из четырех независимых одноразрядных (для ) или двух независимых двухразрядных (дляр 3) суммирующих ячеек 12. В этом случае, в соответствии с ранее приведенным выражением

0 для определения двоичного кода коррекции X, блок 16 логических констант должен выдавать четырехразрядный код коррекции 0000 (для р 2) и 0101 для (р 3).

Назначение отдельных блоков, входящих в состав перестраиваемой суммирующей

5 ячейки 12, следующее: суммирующий блок 13 производит сложение кодов чисел, поступающих по входам 21 м 22. Суммирующий блок 14 корректирует двоичный код с выхода блока 13, если на выходе суммирующего блока 13 сформировался двоичный код числа большего, чем основание новой системы счисления. Код коррекции поступает на вход блока 14 от блока 16 логических констант. Значение кода коррекции задается по входам 20 суммирующей ячейки 12.

5 Группа элементов И-ИЛИ 15 подключат на выходы 19 суммирующей ячейки 12 выходы блока 13, а на время действия сигнала переполнения, поступающего с выхода элемента ИЛИ 17, - выходы суммирующего блока 14.

0

Для большей наглядности рассмотрим конкретный числовой пример.

Пусть по входам 20 суммирующая ячейка 12настроена на основание системы счисления равное шести. Пусть также на входы

21поступает код 0100 - число 4, на входы

22поступает код 0010 - число 2, а на вход

23поступает сигнал переноса с предыдущей младшей суммирующей ячейки. Тогда суммирующий блок 13 формирует на выходе двоичный код 0111 - число 7. Сумматор 14 суммирует код 0111с кодом коррекции 1010 число 10, так как мы рассматриваем суммирующую ячейку 12, настроенную по входам 20 на основание системы счисления равное шести. Поскольку результат сложения равный числу 17, превышает число 15 - максимальное десятичное число, которое может быть выражено четырьмя двоичными разрядами суммирующего блока 14, то он формирует на выходе код 0001 - число 1, а также сигнал переполнения, по которому группа элементов И-ИЛИ 15 подключает выходы блока 14 на выходы 19. Кроме того сигнал переполнения суммирующего блока 14 через элемент ИЛИ 17 поступает на выход 18, формирующий сигнал переноса для следующей суммирующей ячейки. Таким образом на выходе суммирующей ячейки 12 формируется код 0001 - число 1 и си.гнал переполнения, что соответствует сумме чисел поступивших на входы суммирующей ячейки 12, настроенной на основание системы счисления равное шести. Процесс преобразования кодов с другими основаниями системы счисления не отличается от только что рассмотренного выше процесса преобразования кодов, необходимо только чтобы коммутаторы 10 и 11 соответствующим образом подключали выходы регистра 6 на входы комбинационного сумматора 7, для образования очередной цены младшего двоичного разряда регистра сдвига 2, что обеспечивается подачей управляюших сигналов с выхода блока управления 1 на управляющие вХоды коммутаторов 10 и 11. Таким образом введение двух коммутаторов 10 и 11 позволяет передавать содержимое регистра 6 на комбинационный сумматор 7 в зависимости от управляющих сигналов, поступающих с блока управления 1, в прямом или обратном коде, без сдвига или со сдвигом влево или вправо на соответствующее число двоичных разрядов, для образования очередной цены младшего двоичного разряда регистра сдвига 2. Тем самым обеспечивается гибкость работы устройства, что позволяет на одном и том же оборудовании осуществлять прямое и обратное преобразование кодов чисел из системы счисления с одним основанием в систему счисления с другим основанием. Использование предлагаемого устройства по сравнению с устройством (2) позволяет осуществлять преобразование кодов не только из двоичного в двоично-десятичный код, но также осуществлять обратное преобразование кодов из двоично-десятичного (двоично-десятично-шестидесятиричного) в двоичный код. Кроме того, структура заявляемого устройства обеспечивает преобразование кодов с любым основанием в коды с любыми другими основаниями, при этом сохраняются все положительные качества устройства, такие как: 2) получение любой требуемой точности а)получение любой требуемой точности преобразования; б)высокое быстродействие; в)большая гибкость и простота при выборе требуемого вида преобразования. Таким образом, использование предлагае мого устройства позволяет удовлетворить большему числу одновременно возникаюших требований, предъявляемых к преобразователю и позволяет на одном и том же оборудовании преобразовывать коды с различными основаниями системы счисления вместо ряда устройств, каждое из которых обеспечивает преобразование кодов с каким то одним основанием системы счисления. Формула изобретения 1. Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием, содержащий перестраиваемый накапливающий сумматор, перестраиваемый комбинационный сумматор, регистр сдвига, регистр, первый коммутатор и блок управления, первый выход которого соединен с первыми входами перестраиваемого накапливающего сумматора и регистра, второй выход соединен с первым входом регистра сдвига, а вход блока управления соединен со вторыми входами регистра сдвига, перестраиваемого накапливающего сумматора, регистра и первым входом первого коммутатора, второй вход которого соединен с выходом перестраиваемого комбинационного сумматора, а выход первого коммутатора соединен с третьим входом регистра, выход регистра сдвига соединен с третьим входом перестраиваемого накапливающего сумматора, четвертый вход которого соединен с выходом регистра, а.пятый вход соединен с входом управляющим перестраиваемого комбинационного сумматора и вторым входом блока управления, отличающийся тем, что, с целью расширения функциональных возмож ностей, за счет расширения диапазона оснований позиционных кодов, он содержит второй и третий коммутаторы, управляющие входы которых соединены с третьим выходом блока управления, входы второго и третьего коммутаторов соединены с выходом регистра, а выходы соединены соответственно с первым и вторым входами перестраиваемого комбинационного сумматора. 2. Преобразователь по п. 1, отличающийся тем, что в нем перестраиваемый комбинационный сумматор и комбинационная часть перестраиваемого накапливающего сумматора содержит первый и второй сумматоры, блок хранения констант, группу элементов И-ИЛИ и элемент ИЛИ,

входы которого соединены соответственно с выходами переноса первого и второго сумматоров, и выход элемента ИЛИ соединен с первым и вторым входами группы элементов И-ИЛИ, выходы первого и второго сумматоров соединены соответственно с третьим и четвертым входами группы элементов И-ИЛИ, выход первого сумматора соединен с первым входом второго сумматора, второй вход которого соединен с выходом блока хранения констант, вход которого является управляющим входом перестраиваемого комбинационного сумматора, первый: второй и третий входы сумматоров являются первым, вторым и третьим входами перестраиваемого комбинационного сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 526884,. кл. G 06 F 502, 1976.

2.Авторское свидетельство СССР по заявке № 2348294, кл. G 06 F 5/02.

J

CVJ 4J

4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

x

г

CM

л

00

cv

ev

Авторы

Даты

1980-05-15—Публикация

1977-11-23—Подача