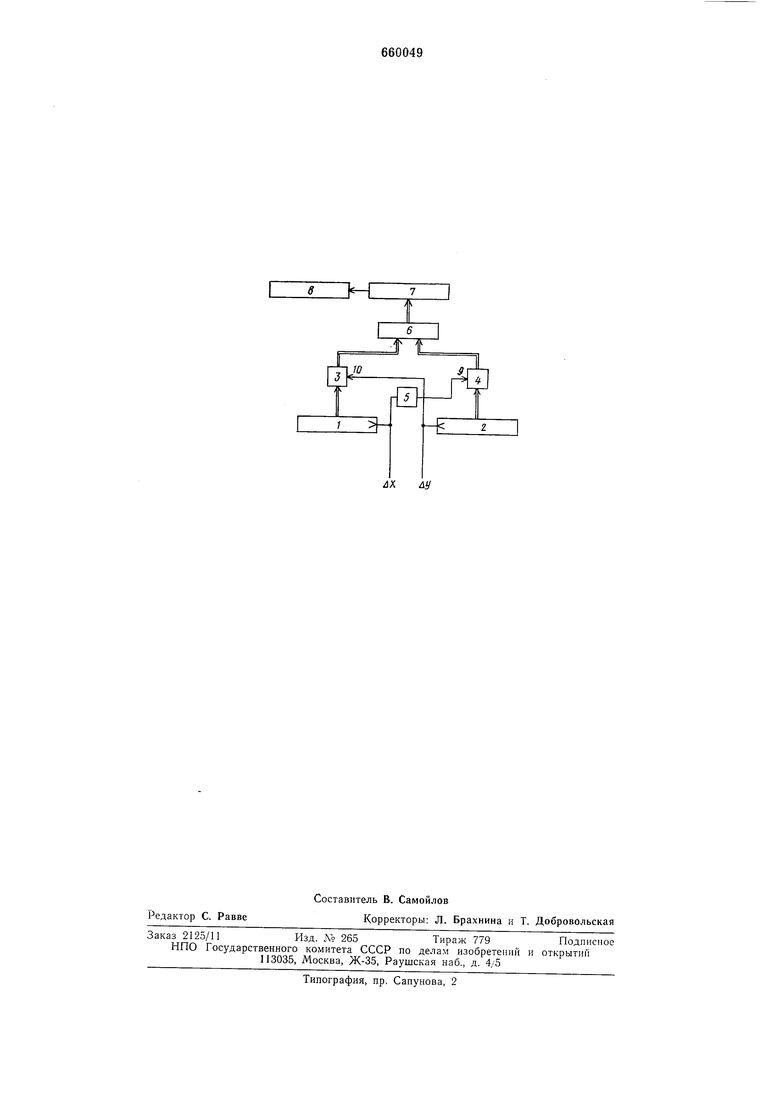

второго сомножителя, один из входов которого соединен с выходом счетчика 1, а второй из входов соединен со входом счетчика 2, блок 4 умножения второго сомножителя на единичное приращение первого сомножителя, один из входов которого соединен с выходом счетчика 2, элемент 5 задержки, вход которого соединен со входом счетчика 1, а выход которого соединен с другим входом блока 4 умножения, элемент ИЛИ 6, входы которого соединены с выходами блоков 3 и 4 умножения, сумматор 7, вход которого соединен с выходом элемента ИЛИ 6, счетчик 8 результата, вход которого соединен с выходом сумматора 7.

Устройство работает следующим образом.

Перед началом вычислений начальные значения нервого и второго сомножителей заносятся соответственно в счетчик 1 и счетчик 2, младшие н старщие л-разрядов точного значения ироизведения - в выходной сумматор 7 и счетчик 8 результата. На входы счетчиков 1 и 2 одновременв;о постунают соответственно нриращения Ад; и Дг/ нредставляющие собой короткие имнульсы.

Принципиально схемы счетчиков 1 и 2 выполнены таким образом, что изменение состояния счетчиков происходит по заднему фронту счетных сигналов Ах и At, (что, например, осуществлено в счетчиках, выполненных на интегральных элементах 155 серии).

Таким образом, состояния счетчиков остаются неизменными в течение действия сигналов Ал и Аг/. Блоки умножения 3 и 4 срабатывают но переднему фронту сигналов А.-Г и Аг/. Поэтому в момент поступления сигналов и Аг/ только на выходе блока 3 умножения появляется сигнал, равный , поступающий через схему 6 на вход сумматора 7, переполнения с выхода которого поступают на вход счетчика 8, в котором суммируются с его содержимым ху.

Па выходе блока умножения 4 сигнал произведения г/-Ал отсутствует, что обусловлено отсутствием в этот момент времени на входе блока 4 сигнала А.Х, задержанного элементом задержки 5. Условие, которому доллсно удовлетворять время задержки т, вносимое элементом задержки 5, равно

,,

где Т4 - длительность импульсов Ах и Аг/; Т - максимальное время переходных процессов в схеме счетчиков.

Далее импульсы Ал- и Аг/ оканчиваются, состояния счетчиков х и г/ изменяются и становятся соответственно равными х + , г/ + Аг/. Теперь на выходе блока умножения

после ноступления на его вход 9 задержанного сигнала образуется значение (г/ + Аг/) Ал . Па выходе блока 3 величина произведения отсутствует из-за отсутствия сигнала At/ на входе 10.

Величина (г/ + Аг/)-Ал: поступает через элемент ИЛИ 6 на вход сумматора 7, с выхода которого переполнения поступают на вход счетчика 8. Величина, которая образуется в конечном итоге в сумматоре 7 и счетчике 8 представляет собой ничто иное, как точное значение произведения входных величин, равное

(л:+Дл:)(г/ + Дг/); сг/ +г/-Дл:+Дг/-.л:4-Д.х-Лг/

Формула изобретения

Устройство для умножения, содержащее

счетчик первого сомножителя, блок умножения нервого сомножителя на единичное приращение второго сомножителя, первый и второй входы которого соединены соответственно с выходом счетчика первого сомножителя и входом счетчика второго сомножителя, соединенного с шиной единичного приращения второго сомножителя, блок умножения второго сомножителя на единичное приращение первого сомножителя, первый вход которого соединен с выходом счетчика второго сомножителя, счетчик результата, вход которого соединен с выходом сумматора, отличающееся тем, что, с целью повышения точности устройства, оно содержит элемент ИЛИ и элемент задерл ки, вход которого соединен с шиной единичного приращения первого сомножителя и входом счетчика нервого сомножителя, выход - со вторым входом

блока умножения второго сомножителя на единичное приращение первого сомножителя, входы элемента ИЛИ соединены с выходами блоков умножения одного из сомножителей на единичное приращение второго сомножителя, выход элемента ИЛИ подключен ко входу сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 432525, кл. G 06G 7/16, 1972.

2.Песлуховский К. С. Цифровые дифференциальные анализаторы. М., «Машиностроение, 1968, стр. 90.

IS M

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1977 |

|

SU630628A1 |

| Стереоавтограф | 1960 |

|

SU147841A1 |

| Множительное устройство | 1979 |

|

SU781809A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| УСТРОЙСТВО для СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ДИСКРЕТНЫХ СИГНАЛОВ | 1973 |

|

SU386424A1 |

| Устройство для дифференцирования | 1983 |

|

SU1080142A1 |

| Устройство для формирования элементов расширенных полей Галуа GF ( @ ) и кодовых последовательностей на их основе | 1987 |

|

SU1441413A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

X

Авторы

Даты

1979-04-30—Публикация

1977-01-17—Подача