Известны стереоавтографы, содержащие вычислительнЬ1е устромства.

В предлагаемом стереоавтографе, предназначенном для быстрого определения объемов открытых разработок полезных ископаемых is т. п. по снимкам наземной стереосъемки, для повышения быстродействия и точности блок вычисления объемов содержит цифровой интегратор, реализуюисмй формулу Скмпсона с троичным кодированием приращений, выход которого для обеспечения переменного шага интегрирования соединен со входом через блок управления шагом, выполненным например, на линиях задержки с отводами и вентилях.

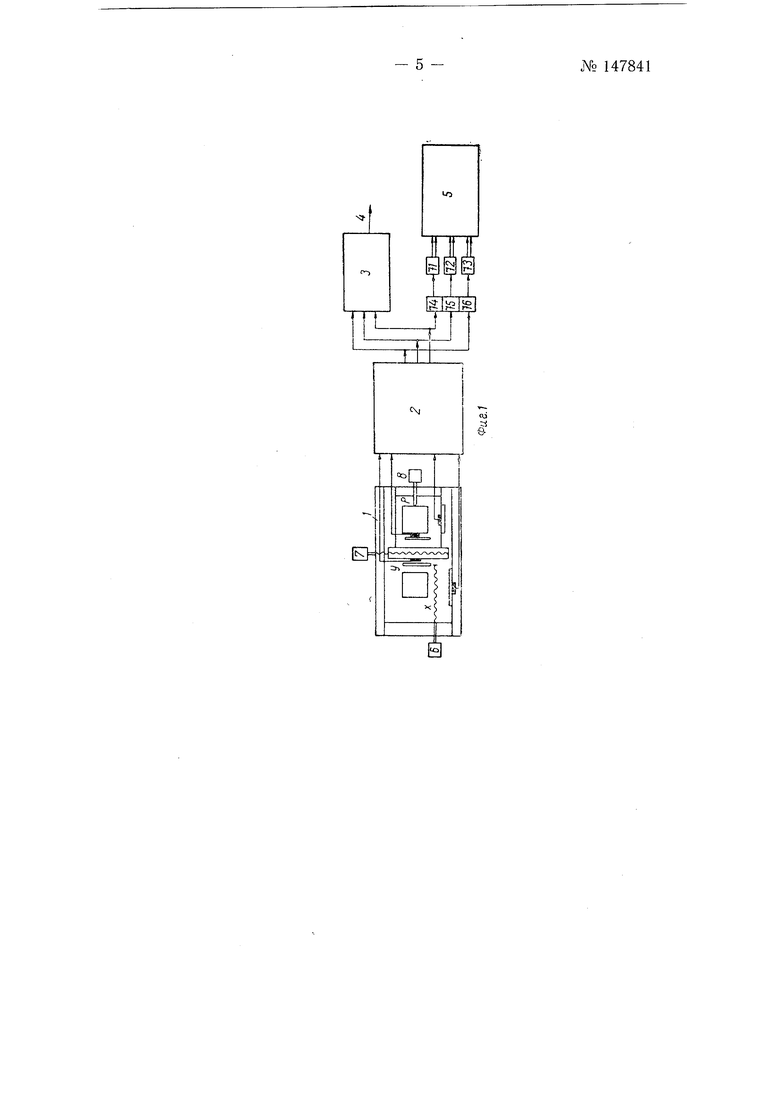

Ня фиг. 1 приведена функциональная схема описываемого стереоавтографа; на фиг. 2 - функциональная схема цифрового интегратора; па фиг. 3 - функциональная схема блока вычисления объемов.

Описываемый стереоавтограф состоит из стереокомпаратора I (измерительный блок), блока 2 преобразования координат, блока 3 подсчета объемов с выводом 4 на печать и координатографа 5. Стереокомпаратор снабжен преобразователями линейного перемещения кареток в унитарный код, а также двигателями 6, 7 и 8 для перемещения кареток, закрепленных на ходовых винтах л- и г/ и параллактическом винте р. Блок преобразования координат осуществляет трансформирование измеряемых координат в фотограмметрические. В качестве вычислительного ycTpoйctвa блока 2 применен цифровой интегратор, реаливуюп1,1;Г1 формулу Симпсона с троичным кодированием приращений, а такнчс устройство для интегрирования с переменным шагом.

Интегратор работает следующим образом. По команде а из устройства 9 управления из линий 10 и 11 задержки выбираютсй приращения, которые поступают на вход Д у интегратора. Если знак приращения положительный, то оно приходит прямым кодом через вентили 12

№ 147841- 2 и 13, причем последний управляется по второму входу напряжением с триггера 14, и схему 15 «ИЛИ на вход счетчика 16 (ЕДу). Если приращение отрицательно, то знак приращения, выбранный из линии // задержки, через вентиль 17 перебросит триггер 14 в состояние «1, вентиль 13 закроется, но откроется вентиль 18, который разрещит прохождение кода абсолютной величины приращения на схему 19 взятия дополнения. Дополнительный код приращения через схему 15 «ИЛИ проходит на вход счетчика 16. По сигналу из устройства управления открывается вентильная группа 20 и код 2Ау -переписывается на регистр 21 сдвига, из которого код последовательно выдается -на вход / сумматора 22. На вход // сумматора 22 поступает последовательным кодом значение подынтегральной функции у из линии 23 задержки.

Схема для интегрирования с переменным щагом состоит из трехразрядного счетчика 24, диодного дешифратора 25, вентилей 26 и переменной линии 27 задержки, состоящей из цепочки линий, время задержки каждой из которых равно времени между двумя соседними разрядами чисел (или периоду тактовой частоты). Перед началом вычитания в счетчик 24 дополнительным кодом заводится число семь, что соответствует высокому потенциалу на левой шине дешифратора (открыт левый вентиль). В процессе прохождения по линии 27 задержки код будет задержан на семь разрядов относительно масштабного импульса Н кода у. Поэтому младщий разряд кода ZAj/ будет складываться с седьмым разрядом кода у, считая от им-пульса Я. В результате на выходе сумматора 22 образуется код у у . Для реализации формулы интегрирования по трапециям код у задерживается в линии 28 на один такт по отношению к коду ЕАг/. Эта операция равносильна сдвигу вправо на один разряд кода SAy и образованию - 2А|/. В сумматоре 29 образуется код у ЕАг/ у + . , который передается

на вход вентиля 30. По второму входу этот вентиль управляется импульсами (Ал;), выбираемыми из линии 10 по команде b через вентиль 31 и схему 32 «ИЛИ. Если приращение Ал; имеет положительный знак, то высокий потенциал от сигнала через вентиль 55 образуется на

нулевом выходе триггера 34 и открывает вентиль 35. Код (у + 3

-г ) (Ах) через схему 36 «ИЛИ пройдет на вход // сумматора 37.

Если код АЛ; отрицателен, то передача кода произойдет дополнительным кодом через вентиль 38 и схему 39 взятия дополнения. Триггер 34 управляется импульсами из линии //, выбираемыми (одновременно с кодами по команде b через схему 40 «ИЛИ. Для вычисления составляющей 2A// Ад; приращения интеграла код БАу с выхода линии 27 задержки направляется на вход вентиля 41. По второму входу иоследний управляется сигналом (А;с) с выхода триггера 42, который запоминает абсолютное значение яриращения (Ал;) на время выполнения операции в интеграторе. Передача кода БАг/ через вентиль 41 равносильна умножению ЕАг/- (Ал:). В зависимости от знака Ах это произведение передается прямым (через вентиль 43} или дополнительным (вентиль 44 и схема 45 взятия дополнения) кодом на вход / сумматора 37 через схему 46 «ИЛИ. На выходе сумматора 57 образуется код

I (г/ + - EAt/) Ах / I sign Ах. - - | 2Аг/ Дх j sign Ах.

Этот код через линию 47 задержки, аналогичную линии 27 и управляемую от тех же шин дещифратора 25, поступает на вход / сумматора 48

1.3

На вход // последнего поступает код из линии 49 задержки. Назначение линии 47 состоит в задержке кода (у + 2Аг/) Ал; -Ь 2Лг/ Ах по

отношению к коду яа входе // на то же число разрядов, как и задержка кода 2Ау по отношению к коду у. На выходе сумматора 48 образуется приращение интеграла AZ, дробная часть которого переписывается в линию 49 Прямым, а в линию 50 дополнительным кодом (через схемы 51, 52 «ИЛИ и схему 53 «взятия дополнения). Единичное прираш,ение интеграла выделяется с помощью вентиля 54 и направляется в .линию 10 задержки. Знак единичного приращения образуется с помощью сумматора 55 как сумма знаков сомножителей (у+ -- 2Аг/) и

Ах, поступающих по команде с через вентили 56 и 57 соответственно. Результат суммирования знаков по команде d через вентиль 58 заносится в линию 11 задержки.

Цепь управления шагом независимой переменной Ал; действует следующим образом. Полученные в /- 1 итерации приращения интеграла и записанные в линии 50 дополнительным кодом сравниваются с приращениями интеграла, полученными в г-той итерации. Для правильности управления величиной щага достаточно, сравнивать абсолютные приращения интеграла только для того интегратора, в котором вырабатываются приращения искомой функции. Код номера этого интегратора и сигнал е из устройства управления, ему соответствующий, будет обозначать Мпф. Поэтому для выборки кода приращения функции достаточно на выходе линии 50 поставить вентиль 59, управляемый по второму входу потенциалом Nnф, длительность действия которого соответствует времени проведения операции в интеграторе Nnф.

В результате на вход // сумматора 60 (через схему 61 «ИЛИ) будет поступать только дополнительный код приращения функции интегратора пф, полученный в i-1 итерации. Аналогичным образо.м управляется вентиль 62, через который поступает на вход / сумматора 60 прямой код приращения функции, полученный в i итерации. В сумматоре 60 необходимо сравнивать не только дробные части приращений интеграла AZo, но и единичные приращения AZ,,. С этой целью единичное приращение, полученное в / - 1 итерации, выби1рается с помощью вентиля 63 из линии 10, преобразуется в дополнительный код схемой 64 и подается на вход // сумматора 60, т. е. в момент, когда на вход / подается ИМпульс переполнения, полученный в /-той итерации. Из получаемого на выходе сумматора 60 кода с помощью вентиля 65 выделяется только единичное приращение разности приращений е (AZ;,- + + Zni}Nnф (AZ,., + )Nnф.

Наличие или отсутствие этого единичного приращения разности f используется для управления величиной щага Ал . Если на выходе сумматора 60 образуется импульс единичного приращения, то это свидетельствует о том, что следующая итерация должна быть произведена с тем же щагом, т. е. разность приращений интегралов на двух соседних итерациях еще достаточно велика и для ее уменьшения шаг независимой переменной менять еще рано. Если же сигнал отсутствует, то для уточнения значения иолученного прирашения щаг нужно уменьшить. С этой целью сигнал вентиля 65 подается на вход счетчика 24. уменьшая записанное в нем число на «1. Следовательно, высокий потенциал возникает на второй левой шине дешифратора 25, откроется вентиль 26 второй слева и код у будет про.ходить по меньшей длине линии 27, что будет соответствовать сдвигу кода 1Лу относительно предыдущей итерации на один разряд вправо. Далее процесс будет аналогичен описанному.

- 3 147841

№ 147841- 4 Блок 3 подсчета объемов состоит из пяти иптеграторов 66, 67, 68, 69 и 70, скоммутированных по схеме, показанной на фиг. 3. Подсчет объема интересующего объекта мож-ет производиться как методом суммирования объемов элементарных горизонтальных сечений, так и методом суммирования объемов элементарных вертикальных сечений стереоскопической модели. Приращения dx, , и поступают с выхода блока 2 преобразования координат. Значение при интегрировании методом накопления сумм элементарных объемов представляет разность между двумя соседними уставками параллактического винта.

Координатограф 5 используется пр-и построении плана. Движение рисующего приспособления по осям х i у осуществляется щаговыми двигателями 7/, 72 и 75 (фиг. 1), которые управляются импульсами приращений координат Аг/,.р, ДХср, AZcp (через расП|ределители 74, 75 и 76 импульсов) при вычерчивании контуров с выхода блока преобразования координат.

Предмет изобретения

Стереоавтограф, предназначенный для быстрого определения объе.мов открытых разработок полезных ископаемых и т. п. по снимкам.наземной стереосъемки, содержащей стереокомпаратор, блок преобразования координат, блок вычисления объемов и координатограф, от л и чающийся тем, что, с целью повыщения быстродействия и точности, блок вычисления объемов содержит цифровой интегратор, реализующий формулу Симпсона с троичным кодированием приращений, выход которого для обеспечения переменного щага интегрирования соединен со входом через блок управления щагом, выполиевным, например, на линиях задержки с отводами и вентилях.

r

LJT

Nt

Ц)

A

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU415676A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для автоматического ввода координат точек аэроснимка в цифроаналоговую вычислительную машину | 1959 |

|

SU127042A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

Авторы

Даты

1962-01-01—Публикация

1960-12-26—Подача