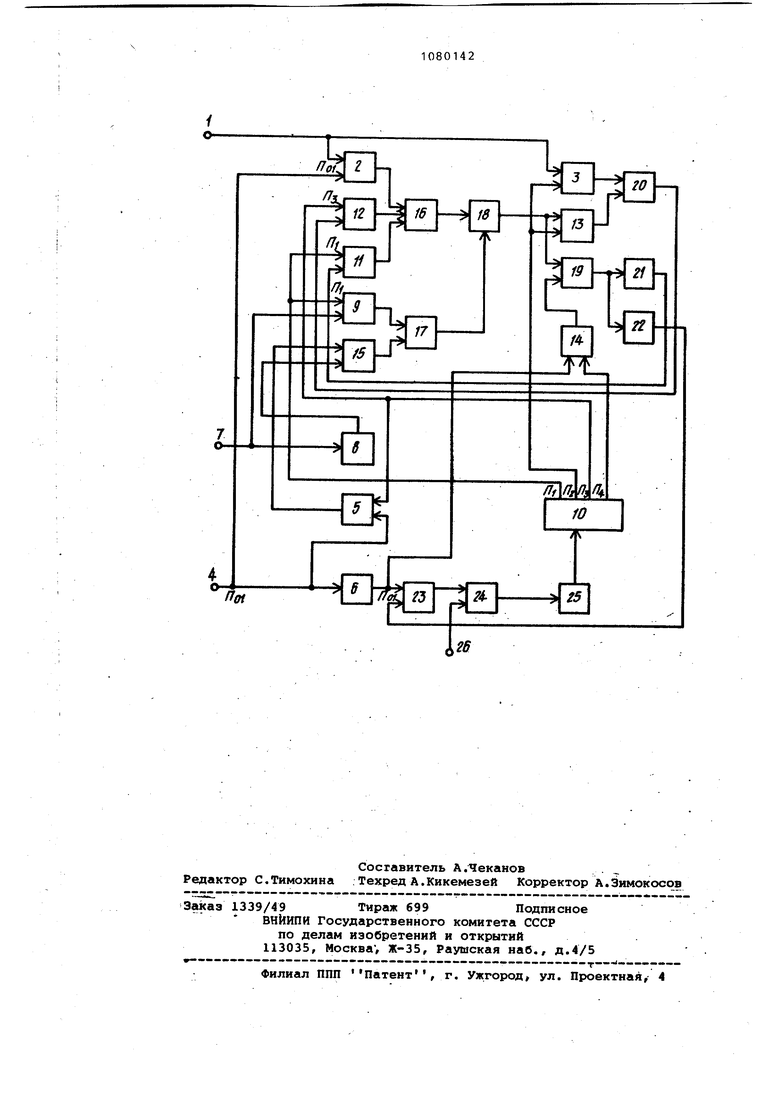

Изобретение относится к вычислительной технике и может быть исполь вано при разработке специализирован вычислительных устройств. Известно устройство для взятия производной, содержащее блок умноже ния, первый и второй сумматоры, эле менты И ч регистр производной ij . Это устройство характеризуется недостаточной точностью и повышенно сложностью. Наиболее близким к предлагаемому по технической сущности является устройство для дифференцирования, содержащее блок формирования приращений, схему умножения, первый и вто рой сумматоры, регистр производной, схемы сравнения и схемы совпадения. Причем вйходы блока формирования приращений и множительного устройств соединены со входами первого суммато ра, выход сумматора соединен со входом схемы сравнения и через схему совпадения, второй вход которой соединен с выходом схемы сравнения, соединен с выходом регистра, а выход - со входом регистра 2 . Однако такое устройство характери зуется достаточно низким быстродейст вием. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается те что в устройство, содержащее блок умножения, два сумматора, блок сравнения и элемент И, введены два элемента ИЛИ, две группы элементов ИЛИ блок вычисления обратной величины, семь групп элементов И, элемент задержки, триггер, счетчик, дешифратор и группа элементов И-НЕ, причем входы приращений подынтегральной функции устройства соединены с первыми входами элементов И первой и второй групп, выходы элементов И вто рой группы соединены с входами первого слагаемого первого сумматора, вход запуска устройства соединен с первым входом первого элемента ИЛИ и через элемент задержки подключен первому входу второго элемента ИЛИ ;входу установки в единицу триггера, выход которого соединен с первым вхо дом элемента и,выход которого соединен со счетным входом счетчика,выход которого соединены со входами дешифратора, первый которого подключен к первым входам элементов И третьей й четвертой групп, второй выход дешифратора соединен со вторы ми входами элементов И второй грулпы и первыми входами элементов И-НЕ группы, выходы которых соединены со входгши второго слагаемого первого сумматора, выходы которого подключены к первым вхрдам элементов И пятой группы, выходы которых соединены с первыми вхбдами элементов ИЛИ первой группы, выходы которых соединены с входами первого сомножителя блока умножения, входы приращений аргумента устройства подключены ко вторым входам элементов И третьей группы и входам блока вычисления обратной величины, выходы которого соединены с первыми входами элементов И шестой группы, выходы которых соединены с первыми входами элементов ИЛИ второй группы, выходы которых подключены к входам второго сомножителя блока умножения, выходы которого соединены со вторамя входами элементов И-НЕ группы и первьпиш входами элементов И седьмой группы, выходы которых соединены со входами блока сравнения и второго сумматора, выходы которого соединены со вторыми входами элементов И четвертой группы, выходы которых соединены со вторыми входами элементов ИЛИ первой группы, третий выход дешифратора .соединен со вторыми входами элементов И пятой группы и вторым входом первого элемента ИЛИ, выход которого подключен ко вторым входам элементов И шестой группы, четвертый выход дешифратора соединен со вторым входом второго элемента ИЛИ, выход которого подключен ко вторым входам элементов И седьмой группы, выход блока сравнения соединен с входом установки в ноль триггера, второй вход элемента И подключен к тактовому входу устройства, вход запуска устройства соединен со вторыми входами элементов И первой группы, выходы которых соединены с третьими входами элементов ИЛИ первой группы, выходы элементов И третьей группы соединены со вторыми входами элементов ИЛИ второй группы. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит входы 1 приращений подынтегральной функции, первую и вторую группы элементов И 2,3, вход 4 запуска устройства, первый элемент ИЛИ 5, элемент б задержки, входы 7 приращений аргумента, блок 8 вычисления обратной величины, третью группу элементов И 9, дешифратор 10, четвертую и пятую группы элементов И 11,12, группу элементов И-НЕ 13, второй элемент ИЛИ 14, шестую группу элементов И 15, первую и вторую группы элементов ИЛИ 16,17, блок 18 умножения, седьмую группу элементов И 19, первый и второй сумматоры 20, 21, блок 22 сравнения, триггер 23, элемент И 24, счетчик 25, тактовый вход устройства 26. Вход 1 устройства соединен со входами элементов И 2,3. Вход устройства 4 соединен со входами элементов И, 2, элемента ИЛИ 5 и элемента задержки 6. Вход устройства 7 соединен со входом блока 8 и входом элементов И 9. Выходы дешифратора 10 соединены со входами элементов И 3,9,11,12, элементов И-ИЕ 13 и элементов ИЛИ 5,14. Входы элементов И 15 соединены с выходбм .элемента ИЛИ 5 и блока 8. Выходы элементов И 2,11,12 и элементов И 9,15 через элементы ИЛИ 16,17 соединены со входами блока 18. Выход блока 18 соединен со входами элементов И 13, 19. Выходы элементов И 3, элементов И-НЕ 13 соединены со входами сумматора 20, выход последнего соединен со входом элементов И 12. Выход элемента ИЛИ 14 соединен со входом элемента И 19, выход последне го через сумматор 21 соединен со входом элемента И 11 и блока сравнения 22. Выход блока сравнения 22 и элемента задержки 6 соединен со входом триггера 23, выход последнего через элемент И 24 соединен со входо счетчика 25. Второй вход элемента И 24 соединен со входом устройства 26. Выход счетчика 25 соединен со входом дешифратора 10. В качестве блока 8 вычисления обратной величины удобно .использовать постоянное запоминающее устройство (ПЗУ). Операция дифференцирования выполняется следующим образом. Приращения дифференцируемой функ ЦИК JiU поступают на вход 1, приргицения аргумента & X поступают на вход 7. На вход 4 поступает сигнал запуска Пд, . От приращения 4Х отделяется m старших разрядов, которые поступа. ют на адресные входы постоянного запоминающего устройства (ПЗУ). Обозначим m старших разрядов приращения .Д X через & младшие разряды обозi начим -е . На входе ПЗУ 8 формируется величина-- -. Сигнал запуска открывает элементы И 2,15, на входы блока умножения через элементы ИЛИ 16,17 поступают величины АU и1/4Х, В блоке Is формируется первое прибли жение производной , Y - i ri; iX-e По завершении операции умножения сигнал запуска, задержанный элементом задержки 6, O jпереводит триггер 23 в единичное состояние; одновременно проходит через элемент ИЛИ 14 и открывает элементы И 19. Величина 1{| записывается в сумматор 21 предназначенн для накопления производной. .На этом заканчивается нулевой (подготовительный) ш.аг вычисления. Устройство переходит к выполнению первого шага. Триггер 23, переведенный в единичное состояние сигналом flg2 открывает элемент И 24 и . на вход счетчика 25 со входа 26 поступа ет главная тактовая серия. Сметчнк подсчитывает номера тактов и на выходах дешифратора формируются серии управляклчих сигналов П , Пу , П,П,. Сигнал П открывает элементы И 9,11 и на входы блока 18 поступают полноразрядное приращение. 4X со входа 7 и величина (J.,из сумматора 21. В блоке 18 формируется величина ,,.x.ijt-u. Сигнал открывает элементы И 3 И элементы И-НЕ 13. На входы сумматора 20 поступают приращение/ U и инверсия произведения ij аХ. В сумматоре 20 формируется величина К,(Ч ьхЬ&и-У,ьи . Сигнал Пт открывает элементы И 12,15 и на входы сомножителя через элементы ИЛИ 16,17 поступают величины R и --vS I гД® и перемножаются. Д л. Формируется приращение производной Y .J « . Сигнал П, открывает элементы И 19 и приращениеД4 поступает на вход сумматора 21, где складывается с величиной (ji . Формируется второе приближение производной , . Одновременно приращение l|t поступает в блок 22 сравнения, где сравнивается с допустимой погрешностью. На этом выполнение первого шага заканчивается. Бсли&()4|3 то выполняется следующий шаг вычислений. По сигналу Пг формируется в блоке 18 произведение По сигналу П в сумматоре 20 вычисляется значение 87euU4lA( По сигналу П 3 в блоке 18 формируется второе приращение 1 RI . .. 1 сигналу П формируется- третье приближение производной и одновременно величина Atjj сравнивается с допустимой погрешностью ft . Выполнение второго шага закончено. Уточнение производной продолжается до тех пор, пока не будет достигнута заданная точность. Как только.й1)Н , блок сравнения 22 переводит триггер 23 в нулевое состояние. Элемент И 24 закрывается счетчик 25 останавливается, генерироваиие сигналов П П П) П4 прекращается. Искомая, производная находится в су маторе 21. Покажем, что скорость сходимости указанного устройства окажется существенно выше сходимости прототипа. Нулевой шаг Ш ли dJC Погрешность нулевого шага 1.1 Iv l T Ixl4xUx-eV Первый шаг .v -, . , Iv «J uue i n ;d7r AUI7:e , Аналогичным образом находим д второго шага. .Ы .dx , 4xUX-e) и для - некоторого 1-го шага ,..v,vi.,,|,,(:. Величина IE представляет собой младшие разряды приращения л X. Приращения .Jk U и Л X удобно надеть мализованными, тогда 0 2аХ и , .Ли 2- , iX Л1-2- На практике о&лчно 2 мало, п . Если U/jK l, то кгикдый новый позволяет определить слеяуищие m вбриых разрядов. При й 16 для получения 16 верных разрядов изводйой достаточно всего два ша jijjh и - четыре шага и т Скорость сходимости предлагаемого устройства выше скорости сходимости прототипа при , как. минимум, в четыре раза. Если , то емкость ПЗУ составит 256 слов. Длина слова может составлять п разрядов. В этом случае величина -j представляется полноразрядным словом с погрешностью 2 . Однако.1ля сокргщения емкости ПЗУ удобно сокращать разрядную сетку величины /Л,, ограничивать ее К разрядами. Сокращение разрядной сетки не снижает заметно скорость сходимости процесса. При таком сокращении погрешность дифференцирования описывается следующими выражениями:. 1 1 4 е -к i rx-lfe z l -ufti ли е ,-к Е Слх) и так далее. Можно ограничить К 8-16 разрядами. Тогда ПЗУ может .быть выполнено в одной микросхеме (современный уровень. электроники позволяет получать ПЗУ емкостью 4-16 Кбит в корпусе). Следовательно, объем устройства увеличится незначительно, а (йлстродействие его возрастет существенно. При ис-. пользовании прототипа получение точности 0,0000001 потребовало бы более 30 шагов. Быстродействие устройства увеличивается в 10 раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1203552A1 |

| Устройство для решения дифференциальных уравнений | 1979 |

|

SU1023340A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Цифровой генератор функций | 1989 |

|

SU1656511A1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИ РОВАНИЯ, содержащее блок умножения, два сумматора, блок сравнения и элемент И, отличающееся тем, что, с целью повышения быстродействия, в него введены два элемента ИЛИ, две группы элементов ИЛИ, блок вычисления обратной величины, семь групп элементов И, элемент задержки, триггер, счетчик, дешифратор и группа элементовИ-НЕ, причем входы приращений подынтегральной функции устройства соединены с первыми входами элементов И первой и второй групп, выходы элементов И второй группы-соединены с входами первого слагаемого первого сумматора, вход запуска устройства соединен с nepBfcjMдвходом первого элемента ИЛИ и через элемент згшержки подключен к первому входу второго элемента ИЛИ и входу установки в единицу триггера, выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика, выходы которого соединены со входами дешифратора, первый выход которого подклю ен к первым входам .элементов И третьей и четвер1;ой групп, второй выход дешифратора соединен со вторыми входами элементов И второй группы и первыми входами Элементов И-НЕ группы, выходы которых соединены со входами второго слагаемого первого сумматора, выходы которого подключены к первым входам элементов И пятой группы, выходы которых соединены с первыми входами элементов ИЛИ первой группы, выходы которых соединены с входами первого сомножителя блока умножения, входы приращений аргумента устройства подключены ко вторым входам.элементов И третьей группы и входам блока вычисления обратной величины, выходы которого соединены с первыми входами элементов И шестой группы, выходы которых соединены с первыми входгили элементов ИЛИ второй группы, выходы которых подключены к входам второго сомножителя блока умножения, выходы которого соединены со вторыми входами элементов И-НЕ группы и первыми входами элементов И седьмой группы, выходы которых соединены со входами блока сравнения и второго сумматора, в выходы которого соединены со вторыМИ входами элементов И четвертой группы, выходы которых соединены со н : вторыми входами элементов ИЛИ первой: группы, третий выход дешифратора со-; единей со вторыми входами элементов ( И пятой группы и вторым входом I f первого элемента ИЛИ, выход которого| И шестой группы, четвертый выход дешифратору соединен со вторым вхрдом Ю второго элемента ИЛИ, выход которого подключен ко вторым входам элементов И седьмой группы, выход блока сравнения соединен с входом установки в ноль триггера, второй вход элемента И подключен к тактовому входу устройства, вход эапуска устройства соединен со вторыми входами элементов .,И первой группы, выходы которых соединены с третьими входами элементов ИЛИ первой группы, выходы элементов И третьей группы соединены ср вторыми входами элементовИЛИ второй группы.

| ,1 | |||

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 0 |

|

SU355631A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для дифференцирования | 1974 |

|

SU543000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-15—Публикация

1983-01-11—Подача