Изобретение относится к вычислительной технике и может быть использовано в аналогоцифровых вычислительных системах. Известны цифровые устройства для умножения чисел, поступающих в устройство параллельцым кодом, состоящие из цифровых блоков реализующих операции запоминания, сложения, сдвига и др 1. Недостаток этих устройств - большие аппаратурные затраты на организацию начала связи между устройствами. Наиболее близким к предлагаемому является множительное устройство, которое дает возможность вычислять однозарядные приращения произведения при поступлении на его вход одноразрядных приращений сомножителей, что fioзволяет по сравнению с цифровыми устройствами для умножения чисел, поступающих в устройство параллельным кодом, уменьшить затраты оборудования на организацию каналов связи с другими устройствами, т.е. упростить системную связь устройств. Например, вычислительная структура с составной частью известного устрой ства позволяет раййараллелить процесс вычислений и строить достаточно высокопроизводительные проблемно-ориентированные процессоры. В известном устройстве процесс умножения основан на приближенной формуле дифференциального исчисления Д(Х.) , в то время как формула точного дифференцирования учитывает и член высщего порядка малости й(Х.- а) У.-ДЧ- - -ДХ-«-йХ-Д Однако из-за отбрасывания величины ДХ-Д в нем происходит накопление погрещности по мере вычислений 2. Цепь изобретения - повыщение точности вычислений. Поставленная цель достигается тем, что множительнЬе устройство, содержащее счетчик первого сомножителя, счетчик второго сомножителя, блок умножения сомножителя на единичное приращение и накапливающий сумматор, вход каторого соединен с выходом блока умножешся сомножителя на едини шое приращение,

вход единичных приращений второго сомножителя множительного устройства соединен со входом счетчика второго сомножителя, отличающееся тем, что в него введены элемент задержки, коммутатор, два элемента ИЛИ, счетчик старших разрядов невязки и формирователь единичных приращений произведений, причем вход элемента задержки соединен со входом единичных приращений первого сомножителя множительного устройства, выход элемента задержки соединен со входом счетчика первого сомножителя и одним из входов первого элемента ИЛИ, другой вход которого соединен со входом счетчика второго сомножителя, а выход - соединен с первым входом блока умножения сомножителя на единичное приращение, входы второго коммзтатора соединены с выходами счетчиков первого и второг сомножителей, а выход соединен со вторым входом блока умножения сомножителя на едишгчное приращение, один вход второго элемента ИЛИ соединен с выходом переполнения накапливающего сумматора, другой вход соединен с выходом формирователя единичных приращений произведения, а выход соединен со входом счетчика старщих разрядов невязки, вход формирователя единичных приращений произведения соединен с выходом знакового разряда счетчика старщих разрядов невязки.

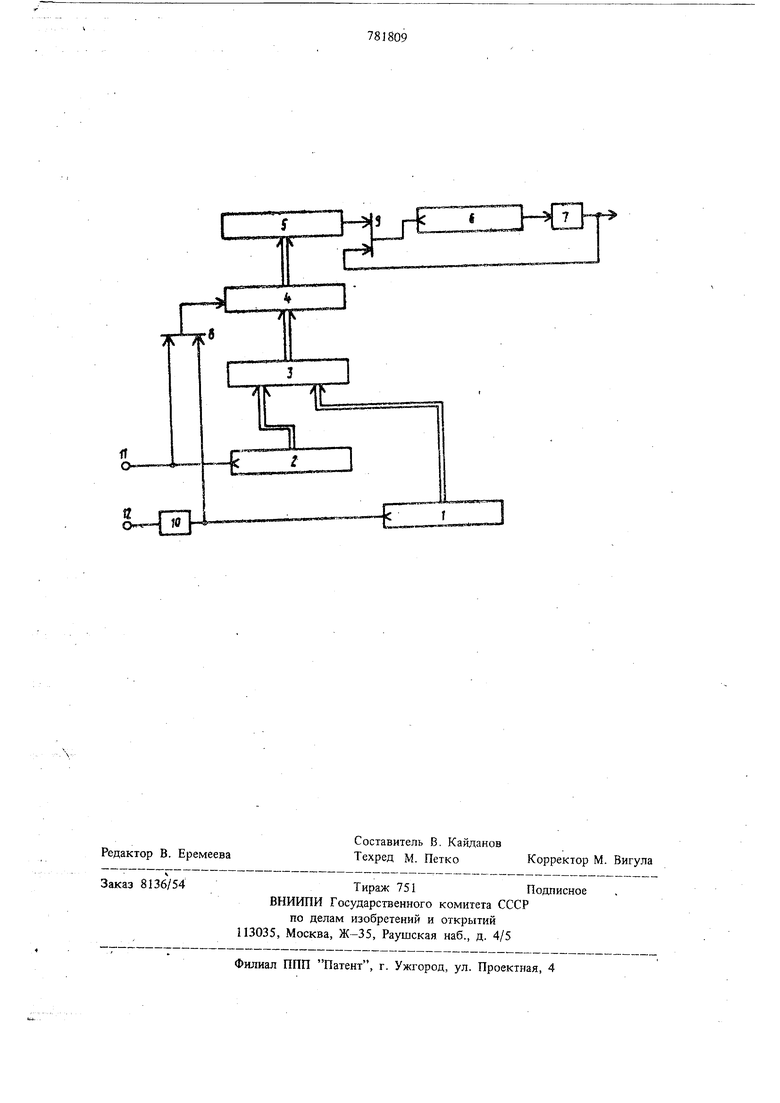

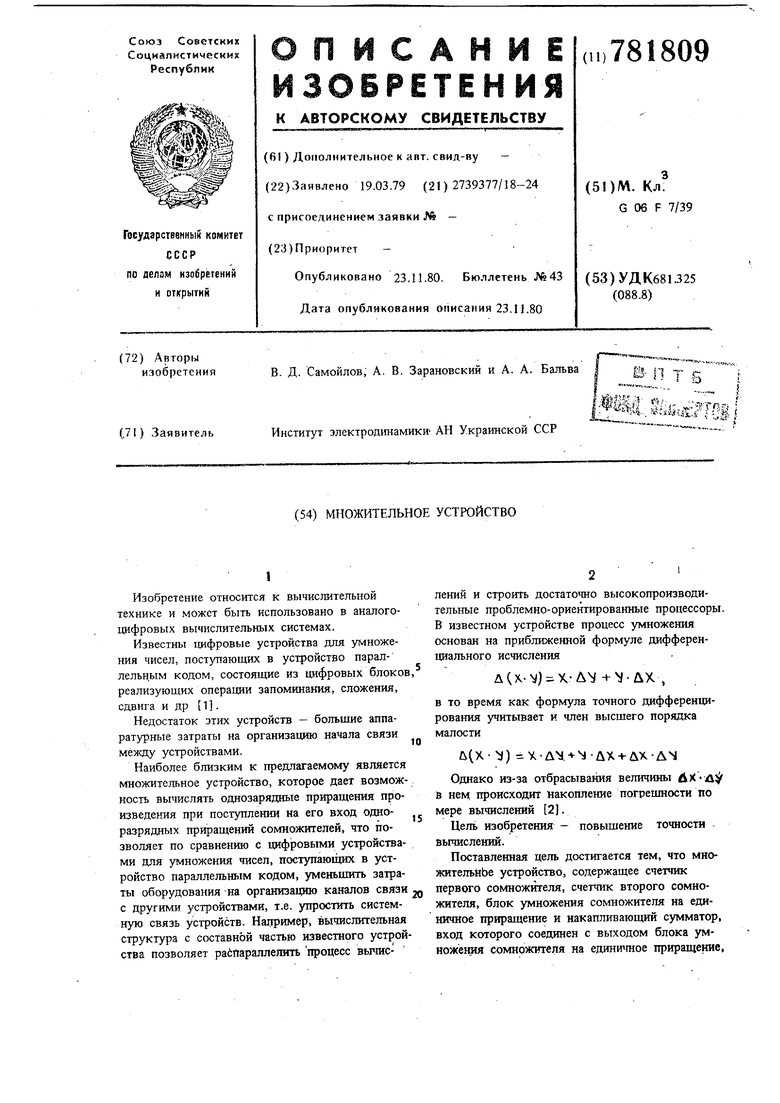

На чертеже изображена блок-схема устройств Устройство состоит из счетчика 1 первого сомножителя, счетчика 2 второго сомножителя, коммутатора 3, блока 4 умножения сомножителя на единичное приращение, накапливающего сумматора 5, счетчика 6 старших разрядов

невязки, формирователя 7 единичных приращений произведения, первого элемента ИЛИ 8, второго элемента ИЛИ 9, элемента 10 задержк

Вход элемента 10 задержки соединен со входом 12 единичных приращений первого

сомножителя, а выход - со входом счетчика 1 первого сомножителя и входом первого элемента ИЛИ 8. Вход 11 единичных приращений второго сомножителя соединен со входом счетчика второго сомножителя и другим входом первого элемента ИЛИ 8. Выход первого элемента ИЛИ 8 соединен с блоком 4 умножения сомножителя на единичное приращение. Выходы счетчиков первого и второго сомножителей соединены со входами коммутатора 3. Выход коммутатора 3 соединен со входом блока 4 умножения сомножителя на единичное приращение. Выход блока 4 умножения сомножителя, на единичное приращение соединен со входом накапливающего сумматора 5. Выход переполнения сумматора 5 соединен с одним из входов второго элемента ШШ 9, другой вход второго злемета ИЛИ 9 соединен с выхдом формирователя 7 единичных приращений

произведения. ВЬЕХОД второго элемента ИЛИ 9 соединен со входом счет1ика 6 старших разрядов невязки. Вход формирователя 7 единичных приращений произведения соединен со знаковым разрядом счетчика 6 старших разрядов невязки.

Устройство производит умножение в соответствии со следующей системой уравнений

.-dL-Sc ne (K)g(K-.),(k-.)(KL.g(M

(K)(k-i)U)

ч..

g(.)

Устройство работает следующим образом.

Перед началом вычисления счетчики и накапливающий сумматор устанавливаются в нулевое состояние. После этого одновременно поступают на вход устройства единичные приращения первого и второго сомножителей и вырабатывается единичное приращение произведения.

Подготовка устройства и выдача единичного приращения произведения производится за один цикл, который вьщолняется за два такта. На первом такте реализуются формулы (1), (2), и (3). На выходе формирователя 7 единичного приращения произведения появляется единичное приращение произведения д Z , знак его обратный знаку невязки €. ., поступающему на вход формирователя 7 единичного приращения произведения с выходом знакового разряда счетчика 6 старших разрядов невязки (производится вычисление по формуле (1)). Единичное приращение произведения поступает на вход второго элемента ИЛИ 9 и с его выхода на вход счетчика 6 старщих разрядов невязки. В счетчике 6 старших разрядов невязки и накапливающем коммутаторе 5 формируется величина

Ск-,)д(к)

На вход блока умножения сомножителя на единичное приращение через коммутатор 3 выдается содержимое счетчика первого сомножителя. С первого элемента ИЛИ 8 на вход блока 4 умножения сомножителя на единичное приращение поступает единичное приращение второго сомножителя и на выходе этой схемы формируется величина «ДХ . В накапливающем сумматоре 5 и счетчике 6 старши разрядов невязки производится вычисление величины

r(KLe(K.;.,(K-i.CK)(K) На вход счетчика 2 второго сомножителя поступает единичное приращение ДХ и формируется величина . После окончания переходных процессов в накапливающем сумматоре 5 и счетчике 6 стар ших разрядов невязки начинается второй такт, на котором реализуются формулы (4) и (5). С выхода элемента 10 задержки единичное приращение Д-а поступает на вход счетчика 1 первого сомножителя, где формируется величина гу tudа, через перв элемент ИЛИ 8 на вход блока 4 умножения сомножителя на единичное приращение. Величина X со счетчика второго сомножителя поступает через коммутатор 3 на вход блока 4 умножения сомножителя на единичное прираще ние, а с выхода зтого блока - на вход сумма тора 5. В накапливающем сумматоре 5 и счетчике в старщих разрядов невязки формиру ется величина (kL(K)(K)(K) Произведение двух сомножителей находится тогда, когда единичные приращения сомножителей и произведения после каждого цикла меня ют знак, т.е. когда в счетчиках сомножителей хранятся величины, равные задаваемым числам или меньшие на единичное приращение, а б после каждого цикла меняет знак. Величина произведения не хранится в устройстве, а равна алгебраической сумме приращений, выданны с выхода формирователя единичных приращени произведения в процессе работы. Устройство дает возможность получать произ ведение без накопления погрепшости по мере вычислений. Использование устройства целесообразно для построения блочных вычислительных структур больщим временем непрерывного моделирования процесса, где при больщом числе итераций не должно происходить накопление погрешности. Формула изобретения Множительное устройство, содержащее счетчик первого сомножителя, счетчик второго сомножителя, блок умножения сомножителя на единичное приращение и накапливающий сумматор, вход которого соединен с выходом блока умножения сомножителя на единичное приращение, вход единичных приращений второго сомножителя множительного устройства соединен со входом счетчика второго сомножителя, отличающееся тем, что, с целью повыщения точности, в него введены злемент задержки, коммутатор, два злемента ИЛИ, счетчик старщих разрядов невязки и формирователь единичных приращений произведений, причем вход злемента задержки соединен со входом единичных приращений первого сомножителя множительного устройства, выход элемента -задержки соединен со входом счетчика первого сомножителя и одним из входов первого злемента ИЛИ, другой вход которого соединен со входом счетчика второго сомножителя, а выход - соединен с первым входом блока умножения сомножителя на единичное приращение, входы коммутатора соединены с выходами счетчиков первого и второго сомножителей, а выход соединен со вторым .входом блока умножения сомножителя на единичное приращение, один вход второго элемента ИЛИ соединен с выходом переполнения накапливающего сумматора, другой вход соединен с выходом формирователя единичных приращений произведения, а выход соединен со входом счетчика старщих разрядов невязки, вход формирователя единичных приращений произйедения соединен с выходом знакового разряда счетчика старщих разрядов невязки. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 608157,кл. G 06 F 7/39, 1975. 2.Неслуховский К. С. Цифровые дифференциальные анализаторы. М., Мащиностроение, 1968, с. 90-91, рис. 23 (прототип).

LlIIHij --ir

сг:

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1979 |

|

SU781810A1 |

| Устройство для возведения в квадрат | 1979 |

|

SU894705A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1203552A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Множительное устройство | 1972 |

|

SU556433A1 |

Авторы

Даты

1980-11-23—Публикация

1979-03-19—Подача