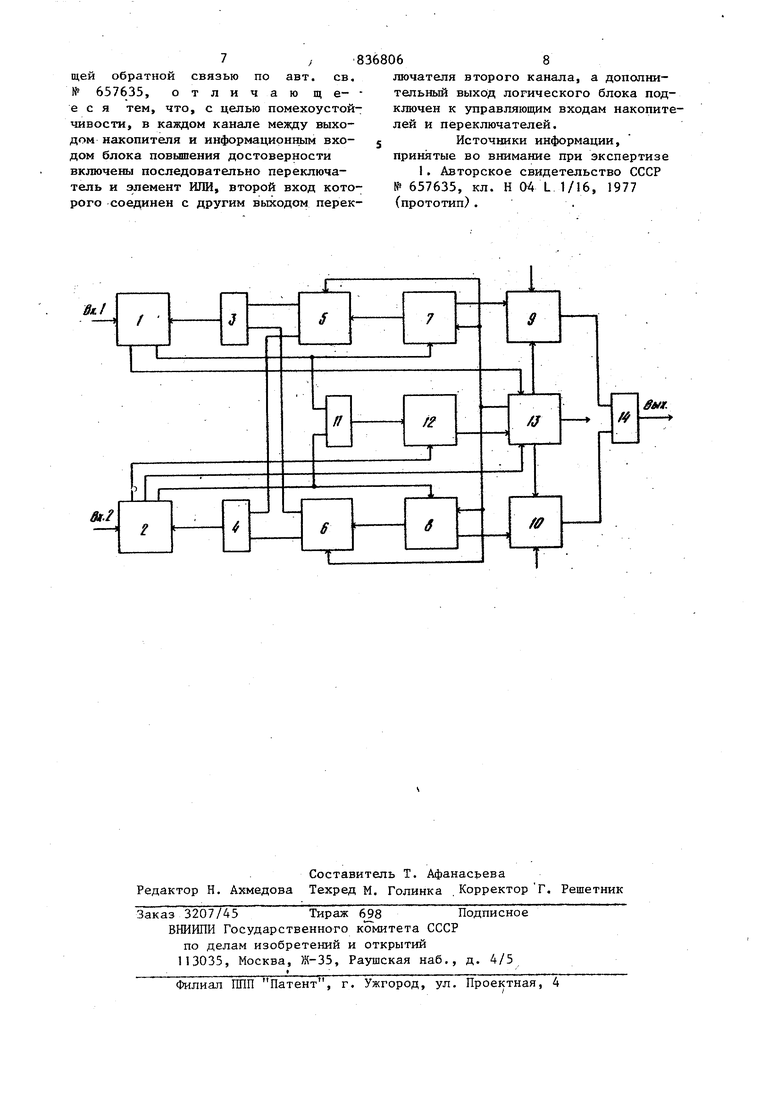

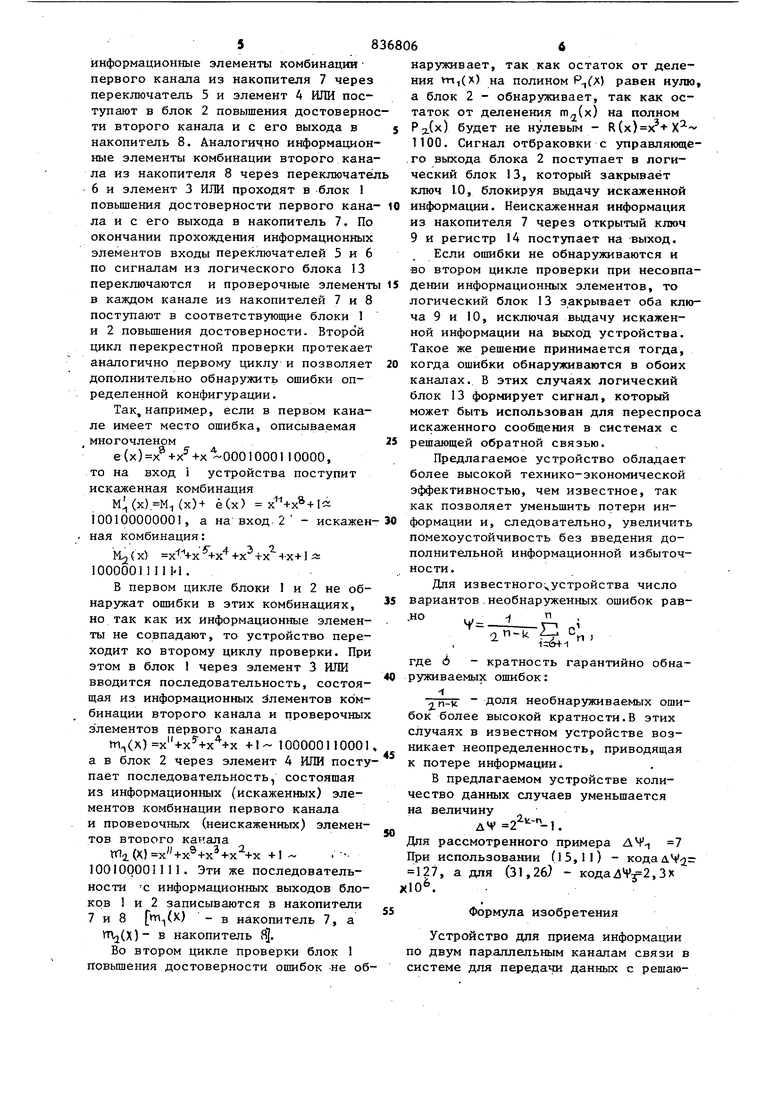

(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ ПО ДВУМ ПАРАЛЛЕЛЬНЫМ КАНАЛАМ СВЯЗИ В СИСТЕМЕ ДЛЯ ПЕРЕДАЧИ ДАННЫХ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ входы которых подключены к соответствующим входам логического блока и блока опроса несовпадений кодовых комбинаций, в каждом канапе между выходом накопителя и информационным входом блока повьшения достоверности включены последовательно переключатель и элемент ИЛИ, второй вход которого соединен с другим выходом переключателя канала, а дополнительный выход логического блока подключен к управлякядим входам накопителя и переключателей.На чертеже представлена структурная электрическая схема устройства для приема информации по двум парал- лельным каналам связи в системе для передачи данных с решаницей обратной связью. Устройство содержит блоки 1 и 2 повышения достоверности, элементы ИЛ 3 и 4, переключатели 5 и 6, накопите ли 7 и 8, ключи 9 и 10, сумматор по модулю два 11, блок 12 опроса несовпадений кодовых комбинаций, логический блок 13 и регистр 14 вьщачи инфо мации . 1 Блоки 1 и 2 повышения достовернос ти предназначены для анализа принима мых кодовых комбинаций на наличие ил отсутствие ошибок. В частном случае блок 1 представляет собой декодирующее устройство циклического (11,7)-кода с образующи полиномом Р (х) х +Х+1, а блок 2 с образующим полиномом Р2.() . Если комбинация безызбыточного кода С(х), то комбинация (11,7)- кода первого канала будет Mi(x) 100000110001, а комбинация (11,7)- кЬда второго канала +х н-х Мд X х +Х- +х +х100000111111. Таким образом, информационные эле менты этих комбинаций совпадают (оди наковые)., а проверочные - различные Элементы 3 и 4 ИЛИ и переключате ли 5 и 6 принимают участие в перекрестной проверке кодовых комбинаций первого и второго каналов. Накопите ли 7 и 8 предназначены для записи и хранения кодовых комбинаций перво и второго каналов. Через ключи 9 и и регистр 14 принятая и проверенная информация выдается на выход устрой ства. Сумматор 11 по модулю два осу ществляет поразрядное сравнение одноименных элементов комбинации обоих каналов. Блок 12 опроса обеспечивает формирование сигнала несовпадения информационных элементов сравниваемых комбинаций по окончании цикла проверки. Логический блок 13 осуществляет функции управления. Работает устройство следующим образом. Элементы кодовых комбинаций поступают в блоки 1 и 2 повьшения достоверности. Одновременно с обработкой в блоках I и 2 элементы комбинаций записываются в накопители 7 и 8 и сравниваются на сумматоре И по модулю два. Результат сравнения информационных элементов комбинаций, принятых по обоим каналам, учитывается только в тех случаях, когда с управляющих выходов блоков 1 и 2 не поступают сигналы отбраковки данной комбинации. При поступлении по обоим каналам связи информации без ошибок будут отсутствовать сигналы отбраковки из блоков 1 и 2 повышения достоверности и сигнал несовпадения из блока 12 опроса. В этом случае информация из накопителей 7 и 8 через открытые ключи 9 и 10 и регистр 14 выдается на выход устройства. При поступлении информации без обнаруживаемых ошибок по первому каналу и обнаружении ошибок блоком 2 второго канала, последний формирует сигнал отбраковки в логический блок 13, который независимо от результата сравнения кодовых комбинаций закрывает ключ 10, блокируя выдачу искаженной информации. На выход устройства через открытый ключ 9 и регистр 14 проходит информация из накопителя 7 пер- вого канала. Устройство работает аналогично и тогда, когда ошибки не обнаруживаются во втором канале и обнаруживаются в первом канале. В этом случае закрывается ключ 9 и остается открытым ключ 10, через который информационные элементы комбинации второго канала вьщаются на выход. Если ошибки не обнаруживаются в обоих каналах, но информационные эле менты сраниваемых комбинаций не совпадают, то блок 12 опроса формирует сигнал несовпадения в логический блок 13, который выдает сигналы на управлякицие входы накопителей 7 и 8 и переключателей 5 и 6. В этом случае 58 информациошше элементы комбинации первого канала из накопителя 7 через переключатель 5 и элемент 4 ИЛИ поступают в блок 2 повышения достовернос ти второго канала и с его выхода в накопитель 8. Аналогично информационные элементы комбинации второго канала из накопителя 8 через переключател 6 и элемент 3 ИЛИ проходят в блок 1 повышения достоверности первого канала и с его выхода в накопитель 7. По окончании прохождения информационных элементов входы переключателей 5 и 6 по сигналам из логического блока 13 переключаются и проверочные элементы 15 В каждом канале из накопителей 7 и 8 поступают в соответствующие блоки 1 и 2 повышения достоверности. Второй цикл перекрестной проверки протекает аналогично первому циклу и позволяет дополнительно обнаружить ошибки определенной конфигурации. Так, например, если в первом канале имеет место ошибка, описываемая многочленом е(х) 5-00010001 10000, то на вход 1 устройства поступит искаженная комбинация м,(х)М (x)- ё(х) х ч-х +1 ; iOOIOOOOOOOl, а на вход 2 - искажен ная комбинация: К, (х) +х +х тх 1 л 1000001 111 . В первом цикле блоки 1 и 2 не обнаружат ошибки в этих комбинациях, но так как их информационные элементы не совпадают, то устройство переходит ко второму циклу проверки. При этом в блок 1 через элемент 3 ИЛИ вводится последовательность, состоящая из информационных Элементов комбинации второго канала и проверочных элементов первого канала т(х) +1- 100000110001 а в блок 2 через элемент 4 ИЛИ посту пает последовательность, состоящая из информационных (искаженных) элементов комбинации первого канала и проверочных (неискаженных) элементов втооого канала т2.(Х)х +х®+х +х +х +1 100100001111. Эти же последовательности -с информационных выходов блоков 1 и 2 записываются в накопители 7 и 8 Т1(Х) - в накопитель 7, а УТ1(Х)- в накопитель В. Во втором цикле проверки блок 1 повьш1ения достоверности ошибок -не об 6 наруживает, так как остаток от деления vn,(x) на полином ) равен нулю, а блок 2 - обнаруживает, так как остаток от деленения m(x) на полном - У-Ч / j(.. ) будет не нулевым - R(x)x Х 1100, Сигнал отбраковки с управляющего выхода блока 2 поступает в логический блок 13, который закрывает ключ 10, блокируя вьщачу искаженной информации. Неискаженная информация из накопителя 7 через открытый ключ 9 и регистр 14 поступает на выход. Если ошибки не обнаруживаются и во втором цикле проверки при несовпадении информационных элементов, то логический блок 13 закрывает оба ключа 9 и 10, исключая выдачу искаженной информации на выход устройства. Такое же решение принимается тогда, когда ошибки обнаруживаются в обоих каналах. В этих случаях логический блок 13 формирует сигнал, который может быть использован для переспроса искаженного сообщения в системах с решающей обратной связью. Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное, так как позволяет уменьшить потери информации и, следовательно, увеличить помехоустойчивость без введения дополнительной информационной избыточности. Для известного; устройства число вариантов.необнаруженных ошибок равно , , -1 . где 6 - кратность гарантийно обнаруживаемых ошибок: f - доля необнаруживаемых ошибок более высокой кратности.В этих случаях в известном устройстве возникает неопределенность, приводящая к потере информации. В предлагаемом устройстве количество данных случаев уменьшается на величину . дН Дпя рассмотренного примера AV-, 7 При использовании (15,11) - кодадУ г 127, а для (31,26) - кода4Н 2,Зх 10. Формула изобретения Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью по авт. № 657635, о тли ч а ю щ е с я тем, что, с целью помехоустойчивости, в каждом канале между выходом накопителя и информационным входом блока повышения достоверности включены последовательно переключатель и элемент ИЛИ, второй вход которого соединен с другим выходом перек86 лючателя второго канала, а дополнительный выход логического блока подключен к управляющим входам накопителей и переключателей. Источиики информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 657635, кл. Н 04 L 1/16, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решаюшей обратной связью | 1977 |

|

SU657635A2 |

| УСТРОЙСТВО СИНХРОННОГО ПРИЕМА ДВОИЧНОЙ ИНФОРМАЦИИ ПО ДУБЛИРУЮЩИМ КАНАЛАМ СВЯЗИ | 2012 |

|

RU2528089C2 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для защиты от ошибок в системе передачи с решающей обратной связью | 1976 |

|

SU728153A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

1- Змх.

Авторы

Даты

1981-06-07—Публикация

1979-07-24—Подача