(54) ФОРМИРОВАТЕЛЬ СЕРИИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь серии импульсов | 1978 |

|

SU783957A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Имитатор радиосигналов | 1983 |

|

SU1107155A1 |

| Фазовращатель дискретного действия | 1981 |

|

SU1005272A1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Устройство для преобразования двоичного кода во временной интервал | 1986 |

|

SU1363475A1 |

| Многоканальный формирователь серии импульсов | 1980 |

|

SU932601A1 |

1

Изобретение относится к импульсной технике и может быть использовано в радионавигационных и радиолокационных индикаторах для формирования периодических последовательностей импульсов с высокоточными временными интервалами.

Известен формирователь серии импульсов, содержащий преобразователь последовательного кода в параллельный программный блок и блок сравнения 1.

Однако указанный формирователь серии импульсов обладает большими переходными процессами, соизмеримыми с периодом частоты генератора опорной частоты, что приводит к понижению точности.

Наиболее близким техническим решением к данному изобретению является формирователь серии импульсов, содержащий генератор опорной частоты, программный блок, преобразователь код-временной интервал и многоразрядный блок совпадения 2.

Недостатком известного формирователя серии импульсов является низкое быстродействие.

С целью повышения быстродействия в формирователь серии импульсов, содержащий генератор опорной частоты, программный блок и преобразователь код-в,ременной интервал, управляющие входы которого соединены с выходами старших разрядов программного блока, дополнительно введены преобразователь параллельного кода в последовательный и делитель-фазоосдвигатель, первый вход которого подключен к выходу генератора опорной частоты, а выход делителя - фазосдвигателя соединен с синхронизирующим входом преобразователя кодвременной интервал, причем выходы младших разрядов программного блока соединены соответственно с входами преобразователя параллельного кода в последовательный, первый и второй выходы которого соединены соответственно с вторым и третьим

входом делителя-фазосдвигателя.

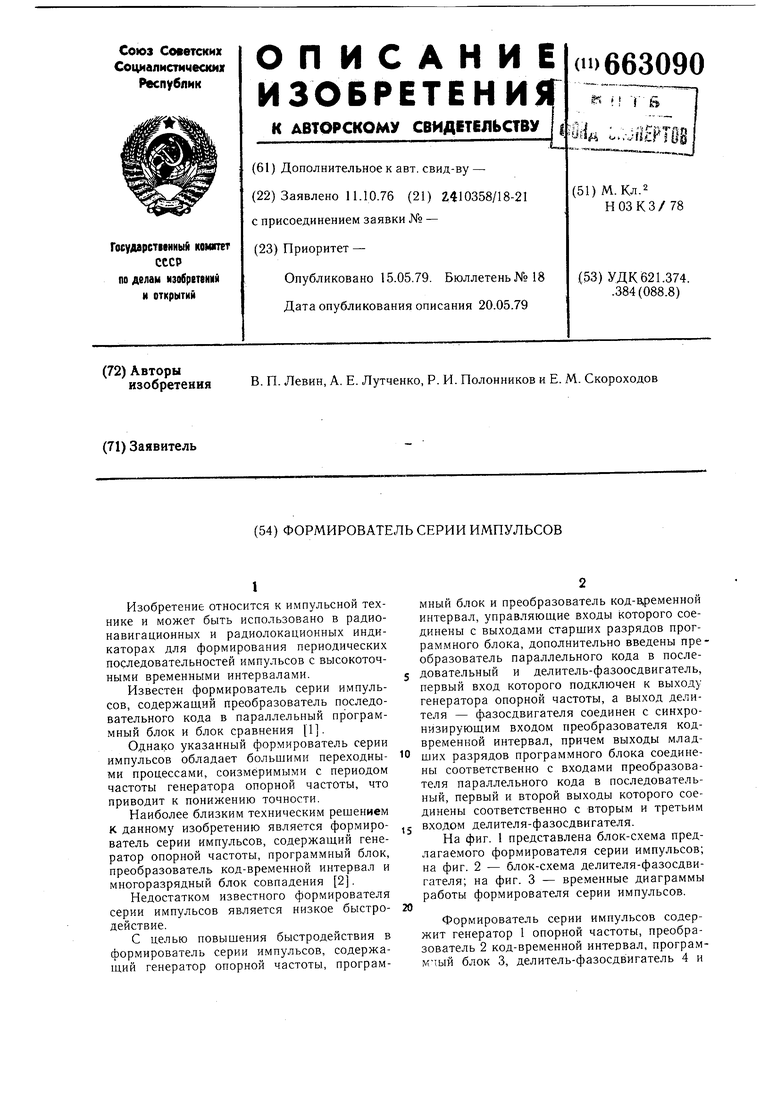

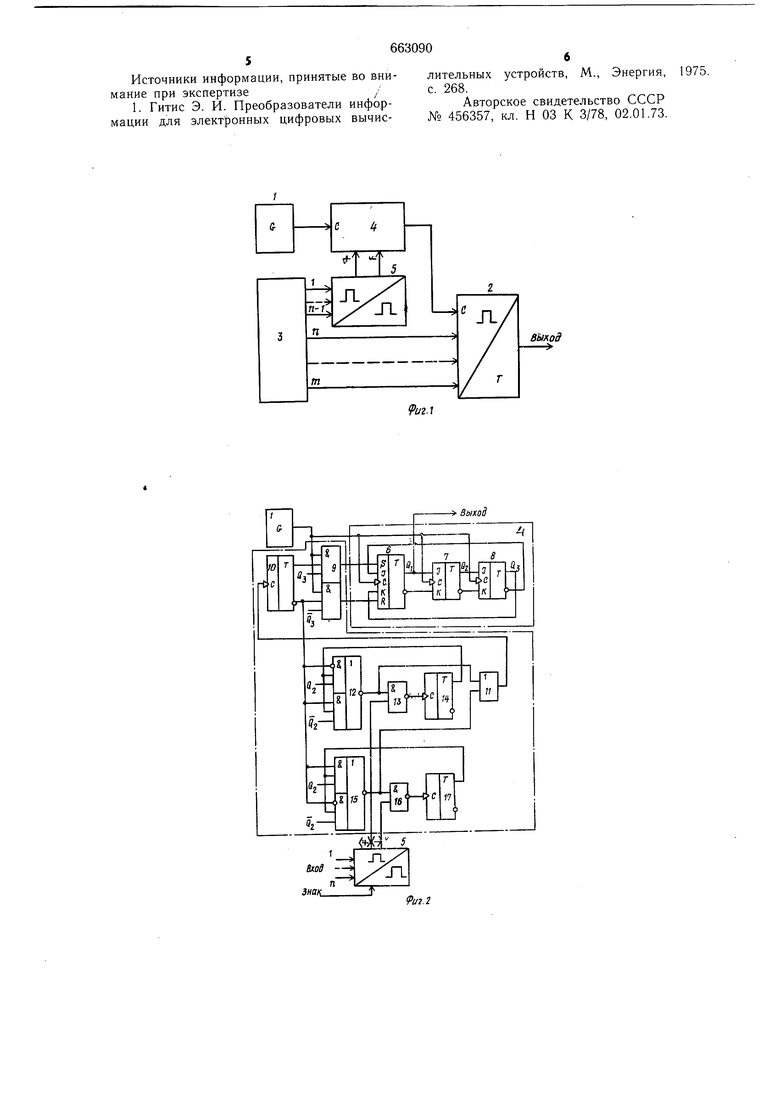

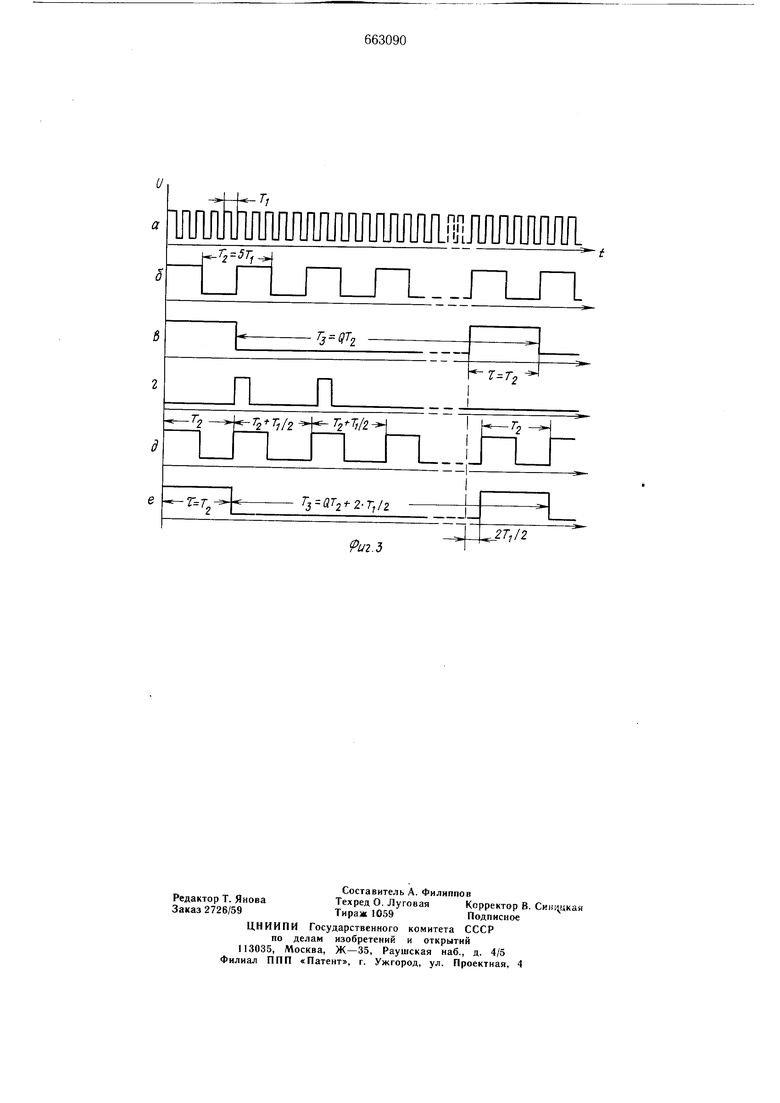

На фиг. 1 представлена блок-схема предлагаемого формирователя серии импульсов; на фиг. 2 - блок-схема делителя-фазосдвигателя; на фиг. 3 - временные диаграммы работы формирователя серии импульсов.

Формирователь серии импульсов содержит генератор 1 опорной частоты, преобразователь 2 код-временной интервал, программный блок 3, делитель-фазосдвигатель 4 и преобразователь 5 параллельного кода в последовательный код. Делитель-фазосдвигатель содержит кольцевой счетчик, включающий в себя первый триггер 6, второй триггер 7, третий триггер 8 и обратные связи по S и R-входам первого триггера 6, осуществляемые через элемент И 9, четвертый триггер 10, элемент ИЛИ 11, блок формирования управляющих импульсов положительного сдвига фазы выходных сигналов, состоящей из элемента И-НЕ 12, элемента И-НЕ 13 и пятого триггер 14, и блок формирования управляющих импульсов отрицательного сдвига фазы, состоящей из элемента И-НЕ 15, элемента И-НЕ 16 и щестого триггера 17. Формирователь серии импульсов работает следующим образом. На синхронизирующий вход делителяфазосдвигателя 4 (фиг. 1) с выхода генератора 1 поступает периодическая последовательность прямоугольных импульсов типа «.меандр, и.меющая период Т, (эпюра а, фиг. 3). При отсутствии сигналов на управляющих входах преобразователя 5 параллельного кода в последовательный код на выходе делителя-фазосдвигателя 4 формируется последовательность прямоугольных импульсов с периодом Тг рТ (эпюра б, фиг. 3), где р - коэффициент пересчета счетчика делителя-фазосдвигателя 4. Конкретное значение р выбирается с учетом быстродействия логических элементов, которые используются в преобразователе 2 код - временной интервал, и должно быть таким, чтобы период выходных и.мпульсов был значительно больще задержки сигналов в цепях этого устройства. В данном случае . Такой коэффициент пересчета обеспечивается за счет действия обратной связи между выходами третьего триггера счетчика (фиг.2) и S или R - входами первого триггера 1. В этом режиме работы при записи в счетчики преобразователя 2 код - временной интервал кода числа А через период Тз АТл на выходе формирователя вырабатывается импульс с длительностью t Тг. Таки.м образом можно изменять периоды между импульсами с дискретом Тг, за счет изменения кодовых комбинаций сигналов на группе выходов старщих разрядов программного блока 3. Установка очередного периода между импульсами в серии с меньшим дискретом, чем период Tj,, производится за счет сдвига фазы сигналов на выходе делителя-фазосдвигателя 4. Для этого на управляющие входы преобразователя 5 параллельного кода в последовательный код поступает, например, код числа 2 со знаком + . Преобразователь 5 параллельного кода в последовательный код перекодирует параллельный код числа 2 в последовательный код в сигнал, содержащий на щине + два последовательных импульса (эпюра г, фиг. 3). Первым импульсом из этой последовательности через элемент И-НЕ 13 пя тый триггер 14 устанавливается в единичное состояние, в результате элемент И-НЕ 12 в одном из временных интервалов при Q 1 или Q 1 (в зависимости от состояния четвертого триггера 10) формирует короткий по длительности импульс, которым пятый триггер 14 устанавливается в исходное состояние, а четвертый триггер 10 - в противоположное состояние. В этот момент переключается действие обратной связи у первого триггера 6 с S - входа на R - вход или наоборот. В результате изменяется коэффициент пересчета счетчика с р 6 на р 5,5 и фаза сигнала на выходе делителя-фазосдвигателя 4 сдвигается на 0,5 Т i. По аналогии под воздействием следующего импульса фаза выходного- сигнала еще раз сдвигается на + 0,5 Tt. В результате период выходных импульсов увеличивается на 2«0,5 TI (эпюры д и е, фиг. 3). В случае отрицательного знака числа 2 сигналы единичного кода появляются на щине - период выходных и.мпульсов уменьшается на упомянутую выще величину. Таким образом, варьирование знаком и числом на управляющих входах преобразователя 5 параллельного кода в последовательный код изменяет периоды формируе.мых импульсов как в сторону их увеличения, так и в сторону уменьшения относительно периода Тг с дискретом 0,5 Ti. Число дискретов можно изменять от 1 до 9, не изменяя при этом кода числа на входах старших разрядов преобразователя код-временной интервал. Формула изобретения Формирователь серии и.мпульсов, содержащий генератор опорной частоты, программный блок и преобразователь код-временной, интервал, управляющие входы которого соединены с выходами старших разрядов программного блока, отличающийся тем, что с целью повышения быстродействия, в него дополнительно введены преобразователь, параллельного кода в последовательный и делитель-фазосдвигатель, первый вход которого подключен к выходу генератора опорной частоты, а выход делителя-фазосдвигателя соединен с синхронизирующим входом преобразователя код-временной интервал, причем выходы младших разрядов программного блока соединены соответственно с входами преобразователя параллельного кода в последовательный, первый и второй выходы которого соединены соответственно с вторым и третьим входом делителя-фазосдвигателя. 56

Источники информации, принятые во вни-лительных устройств, М., Энергия, 1975.

мание при экспертизе/с. 268.

мации для электронных цифровых вычис-№ 456357, кл. Н 03 К 3/78, 02.01.73.

Знак

663090

Выкод

BbixoS

Й/г.2

1ШШШ11Ш111ШЛ 1ШМ|||1Л11ШШЖ

а

лп

Ti Vf-T T.lz

rj(7-2f-2-r,/2

-Г

|

7/2

Риг.Ъ

Авторы

Даты

1979-05-15—Публикация

1976-10-11—Подача