Изобретение относится к импульсной технике и может быть использовано в информационно-измерительных вычислительных системах.

Цель изобретения - повышение точности устройства.

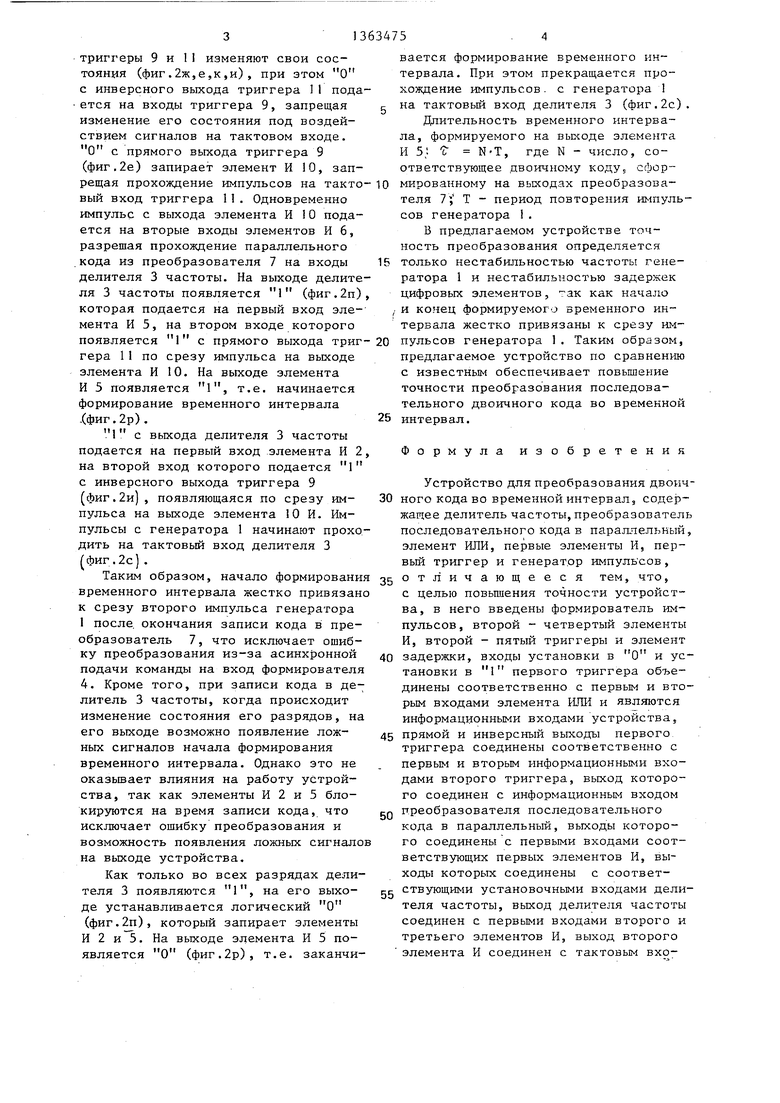

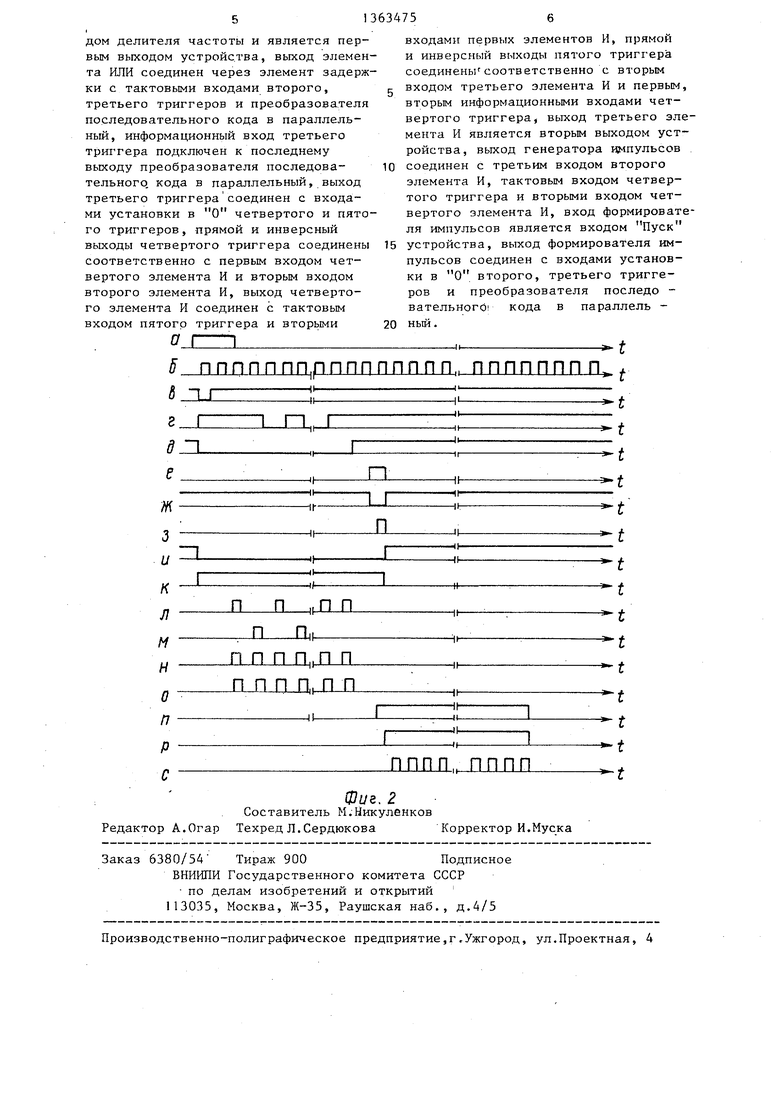

На фиг.1показана функциональная схема устройства для преобразования двоичного кода во временной интервал; на .фиг.2 - временные диаграммы поясняющие его работу.

Устройство для преобразования двоичного кода- во временной интервал содержит {фиг.1) генератор 1 импульсов, второй элемент И 2, делитель 3 частоты, формирователь 4 импульсов, третий 5 и первые 6.1-б.п элементь И, преобразователь 7 последовательного кода в параллельньй, третий 8 и четвертый 9 триггеры, четвертый элемент-И 10, пятый триггер 11 и преобразователь 12 двоичного биимпульсного кода в двоичный код, вьшолненный на первом 13 и втором 14 триггерах, элементе ИЛИ 15 и элементе 16 задержки.

Устройство работает следующим обр1азом.

На вход формирователя 4 подается команда (фиг.2а) в виде уровня 1 произвольной длительности. На выходе формирователя 4 появляется импульс (фиг.2в), осуществляющий сброс триггеров 8 и 14. На инверсном выходе триггера 14 появляется уровень а на выходе триггера 8 - О (фиг.2 г,д). О с выхода триггера 8 подается на R-входы триггеров 9 и 11, устанавливая их в нулевое состояние (фиг.2 е,ж,и,к). Уровень 1 с инверсного выхода триггера 9 подается на второй вход элемента И 2. Уровень О с выхода триггера 1 1 (фиг.2к) блокирует элемент И 5 (фиг.2р) на время записи кода.

После подачи команды на вход формирователя 4 производится запись (п+1)-разрядного импульсного последовательного двоичного кода (п - число разрядов- преобразователя 7 последовательного кода в параллельный). Код подается старшими разрядами вперед, причем в старших разрядах содержится преобразуемьш код , а младший разряд произвольный.

Код для преобразования подается на информационные входы устройства

по двум линиям в виде прямого и инверсного кодов, причем единица в коде соответствует наличию импульса на линии прямого кода и отсутствию импульса на линии инверсного кода, нуль - отсутствию импульса на линии прямого кода и наличию импульса на линии инверсного кода (фиг.2 л,

м). Эти импульсы подаются соответственно на R- и S-входы триггера 13 и входы элемента ИЖ 15. На выходе последнего формируется пачка импульсов записи (фиг.2н), а на

прямом и инверсном выходах триггера 1 3 - соответственно обратный и прямой коды, причем длительность импульсов кода расширена до периода повторения импульсов пачки. Разряды обратного и прямого кодов подаются соответственно на I- и К-входы триггера 14. Пачка импульсов .записи через элемент 16 задержки (фиг.2о) подается на тактовые входы триггеров

8 и 14 и на тактовый вход преобразователя 7 последовательного кода в параллельный, причем задержка импульсов обеспечивает надежную запись кода в преобразователь 7. На инверсном выходе триггера 14 формируются разряды прямого кода (фиг.2г), которые последовательно подаются на информационный вход преобразовате- ля 7.

По мере записи разрядов кода в преобразователь 7 1, которая была первоначально на инверсном выходе триггера 14, перемещается от первого к последнему разряду преобразователя

7. Как только в преобразователь 7 запишутся все п+1 разряды кода, 1 из старшего разряда преобразователя 7 переписьшаются в триггер 8 и с выхода триггера 8 (фиг.2д) подается

на R-входы триггеров 9 и 11, разрешая изменение их состояния под воздействием сигналов на других входах. Первый импульс с выхода генератора I после появления 1 на выхо- де триггера 8 изменяет состояние триггера 9 (фиг.2ж,е), так как на его I- и К-входах присутствует 1. О с инверсного выхода триггера I1 (фиг.2ж) блокирует элемент 2 И.

Второй импульс с генератора I проходит через элемент И 1 О (фиг.2д), открытый уровнем 1 с прямого выхода триггера 9, на счетный вход триггера 11. По срезу этого импульса

триггеры 9 и 11 изменяют свои состояния (фиг.2ж,е,к,и), при этом О с инверсного выхода триггера 11 подается на входы триггера 9, запрещая изменение его состояния под воздействием сигналов на тактовом входе. О с прямого выхода триггера 9 (фиг,2е) запирает элемент И 10, запрещая прохождение импульсов на такто- Ю мированному на выходах преобразова

вый вход триггера 11. Одновременно импульс с выхода элемента И IО подается на вторые входы элементов И 6, разрешая прохождение параллельного кода из преобразователя 7 на входы делителя 3 частоты. На выходе делителя 3 частоты появляется 1 (фиг.2п) которая подается на первый вход элемента И 5, на втором входе которого появляется 1 с прямого выхода триггера 1 1 по срезу импульса на вьпсоде элемента И 10. На выходе элемента И 5 появляется 1, т.е. начинается формирование временного интервала .(фиг. 2р) .

1 с выхода делителя 3 частоты подается на первый вход элемента И 2 на второй вход которого подается 1 с инверсного выхода триггера 9 (фиг.2и), появляющаяся по срезу импульса на выходе элемента 0 И. Импульсы с генератора 1 начинают проходить на тактовый вход делителя 3 (фиг.2с).

Таким образом, начало формировани временного интервала жестко привязан к срезу второго импульса генератора 1 после, окончания записи кода в преобразователь 7, что исключает ошибку преобразования из-за асинхронной подачи команды на вход формирователя 4. Кроме того, при записи кода в делитель 3 частоты, когда происходит изменение состояния его разрядов, на его выходе возможно появление ложных сигналов начала формирования временного интервала. Однако это не оказьшает влияния на работу устройства, так как элементы И 2 и 5 бло- кирзпотся на время записи кода, что исключает ошибку преобразования и возможность появления ложных сигнало на выходе устройства.

Как только во всех разрядах делителя 3 появляются 1, на его выходе устанавливается логический О (фиг.2п), который запирает элементы И 2 и 5. На выходе элемента И 5 появляется О (фиг.2р), т.е. заканчи

вается формирование временного интервала. При этом прекращается прохождение импульсов, с генератора 1 на тактовый вход делителя 3 (фиг.2с).

Длительность временного интервала, формируемого на выходе элемента И 5; S N T, где N - число, соответствующее двоичному коду, сфор

теля 7V Т - период повторения импульсов генератора 1.

В предлагаемом устройстве точность преобразования определяется только нестабильностью частоты генератора 1 и нестабильностью задержек цифровых элементов, так как начало и конец формируемого временного интервала жестко привязаны к срезу импульсов генератора 1. Таким образом, предлагаемое устройство по сравнению с известным обеспечивает повьшение точности преобразования последовательного двоичного кода во временной интервал.

Формула изобретения

0

Устройство для преобразования двоичного кода во временной интервал, содер- делитель частоты, преобразователь последовательного кода в параллельный, элемент ИЛИ, первые элементы И, первый триггер и генератор импуль сов , отличающееся тем, что, с целью повьшения точности устройства, в него введены формирователь импульсов, второй - четвертый элементы И, второй - пятый триггеры и элемент задержки, входы установки в О и установки в 1 первого триггера объединены соответственно с первым и вторым входами элемента HJDi и являются информационными входами устройства, 5 прямой и инверсный выходы первого триггера соединены соответственно с первым и вторым информационными входами второго триггера, выход которого соединен с информационным входом преобразователя последовательного кода в параллельный, выходы которого соединены с первыми входами соответствующих первых элементов И, выходы которых соединены с соответствующими установочными входами делителя частоты, выход делителя частоты соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с тактовым вхо0

0

5

дом делителя частоты и является первым выходом устройства, выход элемента ИЛИ соединен через элемент задержки с тактовыми входами второго, третьего триггеров и преобразователя последовательного кода в параллельный, информационный вход третьего триггера подключен к последнему выходу преобразователя последовательного, кода в параллельный, выход третьего триггера соединен с входами установки в О четвертого и пятого триггеров, прямой и инверсный выходы четвертого триггера соединены соответственно с первым входом четвертого элемента И и вторым входом второго элемента И, выход четвертого элемента И соединен с тактовым входом пятого триггера и вторьгми

а

входами первых элементов И, п и инверсный выходы пятого три соединены соответственно с вт

с входом третьего элемента И и вторым информационными входам вертого триггера, выход треть мента И является вторым выход ройства, выход генератора чмп

10 соединен с третьим входом вто элемента И, тактовым входом ч того триггера и вторыми входо вертого элемента И, вход форм ля импульсов является входом

15 устройства, выход формировате пульсов соединен с входами ус ки в О второго, третьего тр ров и преобразователя посл вательногО кода в паралле ный.

LT

1 П„ Г

±

20

t

5 ппппппп,рпппппппп,, пппппппп и

dJ. е

т

5 и

к л и н

о п

Р с

Фие. 2

Составитель М.Ыикуленков

Редактор А.Огар Техред Л.Сердюкова

Заказ 6380/54 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г,Ужгород, ул.Проектная, 4

634756

входами первых элементов И, прямой и инверсный выходы пятого триггера соединены соответственно с вторым

с входом третьего элемента И и первым, вторым информационными входами четвертого триггера, выход третьего элемента И является вторым выходом устройства, выход генератора чмпульсов

10 соединен с третьим входом второго элемента И, тактовым входом четвертого триггера и вторыми входом четвертого элемента И, вход формирователя импульсов является входом Пуск

15 устройства, выход формирователя импульсов соединен с входами установки в О второго, третьего триггеров и преобразователя последо - вательногО кода в параллель - ный.

20

±

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Преобразователь двоичного кода во временной интервал | 1987 |

|

SU1453597A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Преобразователь двоичного кода во временной интервал | 1986 |

|

SU1376243A1 |

Изобретение относится к импульсной технике и предназначено для преобразования двоичного кода во временной интервал. Изобретение позволяет повысить точность устройства. Входной последовательный код записьюается в преобразователь 7 и поступает на установочные входы делителя 3, на выходе элемента И 5 формируется импульс, длительность которого пропорциональна числу, записанному в двоичном коде. Устройство содержит генератор 1 импульсов, элементы .И 2,5,6,10, делитель 3 частоты, формирователь 4 импульсов, преобразователь 7 последовательного кода в параллельный, триггеры 8,9, 11,13,14, элемент ШШ 15 и элемент задержки 16. 2 ил. (Л со О5 00 4 СП

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника: Справочное руководство | |||

| -М.: Мир, 1983, с.361, рис.20.31 | |||

| Преобразователь двоичного кода вовременной интервал | 1974 |

|

SU508927A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-17—Подача