I

Изобретение относится к импульсной технике и может быть использовано в цифровой аппаратуре для формирования периодических последовательностей пачек импульсов.

Известен формирователь серии импульсов с программным управлением по основному авт. св. № 663090, содержащий опорный генератор, блок программ, преобразователь код-временной интервал и делитель-фазосдвигатель lj .

Недостатком известнЪго устройства является низкое быстродействие, которое ограничивается временем формирования и передачи кодов из блока программ в преобразователь код-временной интервал.

Целью изобретения является повышение быстродействия формирователя.

Указанная цель достигается тем, что в формирователь серии импульсов с программным управлением, содержа щий опорный генератор, блок программ, преобразователь код-временной интервал и делитель-фазосдвигатель, выход которого соединен с С-входом преобраэоВате/1я код-временнойинтервал, управляющие входы которого поразрядно соединены с выходами старших разрядов блока программ, выходы младших разрядов которого подключены к управляющим входам делителя-фазосдвигателя,синхронизирующий вход которого соёдйнен с выходом опорного генератора, а V5 вход блока программ соединен с V-BXOдом и выходом п|реобразова еля кодвременной интервал, введен ждущий элемент задержки, управляющие входы которого поразрядно соединены с выхоtS дами средних разрядов блока программ, а V- и С-входы ждущего элемента задержки соединены соответственно с V и С-входами преобразователя код-временной интервал,

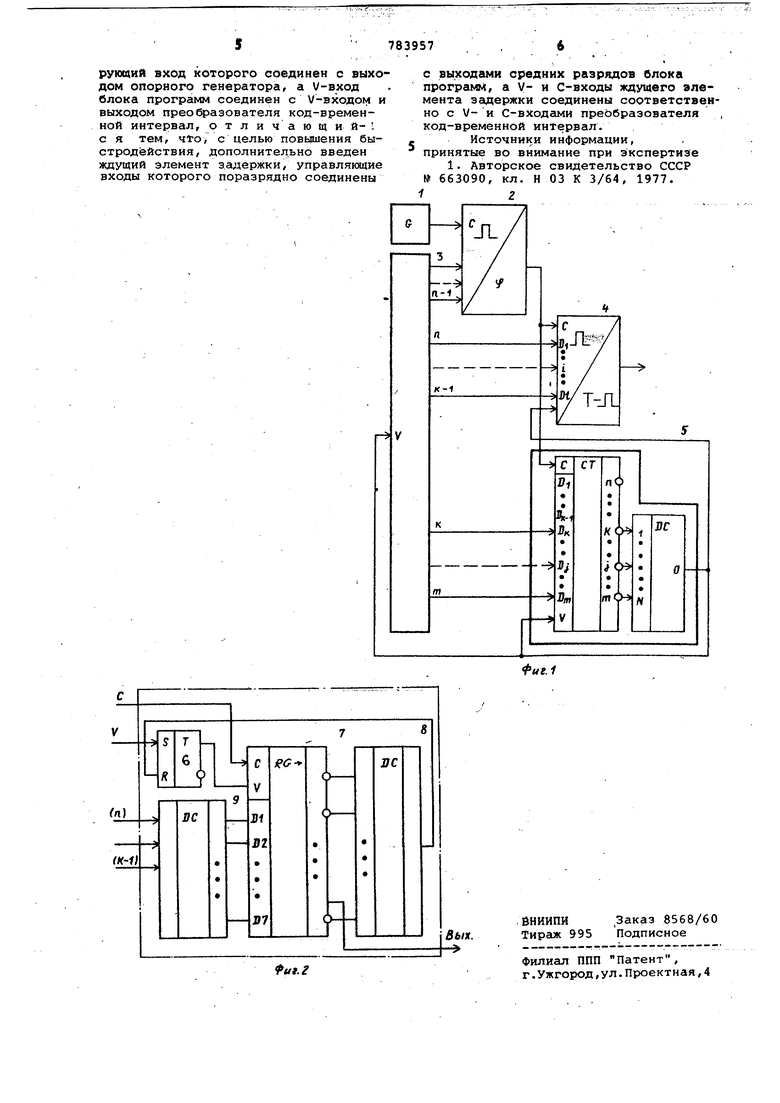

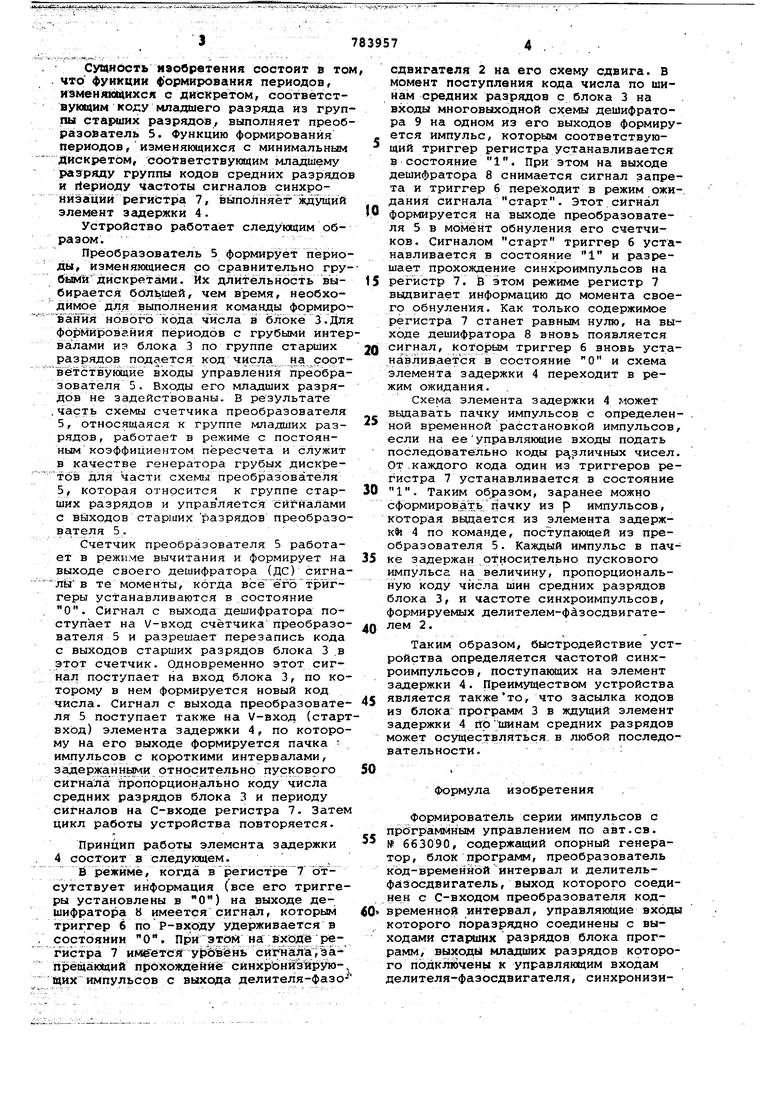

15 На фиг, 1 представлена функциональная схема устройства, на фиг. 2 функциональная схемапримера конкретного выполнения ждущего элемента задержки .

20 Формирователь серий импульсов с программным управлением содержит опорный генератор 1, делитель-фазосдвигатель 2, блок nporpau iM 3, ждущий элемент задержки 4 и преобразователь

25 код-временной интервал 5,

Ждущий элемент задержки (фиг, 2)

содержит триггер 6, сдвигающий регистр 7, дешифратор 8 нулевого состояния регистра и многовыходной дешифратор 9.

Суцность изобретения состоит в тоМ| что функции формирования периодов, иэмеиякцихся с дискретом, соответствующим младшего разряда из группы старших разрядов, выполняет преобразователь 5. Функцию формирования . периодов, изменякхцихся с минимальным Дискретом, сор ветствующим младшему разряду группы кодов средних разрядов и йериоду частоты сигналов синхронйэацйй регистра 7, выполняет-ждущий элемент задержки 4.Ю

Устройство работает следующим образом.

Преобразователь 5 формирует пёриоДЫ, изменяющиеся со сравнительно грубымйдискретами. Их длительность вы- 15 бираётся большей, чем время, необходимое для выполнения команды формиро вания нового кода в блоке 3.Для формйровг.ния периодов с грубыми интервалами из блока 3 по группе старших 20 разрядов под.ется код числа на соотвётствукхцйе входы управления преобразователя 5. Входы его младших разрядов не задействованы. В результате .часть схемы счетчика преобразователя 5, относящаяся к группе младших раз- рядов, работает в режиме с постоянным коэффициентом пересчета и служит в качестве генератора грубых дискре тов для части схемы преобразователя

5, которая относится к группе стар- 30 ших разрядов и управляется сИгйалаМи с выходов старших 1азрядов преобразователя 5.

Счетчик преобразователя 5 работает в режиме вычитания и формирует на 35 выходе своего дешифратора (ДС) сигна лйв те моменты, когда триггеры устанавливаются в состояние

, О. Сигнал с выхода дешифратора поступает на V-вход счётчика преобразо- дп вателя 5 и разрешает перезапись кода с выходов старших разрядов блока 3 ,в этот счетчик. Одновременно этот сигнал поступает на вход блока 3, по которому в нем формируется новый код числа. Сигнал с выхода преобразовате- 45 ля 5 поступает также на V-вход (стартвход) элемента задержки 4, по которому на его выходе формируется пачка импульсов с короткими интервалами, задержанн1лчи относительно пускового 50 сигна ла пропорциоиальйо коду числа средних разрядов блока 3 и периоду сигналов на С-входе регистра 7. Затем цикл работы устройства повторяется.

Принцип рае5оты элемента задержки 4 состоит в следующем.

В режиме, когда в регистре7 дтсутствует информация (все его триггеры установлены в О) на выходе дешифратора 8 имеется сигнал, которым {0 триггер б по Р-входу удерживается в состоянии О. При этом на входе регистра 7 урозеяъ сигнала,запрёщаший прохождение синхронйзирующйх импульсов с выхода делителя-фазосдвигателя 2 на его схему сдвига. В момент поступления кода числа по шинам средних разрядов с блока 3 на входы многовыходной схемы дешифратора 9 на одном из его выходов формируется импульс, которым соответствующий триггер регистра устанавливается в состояние 1. При этом на выходе дешифратора 8 снимается сигнал запрета и триггер 6 переходит в режим ожиДания сигнала старт. Этот сигнал формируется на выходе преобразователя 5 в момент обнуления его счетчиков. Сигналом старт триггер 6 устанавливается в состояние 1 и разрешает прохождение синхроимпульсов на регистр 7. В этом режиме регистр 7 вьщвигает информацию до момента своего обнуления. Как только содержимое регистра 7 станет равным нулю, на выходе дешифратора 8 вновь появляется сигнал, koTopfcjM триггер 6 вновь устанаэливается в состояние О и схема элемента задержки 4 переходит в режим ожидания. .

Схема элемента задержки 4 может выдавать пачку импульсов с определенной временной расстановкой импульсов, если на ееуправляющие входы подать последбвательйо коды ра зличных чисел. От .каждого кода один из триггеров регистра 7 устанавливается в состояние 1. Таким образом, заранее можно сформировать пачку из р импульсов, которая выдается из элемента задержк 5 4 по команде, поступающей из преобразователя 5. Каждый импульс в пачке задержан относктелъ о пускового импульса на величину, пропорциональную коду числа шин средних разрядов блока 3, и частоте синхроимпульсов, формируемых делителем-ф зосдвигателем 2.

Таким образом, быстродействие устройства определяется частотой синхроимпульсов , поступающих на элемент задержки 4. Преимуществом устройства является такжето, что засылка кодов из блока программ 3 в ждущий элемент задержки 4 йошинам средних разрядов может осуществляться, в любой последовательности.:

Формула изобретения

Формирователь серии импульсов с прЬ граммным управлением по авт.св. f 663090, содержащий опорйый генератор, блок программ, преобразователь код-времёйной интервал и делительфйзосдвигатель, выход которого соединен с С-входом преобразователя кодвременной интервал, управляющие входы которого поразрядно соединены с выходами старших разрядов блока программ, выходы младших разрядов которого подключены к управлягадим входам делителя-фазосдвигателя, синхрониэирукхций вход которого соединен с выходом опорного генератора, а V-вход блока программ соединен с V-входом и выходом прео азователя код-временной интервал, отличающийс я тем, что, с целью повышения быстродействия, дополнительно введен ждущий элемент з.адержки, управляющие входы которого поразрядно соединены

с выходами средних разрядов блока программ, а у- и С-входы ждущего элемента задержки соединены соответственно с V- и С-входг1ми преобразователя код-временной интервал.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 663090, кл. Н 03 К 3/64, 1977.

Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь серии импульсов | 1976 |

|

SU663090A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1413590A2 |

К-1

сг

01

л9

ПСОк

КО

- -

fO

mCH

Дп

Авторы

Даты

1980-11-30—Публикация

1978-08-09—Подача