(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

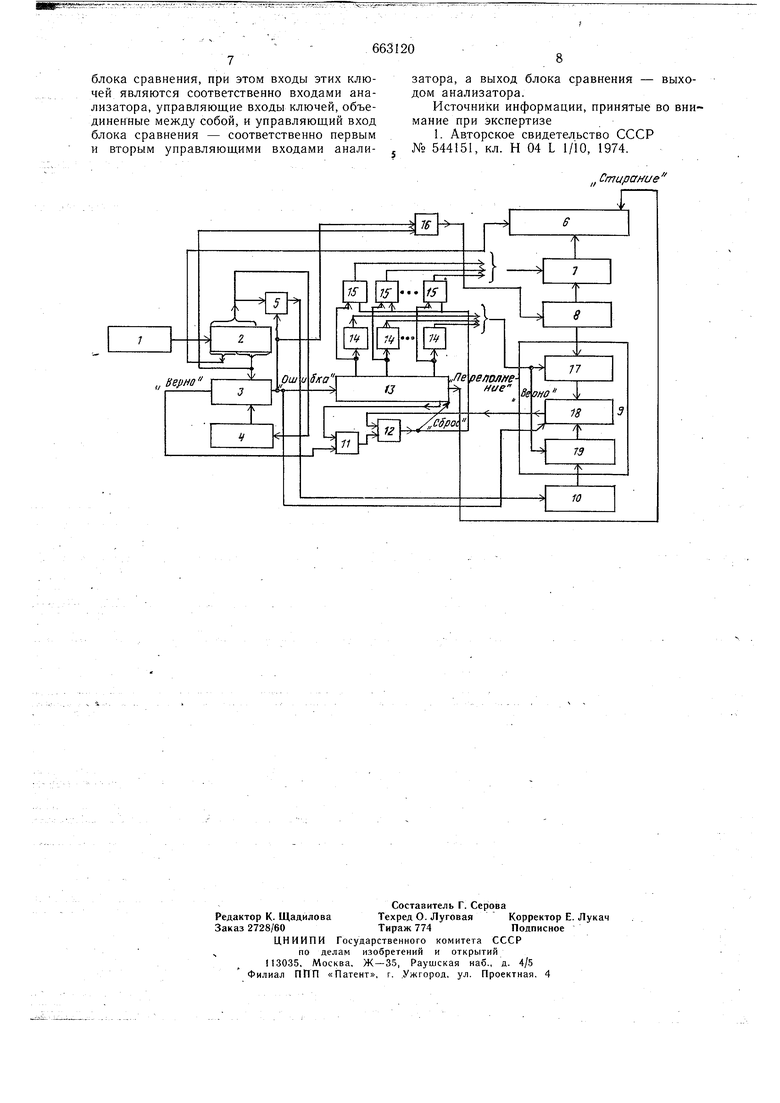

В СИСТЕМАХ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ подключен к другому входу блока сравнения а анализатор выполнен в виде двух ключей выходы которых подключены к входам блока сравнения, при этом входйэтйхклТочёй Яв ляются соответственно входами анализатора управляющие входы ключей, объединенные между собой, и управляющий вход блока сравнения - соответственно первым и вто рым управляющими входами анализатора а выход блока сравнения - выходом анализатора. На чертеже дана структурная электрическая схема предлагаемого устройства. Устройство содержит декодер 1, первый регистр памяти 2, блок сравнения 3, второй регистр памяти 4, элемент запрета 5, накопитель 6, ключ 7, регистр 8 блок:а, принятого с ошибкой, анализатор 9, регистр 10 правильно принятого блока, элемент И 11, элемент ИЛИ 12, регистр ошибок 3, блок элементов НЕ 14, блок элементов И 15 и элемент И 16. Анализатор 9 содержит ключ 17, блок сравнения 18 и ключ 19. Устройство работает следующим образом. -.- - - --,.-,.-----Принятый очередной код о вьш блок после декодирования itocfу па ётв первый регистр памяти 2, откуда его информационные символы записываются в накопитель 6 приема, в котором хранятся информационные комбинации .М ранее принятые кодовых блоков, а проверочные подаются на блок сравнения 3, на второй вход которого из второго регистра памяти 4 поступают символы комбинаций предыдущего блока, используемые в качестве эталона. После сравнения сооб щения, входящие в состав принятого блока, символы которых будут использоваться как эталон для последующего .кодового блока, записываются во второй регистр памяти 4, и в случае правильного приема блока (совпадения .сравниваемых символов) через элемент запрета 5, на-запрещающий вход кото. ,,., ,рого с выхода «ошибка блока сравнения 3 сйгна т не подается, поступает также в регистр 10 правильно принятого блокаГ Информационная комбинация, записанная в накопитель 6 приема, будет выдана потребителю после приема последующих М кодовых блоков. При обнаружении ошибкой в принятом кодовом блоке, если количество подряд обнаруженных ошибок в предыдущих кодовых блоках не превышает числа М сообщений, входящих в состав блока, производится сравнение одноименных сообщений декодированного и последнего правильно ггрйнятого блока. В этом случае с выхода «ощиб.ка блока сравнения 3 снимается сигнал, поступающий в регистр ошибок 13, элементзапрета 5, на торой вход элемента И 16 и на уп-; равляюЩий вход блока сравнения 18, по которому в регистр ошибок 13, содержащий

668120 s 5 М разрядов, записывается «1 и, следова: тельно, число единиц, записанных в регистр ошибок 13 становится равным количеству подряд обнаруженных ошибок в принятых кодовых блоках; запрещается запись через 9Jii6 MeHt запрета 5 декодированного с обнаруженной ошибкой блокав регистр 10 последнего правильно принятого блока, что обеспечивает сохранение в нем сообщений последнего блока, декодированного без обнаруженной ошибки; в регистр 8 блока с ощибкой записываются символы сообщений, вхоДйЩих в состав проверочной комбинации декодированного блока; в блоке сравнения 18 после записи информации в регистр 8 блока с. ошибкой происходит сравнение символов одноимёндых сообщений, записанных в регистр 10 последнего правильно принятого блока и регистр 8блока с ошибкой. . Выбор одноименных сообщений из указанных регистров 8 и 10 для подачи на блок сравнения 18 анализатора 9 осуществляется посредством ключей 17 и 19, управляемых с помощью регистра ошибок 13 и блока элементов НЕ 14. Допустим, что декодирован кодовый блок bi+2 при условии, что в канале искажен только Ui-1г 1 блок. При сравнении проверочной комбинации принятого кодового блока с эталоном, образованным из сообщений блока Ui+1, ошибка в нем обнаружится за искажения эталона. В этом, случае fe регистр блока с ошибкой будут занесены символы проверочной комбинации бло-. ка Ui4-2, а в регистре ошибок 13, выходы М-1 разрядов которого, начиная со второго параллельно соединены с входами блока элементов НЕ 14 и блока элементов И 15 будет заййЪана комбинация 1100. В регистре 10 последнего правильно принятого блока находятся соответствующие сообщения блока Ui . Количество разрядов регистра ошибок 13, в которых записаны нули после декодирования очередного кодового блока, опредеЛяют .число одноименных сообщений, находящихся в регистрах 10, 8 правильно принятого блока и блока с ошибкой, которые необходимо выдать на блок сравнения 18. Сигналами, подаваемыми с выходов блока элементов НЕ 14 через ключи 17 и 19 на йлок сравнения 18 с регистров 8 и 10 блоKj с ощибкой и правильно принятого блока имволы одноименных сообщений выдаются а блок сравнения 18. -- ./ ., при совпадении сравниваемых символов то и. произойдет в данном случае, поскольу блок Ut+2 в канале не искажен, с.выода «верно блока сравнения 18 сигнал рез элемент ИЛИ 12 поступит на вторые ходы элементов И блока элементов И 15, а первые входы которых полаются сигнаы С выходов разрядов регистра ошибок 13, оличество разрядов, начиная со второго.

регистра ошибок 13, в которые записаны «1 определяют количество предыдущих кодовых блоков, информационные сообщения которых необходимо исправить. В рассматриваемом примере «Ь со второго разряда регистра ощибок 13 поступит на первый вход первого элемента И блока элементов И 15 сигнал, с выхода которого обеспечится запись через ключ 7 символов информациопного блока Ut + 1 из регистра 8 блока с ошибкой, в котором хранятся сообщения, в данном случае не искаженного блока Ul -f 2, в накопитель 6 приема вместо находящейся там информационной комбинации кодового блока UL+ 1, таким образом происходит исправление искаженных информационных комбинаций. Сигналом с выхода «верно блока сравнения 18, поступающим на вход «сброс регистра ошибок 13, осуществляется стирание записанной в него комбинации.

Если число подряд обнаруженных ошибок в кодовых блоках равно М (в этом случае в регистре ошибок 13 записаны од ни «1), а последующий М + 1-ый блок декодирован без обнаруженной ошибкой, то за счет проверочной комбинации последне. го блока принятого с ошибкой, который в этом случае в канале не искажен, произойдет исправление информационных сообщений предыдущих М-1 кодовых блоков. При этом сигнал ошибка с выхода блока сравнения 3 не поступает и, следовательно, записи принятого блока в регистр 8 с ошибкой, в котором находится предыдущий блок, последний из числа декодированных с обнаруженной ошибкой, не будет, не произойдет также и записи «1 в регистр ошибок 13. Сообщения декодированного блока бу. дут записаны в регистр 10 правильно принятого блока.

Сигнал «верно с блока сравнения 3 через элемент И 11, на второй вход которого подано отпирающее напряжение с выхода М-го разряда регистра ошибок 13, элемент ИЛИ 12 поступит на вторые входы элементов И блока элементов И 15, на первые входы которых подано отпирающее напряжение с заполненного «единицами регистра ошибок 13, в этом случае сигналы с выхода элементов И блока элементов И 15 через ключи 7 произведут запись М-1 сообщений последнего декодированного с обнаруженной оц1ибкой блока,, находящегося в регистре 8 блока с ошибкой, в накопитель 6 приема, вместо находящихся там комбинаций М- предыдущих блоков. Сигналом, поступивщим на вход «сброс регистра ощибок 13, производится стирание записанной в него комбинации. Если же при условии, что число подряд обнаруя енных ошибок равно М, последующий М + 1-ый блок декодирован с ощибкой, то в регистр ошибок 13 сигналом с выхода «ощибка блока сравнения 3 будетзаписана «1. Тогда сигнал с выхода «переполнение регистЙьЛЙ йгКгйгьйИ iV.s:,.S S.«53( ошибок 13 поступит на вход «стирание накопителя 6 приема и произойдет стирание первого из числа М блоков, декодированных с обнаруженной ошибкой, после чего прием продолжается. Регистр ощибок 13 в этом случае не сбрасывается и если последующий

кодовый блок будет декодирован без ощибки, то за счет проверочной комбинации предыдущего блока, описанным выше образом, произойдет исправление сообщений информационно связанных с ним М- блоков. Если. же последующий блок будет также декодирован с ошибкой, то произойдет стирание из накопителя 6 приема информационной комбинации, следующей за стертой ранее.

Формула изобретения

1.Устройство для исправления ошибок в системах передачи дискретной информации, содержащее последовательно соединенные декодер, первый регистр памяти и блок сравнения, а также накопитель, к одному из входов которого подключен выход ключа, анализатор, выход которого подключен к одному из входов элемента ИЛИ, второй реJ гистр памяти и блок элементов НЕ, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены элемент запрета, два элемента И, регистр ошибок, регистр правильно принятого блока, регистр блока, принятого с ощибкой, и блок элемен ТОО и, при этом выход «ошибка блока сравнения подключен к входам анализатора непосредственно, через последовательно соединенные регистр ощибок и блок элементов НЕ, через последовательно соединенные

J элемент запрета, к другому входу которого подключен эталонный выход первого регистра памяти, и регистр правильно принятого блока и через последовательно соединенные первый элемент И, к другому входу которого подключен проверочный выход первого ре гистра памяти, и регистр блока, принятого с ошибкой, другой выход которого подключен к входу ключа, к управляющему входу которого подключены через блок элементов И выходы регистра ошибок, соответствующий выход которого через последовательно соединенные второй элемент И, к другому входу которого подключен выход «верно блока сравнения, и элемент ИЛИ подключен к другим входам блока элементов И и к входу «сброс регистра ошибок, выход «пеO реполнение которого подключен к входу «стирание накопителя, к другому входу которого подключен соответствующий выход первого регистра памяти, эталонный выход которого через второй, регистр памяти под,.,, ключен к другому ходу блока сравнения.

2.Устройство по П.1, отличающееся тем, что анализатор выполнен в виде двух ключей, выходы которых подключены к входам блока сравнения, при этом входы этих ключей являются соответственно входами анализатора, управляющие входы ключей, объединенные между собой, и управляющий вход блока сравнения - соответственно первым и вторым управляющими входами анализатора, а выход блока сравнения - выходом анализатора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 544151, кл. Н 04 L 1/10, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в системах передачи дискретной информации | 1980 |

|

SU896777A2 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| УСТРОЙСТВО для ЭКСПЕРИМЕНТАЛЬНОГО ИССЛЕДОВАНИЯ | 1971 |

|

SU297963A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления пакетовОшибОК | 1978 |

|

SU794756A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Устройство для приема дискретной информации с исправлением ошибок | 1980 |

|

SU919119A1 |

Авторы

Даты

1979-05-15—Публикация

1977-03-04—Подача