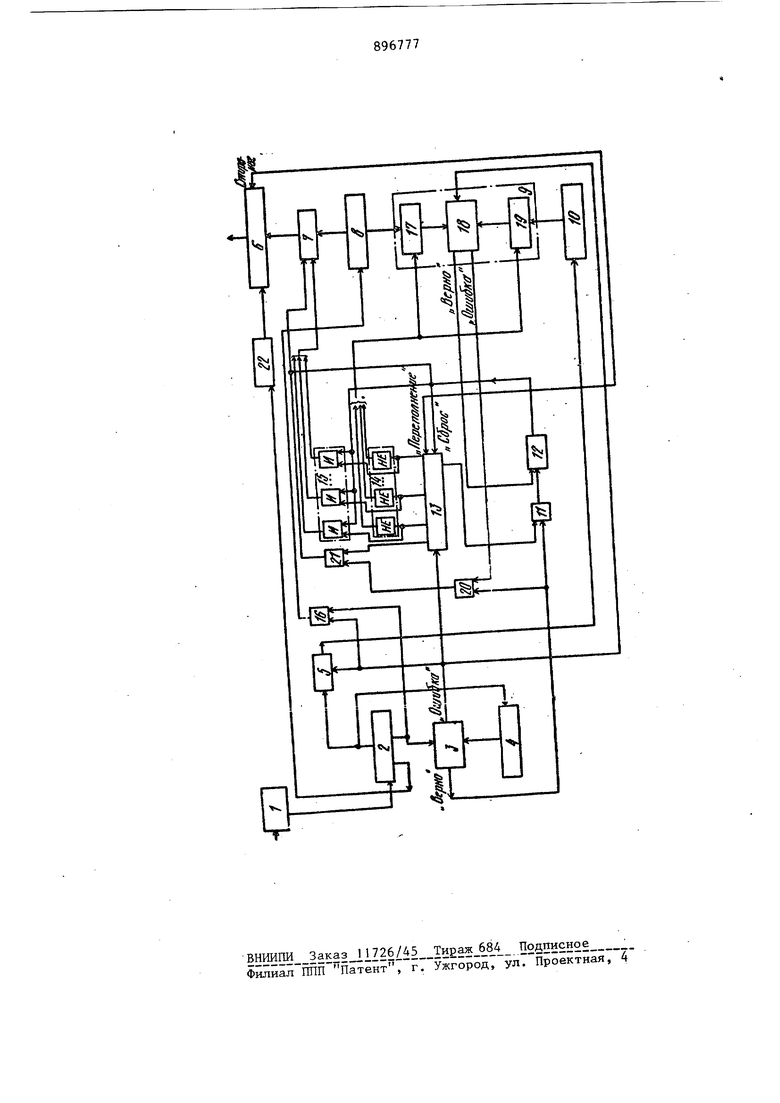

Однако в известном устройстве н статочная помехоустойчивость. Цель изобретения - повышение по мехоустойчивости передачи информации. Для достижения цели в устройство для исправления ошибок в системах передачи дискретной информации вве дены два дополнительных последовательно соединенных элемента И и бу ферный блок, причем другой вход на копителя соединен с соответствующи выходом первого регистра памяти че рез буферный блок, выход Верно блока сравнения соединен с первым первого дополнительного эле мента И, второй вход которого соед нен с другим выходом анализатора, другой вход второго дополнительного элемента И соединен с соответ ствующим выходом регистра ошибок, а выход соединен с другим входом регистра ошибок и дополнительным входом ключа. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство содержит декодер 1, первый регистр 2 памяти, блок 3 сравнения, второй регистр 4 памяти элемент 5 запрета, накопитель 6, ключ 7, регистр 8 блока принятого с ошибкой, анализатор 9, регистр 10 правильно .принятого блока, элемент И 11, элемент ИЛИ 12, регистр 13 ошибок, блок 14 элементов НЕ, блок 15 элементов И, элемент И анализатор 9 содержит ключ 17, 18 сравнения и ключ 19, элементы И 20 и 21, буферный блок 22. Устройство работает следующим образом. Принятый очередной кодовый блок после декодирования поступает в первый регистр 2 памяти, откуда ег информационные символы записываются в буферный блок 22, а проверочные подаются на блок 3 сравнения, на второй вход которого из второго регистра 4 памяти поступают символы комбинаций предыдущего блока, используемые в качестве эталона. После сравнения принятая комбинация записывается во второй регистр 4 памяти и (в случае необнаружения искажений в сравниваемых симв лах) через элемент 5 запрета, на запрещающий вход которого сигнала 74 Ошибка с выхода блока 3 сравнения, не подается, поступают на регистр 10 правильно принятого блока. Накопитель 6 рассчитан на хранение М информационных комбинаций и выдает потребителю очередную информацию - комбинацию после приема М f1 последующих кодовых блоков. При обнаружении ошибки в принятом кодовом блоке, если количество подряд обнаруженных ошибок в предьщущих кодовых блоках не превышает числа М сообщений, входящих в состав блока, производится сравнение одноименных сообщений декодированного и последнего правильно принятого блока. В этом случае с выхода Ошибка блока 3 сравнения снимается сигнал, поступающий в регистр 13 ошибок, элемент 5 запрета, на второй вход элемента И 16 и на управляклчий вход блока 18 сравнения, по которому в регистр 13 ошибок, содержащий М разрядов, записывается 1 и, следовательно, число единиц, записываемых в регистр 13 ошибок, равно числу подряд обнаруженных ошибок в принятых кодовых блоках, запрещается запись через элемент 5 запрета декодированного с обнаруженной ошибкой блока в регистр 10 последнего правильно принятого блока, что обеспечивает сохранение в нем сообщений последнего блока, декодированного без обнаруженной ошибки, в регистр Ь блока с ошибкой записывают символы сообщений, входящих в состав проверочной комбинации декодированного блока, в блоке 18 сравнения после записи информации в регистр 8 происходит сравнение символов одноименных сообщений, записанных в регистрах 8 и 10, Выбор одноименных сообщений из указанных, регистров 8 и 10 для подачи в блок 18 сравнения анализатора 9 осуществляется посредством ключей 17 и 19, управляемых регистром ошибок 13 и блоком 14 элементов НЕ. Допустим, что декодирован кодовый блок V-Ч- 2 при условии, что в канале искажен только V- -Ы блок. т При сравнении.проверочной комбинации принятого декодированного.блока с эталоном, образованным из сообщений блока -f 1, ошибка в нем обнаруживается за счет искаженного эта1лона. В этом случае в регистр 8 5 заносятся символы проверочной комбинации блока V-i-f-Z, а в регистр ошибок, выходы М - I разрядов котор го (начиная со второго) параллельно соединены с рходами- блока 14 элементов НЕ и блока 15 элементов И записывается (при ) комбинация 1100.В регистре 10 последнего прави но принятого блока находятся соотв ствуняцие сообщения блока элементов И. Количество разрядов регистра 13 ошибок, в которых записаны нули после декодирования очередного кодо вого блока, определяют число одноименных сообщений, находяищхся в регистрах 8 и 10, которые необходимо выдать на блок 18 сравнения. Сигналами, подаваемыми с выходов блока 14 элементов НЕ через ключи 17 и 19 на блок 18 сравнения с регистров 8 и 1U выдаются символы одноименных сообщений. При совпадении сравниваемых символов, что и происходит в данном сл чае, поскольку в канале не ис кажен, с выхода Верно блока 18 сравнения сигнал через элемент ШМ 12 поступает на вторые входы элементов И блока 15 элемен- i тов И, на первые входы которых подаются сигналы с выходов регистра 13 ошибок. Количество разрядов (начиная со второго) регистра 13 ошибо в которых записаны 1 , определяют количество предьщущих кодовых блоков , информационные сообщения которых надо исправить. В рассматриваемом примере 1 со второго разряда регистра 13 ошибок поступает на .первый вход первого элемента И блока 15 элементов И, сигнал с выхода которого обеспечивает запись через ключ 7 символов информационного блока 1 из регистра 8, в котором хранятся сообщения в данном слу чае неискаженного блока в накопитель 6, вместо находящейся там информационной комбинации кодового блока V - +1. Таким образом, происходит исправление искаженной информационной комбинации. Сигналом с выхода Верно блока 18 сравнения, поступающим на вход Сброс регистра 13 ошибок, происходит стирание записанной в нем информации. Если число подряд обнаруженных ошибок в кодовых блоках равно М 7 в регистре 13 ошибок записаны одни 1), а последукндий М -f 1 блок декодирован без обнаруженной ошибки, то за счет проверочной комбинации последнего блока принятого с ошибкой (на самом деле не искаженного) происходит исправление.информационных сообщений предьщущих М - 1 ко довых блоков.. При этом сигнал ошибка с выхода 3 сравнения не поступает и, следовательно, записи принятого блока в регистр 8, в котором находится последний -из числа декодированнь1х с обнаруженной ошибкой блоков не будет, не происходит и -записи 1 в регистр 13 ошибок. Сообщение декодированного блока записывается в регистр 10, Сигнал Верно с блока 3.сравнения через элемент И П, на второй вход которого-подается отпирающее напряжение с М-ого разряда регистра 13 ошибок, поступает на вто1)ые.входц элементов И блока 15 элементов И, на первые входы которых подается напряжение с выходов регистра 13 ошибок, заполненного 1. В этом случае сигналы с выхода блока 15 элементов И через ключ 7 производят запись М -1 сообщений последнего с обнаруженной ошибкой блока из регистра 8 в накопитель 6. Сигналом, поступающим на вход Сброс регистра 13 ошибок, стирается записанная в нем комбинация. . Если же при условии, что число подряд обнаруженных ошибок равно М, последний М 1 блок с ошибкой, то в регистре 13.ошибок сигналом с выхода Ошибка блока 3 сравнения запксьшаётся 1. Тогда сигнал с выхода Цереполнение регистра 13 ошибок поступает на вход.Стирание накопителя 6 и происходит стирание первого из М блоков, с ошибкой, после чего продолжается прием. Регистр 13 ошибок не сбрасывается. Если в декодированном блоке V искажены только информационные символы, то блок 3 сравнения сигнал Ошибка не выдает, 1 в регистр 13 ошибок не записывается, блок 1 .(искаженный) записывается в регистр 10 последнего правильно принятого блока и во второй регистр 4 память, а его информационное- сообщение в буферный блок 22.- Поскольку блок Vyf записан во второй регистр 4 па|мяти с искаженным информационным со об1цением, очередной кодовый блок V -fl в любом случае принимается как . ошибочный н записывается в регистр 8 блока с ошибкой. При этом в регистр 13 ошибок записывается 1, а на втором выходеанализатора 9 появляет ся сигнал Ошибка, который поступает на первый вход элемента И 20. Допустим, что кодовые блоки V,-Ь2, .., ,.M-2 искахены в канале, а блоки V, и М не искажены Тогда блок принимается, как блок с ошибкой (в регистре 13 ошибок записывается М-Ь I) и его проверочная комбинация записывается в регистр 8 блока, принятого с ошибкой Одноименные сообщения блоков и /-4-М-1 через ключи 19 и 17 поступают в блок 18 сравнения. На выходе Ошибка анализатора 9 появляется сигнал, который открывает элемент И 20. При поступлении декодированного блока блок сравнения 3 вьщает сигнал Верно, который через открытые элементы И 20 и 21 поступает на вход Сброс - регистра 13 ошибок и управляющий вход ключа 7. При этом происходит стирание содержимого регистра 13 ошибок и полное открытие ключа 7. Символы сообщений, входящие в состав проверочной комбинации блока Vi+M-l, из регистра 8 переписьюаются в М-1 (кроме первой) ячейки накопителя 6 и тем самым исправляют искаженные информационные сообщения блоков ,... ,V:f М-2, Блок записывается в регистр 10 последнего правильно принятого блока после чего прием продолжается. Формула изобретения Устройство для исправления ошибок в системах передачи дискретной информации по авт. св. № 663120, отличающееся тем, что, с целью повышения помехоустойчивости передачи информации, введены два дополнительных Последовательно соединенных элемента И и буферный блок, причем другой вход накопителя соединен с соответствующим выходом первого регистра памяти через буферный блок, выход Верно блока сравнения соединен с первым входом первого дополнительного элемента И, второй-вход которого соединен с другим выходом анализатора, другой вход второго дополнительного элемента И соединен с соответствующим выходом регистра ошибок, а выход соединен с другим входом регистра ошибок и дополнительным входом ключа. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 663120, кл. Н 04 L 1/10, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| "Устройство для исправления ошибок в системах передачи дискретной информации | 1977 |

|

SU663120A1 |

| Система передачи данных по каналам с обратной связью | 1980 |

|

SU966923A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Устройство для исправления пакетовОшибОК | 1978 |

|

SU794756A1 |

| Устройство для приема информации по двумпАРАллЕльНыМ КАНАлАМ СВязи B СиСТЕМЕ дляпЕРЕдАчи дАННыХ C РЕшАющЕй ОбРАТНОй СВязью | 1979 |

|

SU836806A2 |

| Устройство для устранения обратной работы в системах передачи дискретных сообщений с фазовой манипуляцией | 1990 |

|

SU1755722A3 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В ПОЛУДУПЛЕКСНОМ КАНАЛЕ СВЯЗИ | 1996 |

|

RU2127953C1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1976 |

|

SU745009A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-07—Подача