1

Изобретение относится к технике связи и может использоваться при построении систем передачи данных.

Известно устройство для иснравления пакетов ошибок, содержащее на передающей стороне блок согласования, стохастический преобразователь и датчик проверочных комбинаций первой ступени, а на приемной стороне последовательно соединенные блок согласования, стохастический преобразователь, накопитель и первый блок элементов И, причем разрядные входы накопителя соединены с выходами второго блока элементов И 1.

Однако такое устройство имеет невысокую точность исправления.

Цель изобретения - повышение точности исправления пакетов ошибок.

Для этого в устройство для исправления пакетов ошибок, содержащее на передающей стороне блок согласования, стохастический преобразователь и датчик проверочных комбинаций первой ступени, а на приемной стороне последовательно соединенные блок согласования, стохастический преобразователь, накопитель и первый блок элементов И, причем разрядные входы накопителя соединены с выходами второго блока элементов И, на передающей стороне введен формирователь проверочных комбинаций второй ступени, причем выход блока согласования подключен к входам стохастического преобразователя непосредственно и через последовательно

соединенные формирователь проверочных комбинаций второй ступени и датчик проверочных комбинаций, а на приемной стороне введены регистр выборки подблоков и последовательно соединенные формирователь эталонной последовательности, анализатор и блок исправления подблоков, причем выходы первого блока элементов И подключены к входам формирователя эталонной поеледовательности, а другой выход анализатора через регистр выборки подблоков подключен к другим входам первого и второго блоков элементов И, другие разрядные выходы накопителя подключены к другим входам блока исправления подблоков, формирователь эталонной последовательности состоит из регистра стираний и регистра выборки эталона, выходы которых подключены к входам блока элементов И, входы и выходы регистра

етираиий и регистра выборки эталона и выходы блока элементов Il являются соответственно входами и выходами формирователя эталонной последовательности, а анализатор состоит из последовательно соединенных )егист)а проверочной комбинации, ,бло.ка сравнения, блока управления, первого ключа и регистра сравнения, а также второго ключа, входы которого соединены соответственно со вторыми выходами регистра проверочных комбинаций и блока управления, вход которого соединен с другим входом первого ключа, а выход регистра сравнения подключен к другому входу блока сравнения, другие вход и выход регистра сравнения, вход регистра проверочных комбинаций, а также третий н четвертый выходы блока управления и выход второго ключа являются соответственно входами и выходами анализатора.

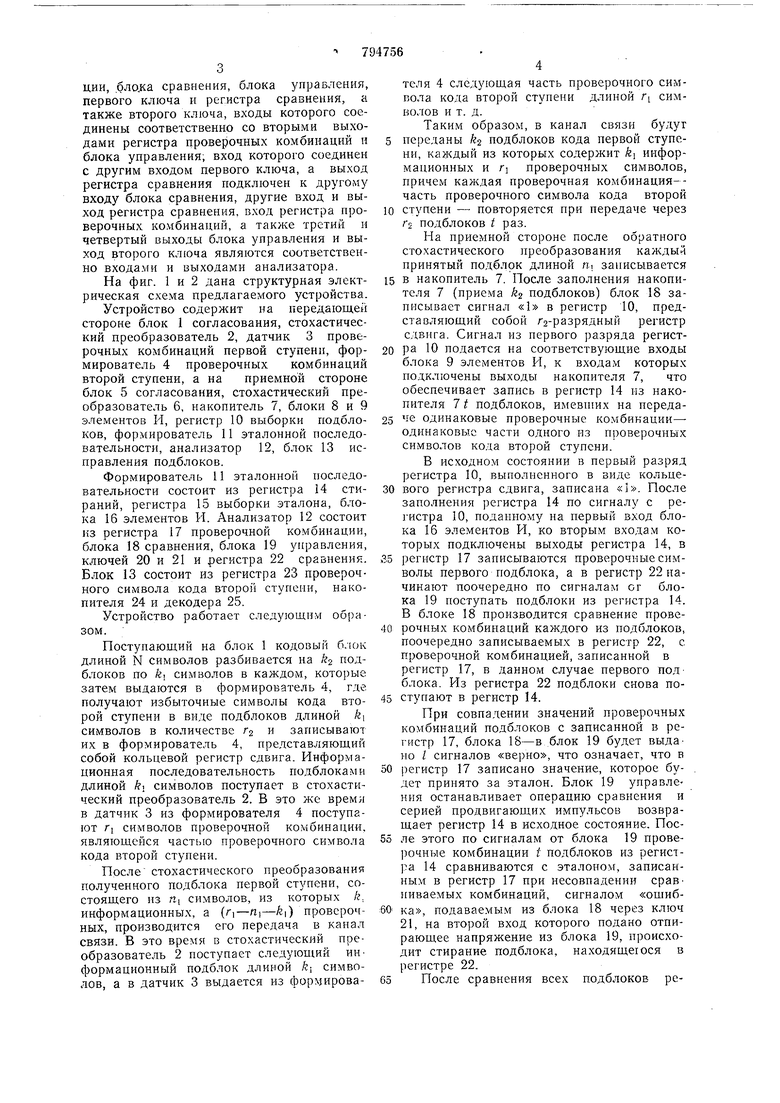

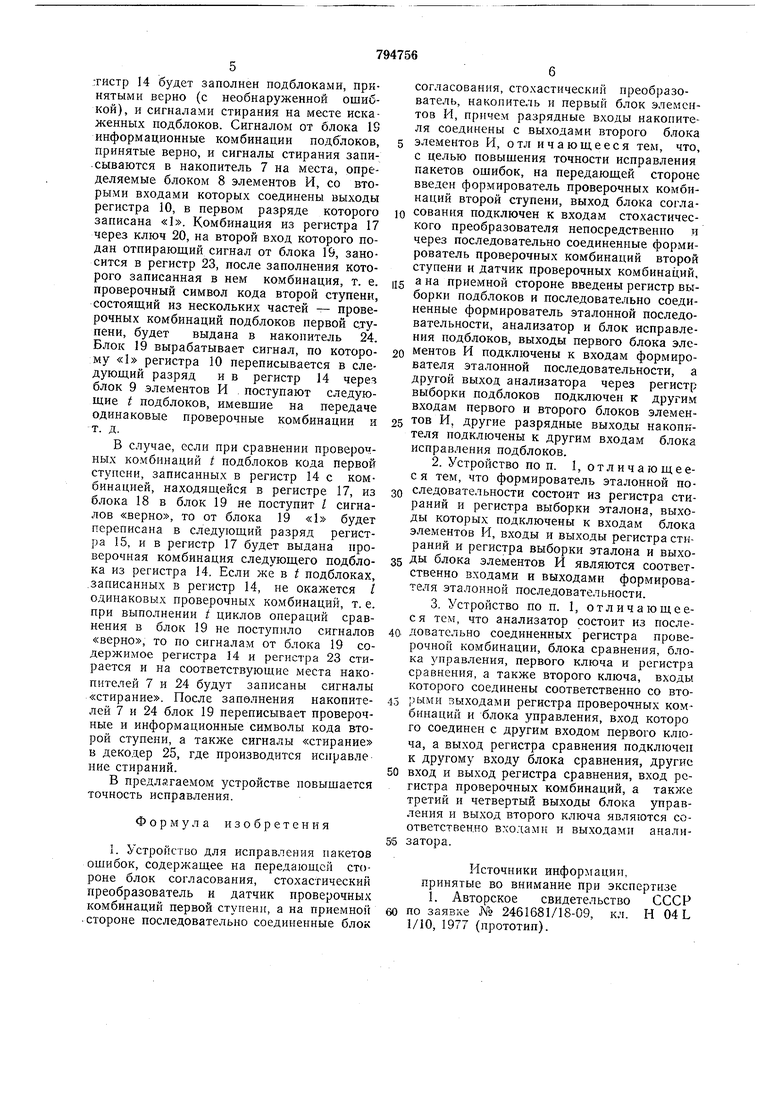

На фиг. 1 и 2 дана структурная электрическая схема предлагаемого устройства.

Устройство содержит на передающей стороне блок 1 согласования, стохастический преобразователь 2, датчик 3 проверочных комбинаций первой ступени, формирователь 4 проверочных комбинаций второй ступени, а на приемной стороне блок 5 согласования, стохастический преобразователь 6, накопитель 7, блоки 8 и 9 элементов И, регистр 10 выборки подблоков, формирователь 11 эталонной последовательности, анализатор 12, блок 13 исправления подблоков.

Формирователь 11 эталонной последовательности состоит из регистра 14 стираний, регистра 15 выборки эталона, блока 16 элементов И. Анализатор 12 состоит из регистра 17 проверочной комбинации, блока 18 сравнения, блока 19 управления, ключей 20 и 21 и регистра 22 сравнения. Блок 13 состоит из регистра 23 проверочного символа кода второй ступени, накопителя 24 и декодера 25.

Устройство работает следующим образом.

Поступающий на блок 1 кодовый блок длиной N символов разбивается на иг подблоков по ki символов в каждом, которые затем выдаются в формирователь 4, где получают избыточные символы кода второй ступени в виде подблоков длиной k символов в количестве г и записывают их в формирователь 4, представляющий собой кольцевой регистр сдвига. Информационная последовательность подблоками длиной ki символов поступает в стохастический преобразователь 2. В это же время в датчик 3 из формирователя 4 поступают TI символов проверочной комбинации, являющейся частью проверочного символа кода второй ступени.

После стохастического преобразования полученного подблока первой ступени, состоящего из fii символов, из которых /г, информационных, а () проверочных, производится его передача в канал связи. В это время в стохастический преобразователь 2 поступает следующий информационный подблок длиной k; символов, а в датчик 3 выдается из формирователя 4 следующая часть проверочного символа кода второй ступени длиной г символов и т. д.

Таким образом, в канал связи будут 5 переданы 2 подблоков кода первой ступени, каждый из которых содержит k информационных и Г проверочных символов, причем каждая проверочная комбинация-часть проверочного символ-а кода второй

10 ступени - повторяется при передаче через Г2 подблоков t раз.

На приемной стороне после обратного стохастического преобразования каждый принятый подблок длиной п, записывается 15 в накопитель 7. После заполнения накопителя 7 (приема kz подблоков) блок 18 записывает сигнал «1 в регистр 10, представляющий собой Г2-разрядный регистр сдвига. Сигнал из первого разряда регистра 10 подается на соответствующие входы блока 9 элементов Н, к входа.м которых подключены выходы накопителя 7, что обеспечивает запись в регистр 14 из накопителя 7 t подблоков, имевших на передаче одинаковые проверочные комбинации одинаковые части одного из проверочных символов кода второй ступени.

В исходном состоянии в первый разряд регистра 10, выполненного в виде кольцевого регистра сдвига, записана «1. После заполнения регистра 14 по сигналу с регистра 10, поданному на нервый вход блока 16 элементов И, ко вторым входам которых подключены выходы регистра 14, в

5 регистр 17 записываются проверочные символы первого подблока, а в регистр 22 начинают поочередно по сигналам ог блока 19 поступать подблоки из регистра 14. В блоке 18 производится сравнение прове0 рочных комбинаций каждого из подблоков, поочередно записываемых в регистр 22, с проверочной комбинацией, записанной в регистр 17, в данном случае первого поД блока. Из регистра 22 подблоки снова поступают в регистр 14.

При совпадении значений проверочных комбинаций подблоков с записанной в регистр 17, блока 18-в .блок 19 будет выдано / сигналов «верно, что означает, что в

0 регистр 17 записано значение, которое будет прииято за эталон. Блок 19 управления останавливает операцию сравнения и серией продвигающих импульсов возвращает регистр 14 в исходное состояние. После этого по сигналам от блока 19 проверочные комбинации t подблоков из регистра 14 сравниваются с эталоном, записанным в регистр 17 при несовпадении сравниваемых комбинаций, сигналом «ошиб0 ка, подаваемым из блока 18 через ключ 21, на второй вход которого подано отпирающее напряжение из блока 19, происходит стирание подблока, находящеюся в регистре 22.

5 После сравнения всех подблоков ре:гистр 14 будет заполнен подблоками, принятыми верно (с необнаруженной ошибкой), и сигналами стирания на месте искаженных подблоков. Сигналом от блока 19 информационные комбинации подблоков, принятые верно, и сигналы стирания записываются в накопитель 7 на места, определяемые блоком 8 элементов И, со вторыми входами которых соединены выходы регистра 10, в первом разряде которого записана «1. Комбинация из регистра 17 через ключ 20, на второй вход которого подан отпирающий сигнал от блока 19, заносится в регистр 23, после заполнения которого записанная в нем комбинация, т. е. проверочный символ кода второй ступени, состоящий из нескольких частей - проверочных комбинаций подблоков первой ступени, будет выдана в накопитель 24. Блок 19 вырабатывает сигнал, по которому «1 регистра 10 переписывается в следующий разряд и в регистр 14 через блок 9 элементов И поступают следующие t подблоков, имевщие на передаче одинаковые проверочные комбинации и т. д.

в случае, если при сравнении проверочных комбинаций / подблоков кода первой ступени, записанных в регистр 14 с комбинацией, находящейся в регистре 17, из блока 18 в блок 19 не поступит / сигналов «верно, то от блока 19 «1 будет переписана в следующий разряд регистра 15, и в регистр 17 будет выдана проверочная комбинация следующего подблока из регистра 14. Если же в t подблоках, .записанных в регистр 14, не окажется / одинаковых проверочных комбинаций, т. е. при выполнении t циклов операций сравнения в блок 19 не поступило сигналов «верно, то по сигналам от блока 19 содержимое регистра 14 и регистра 23 стирается и на соответствующие места накопителей 7 н 24 будут записаны сигналы «стирание. После заполнения накопителей 7 н 24 блок 19 переписывает проверочные и информационные символы кода второй ступени, а также сигналы «стирание в декодер 25, где производится исиравле ние стираний.

В предлагаемом устройстве повышается точность исправления.

Формула изобретения

1. Устройство для исправления пакетов ошибок, содержащее на передающей стороне блок согласования, стохастический преобразователь и датчик проверочных комбинаций первой ступени, а на приемной стороне последовательно соединенные блок

огласования, стохастический преоб|)азоатель, накопитель и первый блок элеменов И, причем разрядные входы накопитея соединены с выходами второго блока

лементов И, отл ичающееся тем, что, целью повышения точности исправления пакетов ошибок, на передающей стороне веден формирователь проверочных комбинаций второй ступени, выход блока соглаования подключен к входам стохастического преобразователя непосредственно и через последовательно соединенные формирователь проверочных комбинаций второй ступени и датчик проверочных комбинаций,

а на приемной стороне введены регистр выборки подблоков и последовательно соединенные формирователь эталонной последовательности, анализатор и блок исправления подблоков, выходы первого блока элементов И подключены к входам формирователя эталонной последовательности, а другой выход анализатора через регистр выборки подблоков подключен к другим входам первого и второго блоков элементов И, другие разрядные выходы накопителя подключены к другим входам блока исправления подблоков.

2.Устройство по п. I, отличающееся тем, что формирователь эталонной последовательности состоит из регистра стираний и регистра выборки эталона, выходы которых подключены к входам блока элементов И, входы и выходы регистра стираний и регистра выборки эталона и выходы блока элементов И являются соответственно входами и выходами формирователя эталонной последовательности.

3.Устройство по п. 1, отличающееся тем, что анализатор состоит из последовательно соединенных регистра проверочной комбинации, блока сравнения, блока зправления, первого ключа и регистра сравнения, а также второго ключа, входы которого соединены соответственно со вторыми выходами регистра проверочных комбинаций и блока управления, вход которо го соединен с другим входом первого ключа, а выход регистра сравнения подключен к другому входу блока сравнения, другие

вход и выход регистра сравнения, вход регистра проверочных комбинаций, а также третий и четвертый выходы блока управления и выход второго ключа являются соответственно входами и выходами анализатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2461681/18-09, кл. Н 04 L 1/10, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации с исправлением ошибок | 1980 |

|

SU919119A1 |

| "Устройство для исправления ошибок в системах передачи дискретной информации | 1977 |

|

SU663120A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| Устройство для исправления ошибок в системах передачи дискретной информации | 1980 |

|

SU896777A2 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Устройство для исправления ошибок дискретной информации | 1977 |

|

SU690640A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Перестановочный декодер с альтернативными решениями | 2024 |

|

RU2826701C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2007 |

|

RU2344556C1 |

Авторы

Даты

1981-01-07—Публикация

1978-04-24—Подача