ферного регистра, второй вход - с выходом второго буферного регистра, третий вход - с выходом третьего буферного регистра, четвертый вход - с выходом регистра поразрядных сумм, первый выход суммирующего блока соединен с входом четвертого буферного регистра, а второй выход - с входом пятого буферного регистра.

Цель достигается также тем, что суммирующий блок содержит в каждом разряде логические элементы Исключающее ИЛИ, И и ИЛИ, причем входы первого элемента Исключающее ИЛИ и первого элемента И подключены к первому и второму входам соответствующего разряда суммирующего блока, третий и четвертый входы которого подключены к входам второго элемента Исключающее ИЛИ, выход первого элемента Исключающее ИЛИ соединен с первыми входами третьего элемента Исключающее ИЛИ и второго элемента И, вторые входы которых подключены к третьему входу соответствующего разряда суммирующего блока, четвертый, вход которого соединен с первым выходом третьего элемента И, второй вход которого соединен с выходом третьего элемента Исключающее ИЛИ, а выход - с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, входы четвертого элемента Исключающее ИЛИ подключены к выходам первого и второго элементов Исключающее ИЛИ, а выход - к первым входам четвертого элемента И и пятого элемента Исключающее ИЛИ, вторые входы которых подключены к входу переноса из предыдущего разряда суммирующего блока, входы второго элемента ИЛИ соединены с выходами первого и второго элементов И, а выход - с выходом переноса в последующий разряд суммирующего блока, выходы пятого элемента Исключающее ИЛИ и первого элемента ИЛИ подключены соответственно к первому и второму .выходам данного разряда суммирующего блока.

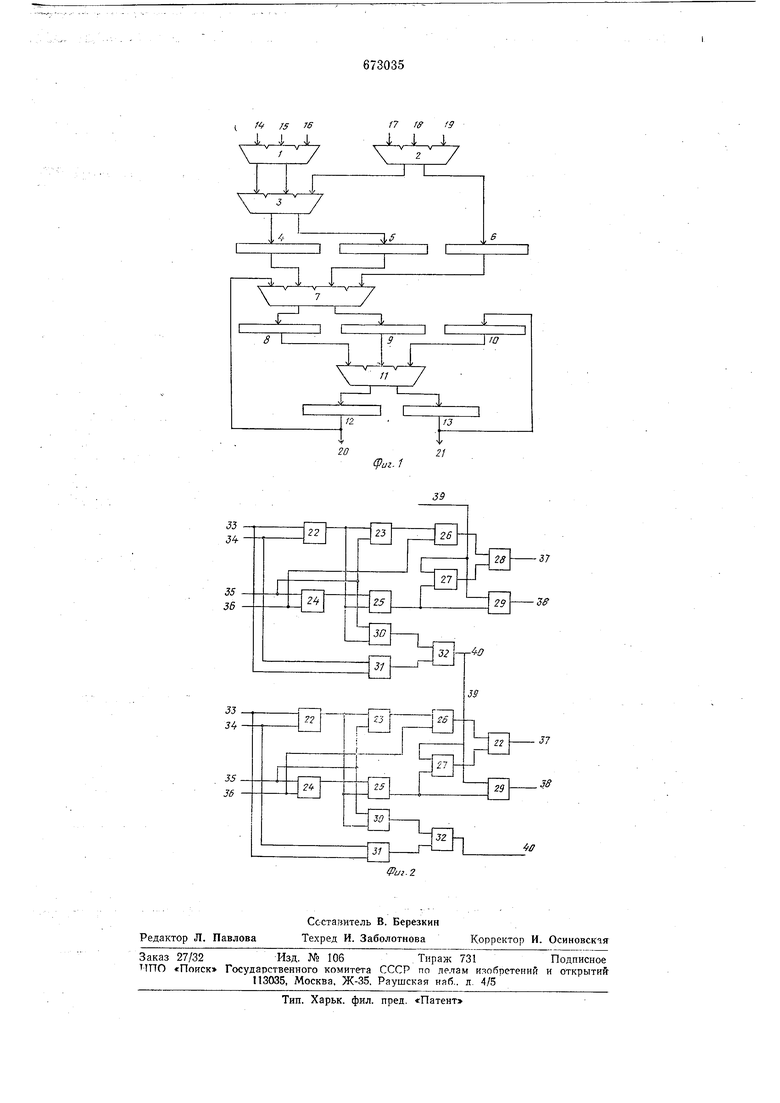

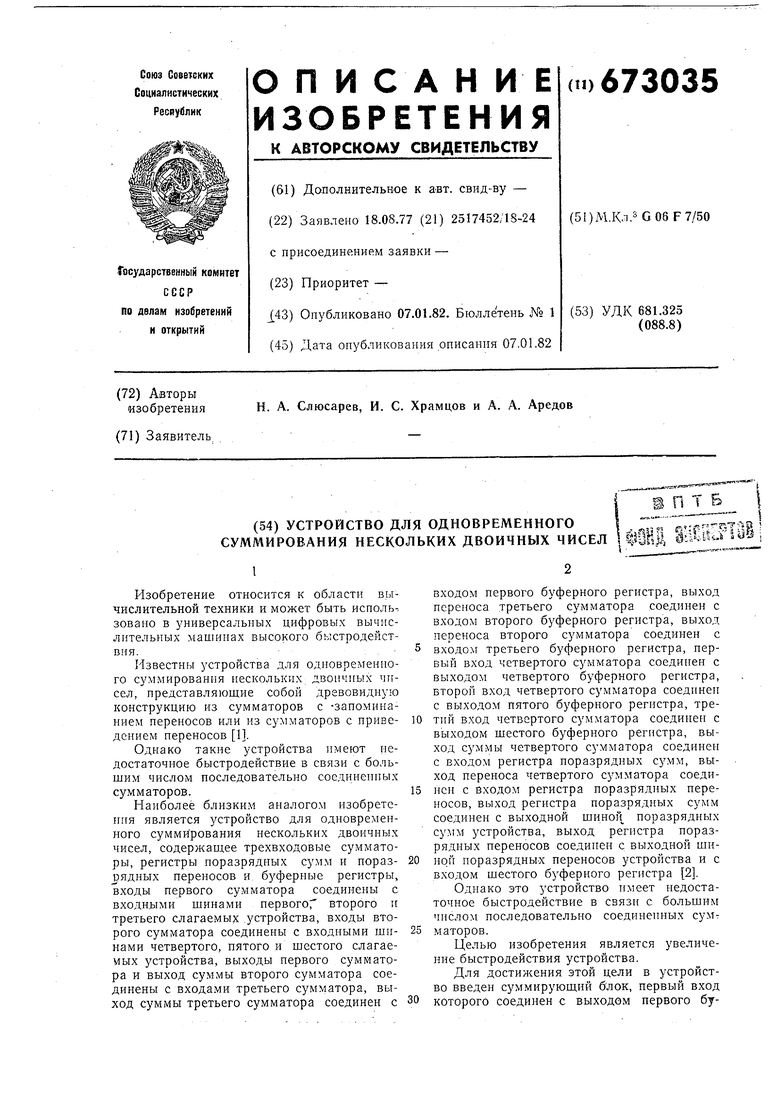

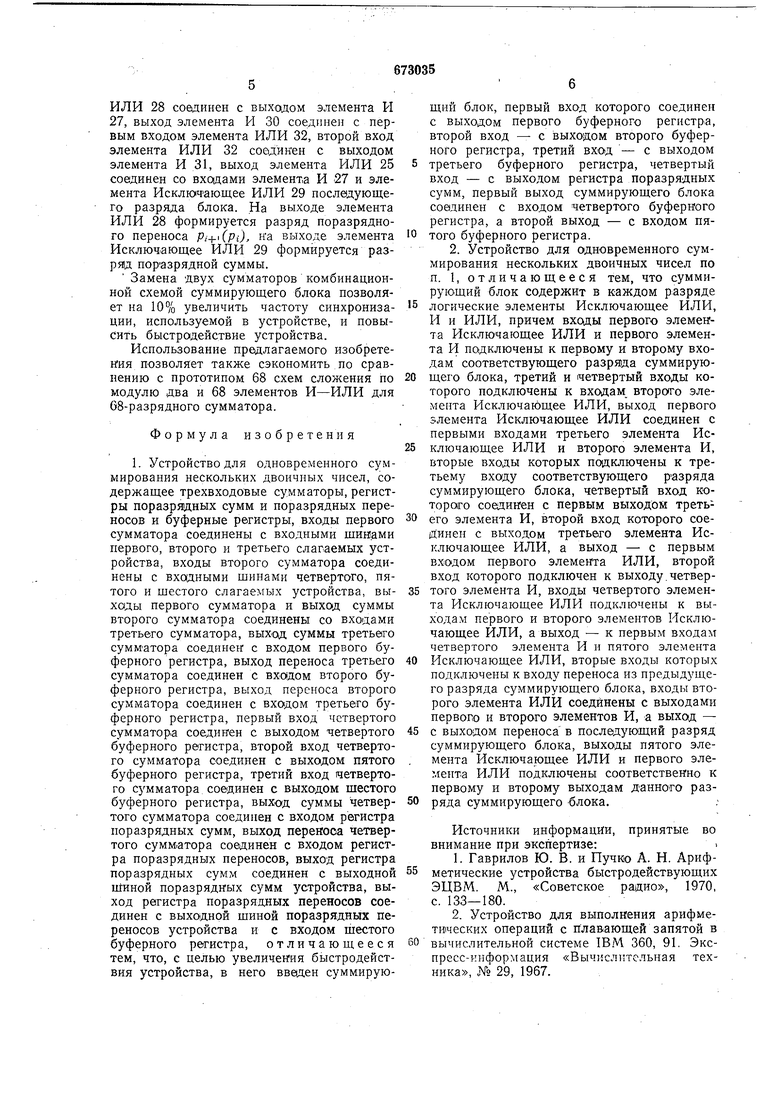

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - два разряда суммирующего блока.

Устройств о. содержит трехвходовые сумматоры 1, 2, 3, 4, буферные регистры 4, 5, 6, суммирующий блок 7, буферные регистры 8, 9, 10, трехвходовый сумматор 11, регистр поразрядных сумм 12, регистр поразрядных переносов 13, входные шины слагаемых 14, 15, 16, 17, 18, 19 устройства, выходную шину 20 поразрядных сумм устройства и выходную шину 21 поразрядных переносов устройства.

Суммирующий блок 7 содержит в каждом разряде элементы Исключающее ИЛИ 22, 23, 24, 25, элементы И 26, 27, элемент ИЛИ 28, элемент Исключающее ИЛИ 29, элементы И 30, 31, элемент ИЛИ 32, входы

33, 34, 35, 36 разряда блока, вы.ходы 37, 38 разряда блока, вход 39 переноса из предыдущего разряда блока, выход 40 переноса из предыдущего разряда блока. Сложение двоичных чисел на предлагаемом устройстве может производиться непрерывно. В то время как информация первых шести слагаемых, обработанная на логике первого уровня (сумм1аторы 1, 2, 3)

(фиг. 1) и на логике второго уровня (суммирующий блок 7), поступает на буферные регистры 8, 9, 10 второго уровня, на входные щины слагаемых 14, 15, 16, 17, 18, 19 подается следующая группа слагаемых.

Одновременно с поступлением информации первых шести слагаемых, обработанной на логике третьего уровня (сумматор М) и имеющей вид поразрядных сумм и перекосов результата сложения, на регистры поразрядных сумм 12 и поразрядных переносов 13, информация второй группы слагаемых, обработанная на логике первого уровня, поступает на буферные регистры 4, 5, 6 первого уровня. Таким образом, осуществляется совмещение во времени нескольких последовательных операций сложения.

Устройство работает в режиме с накоплением суммы.

Результат сложения очередной группы слагаемых добавляется к результату сложением следующей группы слагаемых на стадии его формирования.

Таким образом, производится накапливание суммы.

Структура суммирующего блока 7 показана на примере выполнения двух разрядов (фиг. 2).

Разряды слагаемых G/..I.I и bi+ (uj + bi)

подаются .на входы 33 и 34 разряда блока и соответственно на входы элемента Исключающее ИЛИ 22 и wa входы элемента И 31. Разряды слагаемых c,-.fi и (Ci и di) подаются на входы разряда блока

н соответственно на входы элемента Исключающее ИЛИ 24. Кроме того, рНзряд слагаемого Гс,) подается на первый вход элемента Исключающее ИЛИ 23 и на второй вход элемента И 30. .

Разряд слагаемых d,--M (di) подается на

второй вход элемента И. Выход элемента Исключающее ИЛИ 22 соединен с вторым входом элемента Исключающее ИЛИ 23, с первым входом элемента Исключающее

ИЛИ 25 и с первым входом элемента И 30, второй вход элемента Исключающее 11ЛИ 25 соеданен с выходом элемента Исключающее ИЛИ 24, выход элемента Исключающее ИЛИ 23 соединен с первым входом элемента И 26, выход элемента Исключающее ИЛИ 25 соединен с первым вхоиом элемента И 27 и с первым входом элемента Исключающее ИЛИ 29, выход элемента И 26 соединен с первым входом

элемента ИЛИ 28, второй вход элемента

ИЛИ 28 соединен с выходом элемента И 27, выход элемента И 30 соединен с нервым входом элемента ИЛИ 32, второй вход элемента ИЛИ 32 соединен с выходом элемента И 31, выход элемента ИЛИ 25 соединен со входами элемента И 27 и элемента Исключающее ИЛИ 29 последующего разряда блока. На выходе элемента ИЛИ 28 формируется разряд норазрядного нереноса p/+i (Рг), на выходе элемента Исключающее ИЛИ 29 формируется разряд норазрядной суммы.

Замена двух сумматоров комбинационной схемой суммирующего блока позволяет на 10% увеличить частоту синхронизации, иснользуемой в устройстве, и повысить быстродействие устройства.

Использование предлагаемого изобретения позволяет также сэкономить но ср-авнению с прототипом 68 схем сложения но модулю два и 68 элементов И-ИЛИ для 68-разрядного сумматора.

Формула изобретения

1. Устройство для одновременного суммирования нескольких двоичных чисел, содержащее трехвходовые сумматоры, регистры поразрядных сумм и поразрядных переносов и буферные регистры, входы первого сумматора соединены с входными щинами первого, второго и третьего слагаемых устройства, входы второго сумматора соединены с входными шинами четвертого, пятого и шестого слагаемых устройства, выходы первого сумматора и выход суммы второго сумматора соединены со входами третьего сумматор-а, выход суммы третьего сумматора соединен с входом первого буферного регистра, выход переноса третьего сумматора соединен с входом второго буферного регистра, выход переноса второго сумматора соединен с входом третьего буферного регистра, первый вход четвертого сумматор.а соединен с выходом -четвертого буферного регистра, второй вход четвертого сумматора соединен с выходом пятого буферного регистра, третий вход четвертого сумматора соединен с выходом щестого буферного регистра, выход суммы четвертого сумматора соединен с входом регистра поразрядных сумм, выход переноса четвертого сумм.атора соединен с входом регистра норазрядных переносов, выход регистра поразрядных сумм соединен с выходной Щиной норазрядных сумм устройства, выход регистра поразрядных переносов соединен с выходной шиной поразрядных переносов устройства и с входом шестого буферного регистра, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введен суммирующий блок, первый вход которого соединен с выходом первого буферного регистр|а, второй вход - с выходом второго буферного регистра, третий вход - с выходом третьего буферного регистра, четвертый вход - с выходом регистра поразрядных сумм, первый выход суммирующего блока соединен с входом четвертого буферного регистра, а второй выход - с входом пятого буферного регистра.

2. Устройство для одновременного суммирования нескольких двоичных чисел по п. 1, отличающееся тем, что суммирующий блок содержит в каждом разряде

логические элементы Исключающее ИЛИ, И и ИЛИ, причем входы первого элемента Исключающее ИЛИ и первого элемента И подключены к первому и второму входам соответствующего разряда суммирующего блока, третий и четвертый входы которого подключены к входам второго элемента Исключающее ИЛИ, выход первого элемента Исключающее ИЛИ соединен с первыми входами третьего элемента Исключающее ИЛИ и второго элемента И, вторые входы которых подключены к третьему входу соответствующего разряда суммирующего блока, четвертый вход которого соединен с первым выходом третьего элемента И, второй вход которого соединен с выходом третьего элемента Исключающее ИЛИ, а выход - с нервым входом первого элемента ИЛИ, второй вход которого подключен к выходу.четвертого элемента И, входы четвертого элемента Исключающее ИЛИ подключены к выходам первого и второго элементов Исключающее ИЛИ, а выход - к первым входам четвертого элемента И н пятого элемента

Исключающее ИЛИ, вторые входы которых подключены к входу переноса из предыдущего разряда суммирующего блока, входы второго элемента ИЛИ соединены с выходами нервого и второго элементов И, а выход -

с ВЫХОДОМ переноса в последующий разряд суммирующего блока, выходы пятого элемента Исключающее ИЛИ и первого элемента ИЛИ подключены соответственно к первому и второму выходам данного разряда суммирующего блока.

Источники информации, принятые во внимание при экспертизе:

1.Гаврилов Ю. В. и Пучко А. Н. Арифметические устройства быстродействующих

SUBAIi. М., «Советское радио, 1970, с. 133-180.

2.Устройство для выполнения арифметических операций с плавающей запятой в

вычислительной системе 1В.М 360, 91. Экспресс-информация «Вычислительная техника, № 29, 1967.

( if Г5 ГВ

L

17 tff tg JiI

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

| ПАРАЛЛЕЛЬНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1969 |

|

SU242498A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

202

35 36

J L

J L

/o

13

(риг. 1

39

Г

3ff

Авторы

Даты

1982-01-07—Публикация

1977-08-18—Подача