Изобретение относится к области цифровой вычислительной техники и может быть использовано при построении электронных цифровых вычислительных машин.

Известные параллельные арифметические устройства (АУ) имеют четырехступенчатую замкнутую цепь сумматора, в которой недостаточно используются скоростные возможности элементов; для приведения двухрядного кода к однорядному требуется специальное устройство, а для выполнения каждой арифметической операции - отдельное оборудование.

Целью изобретения является повышение быстродействия арифметического устройства с одновременным уменьшением количества оборудования.

Это достигается тем, что устройство состоит из двух пар регистров, разбитых на регистр суммы и регистр переносов каждая, выполненных на элементах с двухфазным управлением, причем выходы каждого разряда первой и второй пар регистров соединены через схемы совпадения с собственными входами, а также со входами трехвходовых сумматоров. Выходы сумматоров подключены на входы каждого разряда соответственно второй и первой пары регистров суммы и регистров переносов.

или обеих пар регистров соединены также со схемами совпадения, выходы которых подключены ко входам каждого разряда другой или других пар регистров.

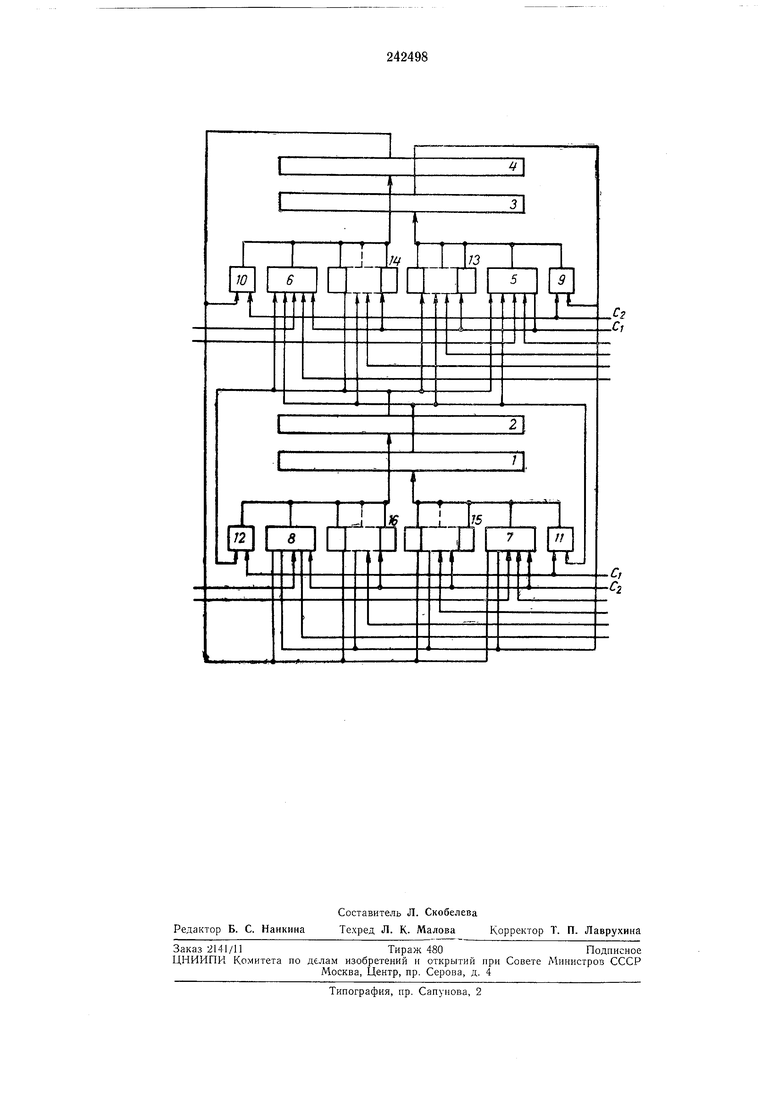

К схемам совпадения и трехвходовым сумматором подсоединены управляющие шины, сигналы которых разрешают работу схем, необходимых для выполнения нужной операции. На чертеже приведена блок-схема предложенного устройства, где приняты следующие обозначения:

1 - первый регистр поразрядных сумм; 2 - первый регистр поразрядных переносов; 5 - второй регистр поразрядных сумм; 4 - второй

регистр поразрядных переносов; 5-8 - трехвходовые сумматоры; 9-12 - схемы совпадения, осуществляющие обратную связь; 13- 16 - группа схем совпадения, обеспечивающих выполнение логических операций.

Регистры выполнены на одновходовых усилителях с парафазными выходами. Схемы на выходах каждого разряда обеих пар регистров управляются двумя постоянно идущими прямоугольными противофазными сигналами со

скважностью 2-С и С, из которых один управляет схемой совпадения обратной связи, а второй - остальными схемами, подключенными ко входу усилителя. Одну половину периода производится прием кода в пару региЗатем включаются схемы обратной связи, и другую половину периода полученный код хранится в паре регистров. Сигналы, управляющие приемом и хранением в одной паре регистров, противофазны сигналам, управляющим приемом и хранением во второй паре регистров.

Хранением и приемом для регистров / и 2 управляют соответственно сигналы С и 2, а для регистров 5, 4 - сигналы Са и Ci.

После первоначального занесения слагаемых на любую пару регистров, например на регистры 1 и 2, код, хранящийся в этих регистрах, суммируется в трехвходовых сумматорах 5 к 6. По сигналу С происходит прием результата суммирования в регистры 3 н 4. Затем по сигналу €2 включается цепь обратной связи 9 и 10 регистров 3 к 4 и производится суммирование полученного результата в сумматорах 7 и 5 с любым другим кодом, поступающим на третьи входы этих сумматоров. Новый код с выходов сумматоров 7 и 8 поступает на входы регистров 1 и 2, и процесс повторяется.

Таким образом, код циркулирует в АУ, причем суммирование производится при каждой передаче кода с одной пары регистров на другую, т. е. дважды за период управляющего двухфазного сигнала.

Для получения однорядного результата производится поразрядное суммирование полученного двухрядного кода, т. е. сумма и перенос используются как новые слагаемые, а на третьи входы сумматоров 5, 6 и 7, 8 подается код «О. Этот процесс поразрядного суммирования продолжается до тех пор, пока не исчезнут поразрядные переносы.

Такая организация работы предложенного устройства обеспечивает необходимое быстродействие и позволяет выполнять в одном и том же устройстве все арифметические операции - сложение, вычитание, умножение, деление, а также все требуемые логические операции, что дает значительную экономию оборудования.

Предмет изобретения

1.Параллельное арифметическое устройство, содержащее регистры и логические элементы, отличающееся тем, что, с целью повышения быстродействия и экономии оборудования, оно состоит из двух пар регистров, разбитых на регистр суммы и регистр переносов каждая, выполненных на элементах с двухфазным управлением, причем выходы каждого разряда

первой и второй пар регистров соединены через схемы совпадения с, собственными входами, а также со входами трехвходовых сумматоров, выходы которых подключены на входы каждого разряда соответственно второй и первой пары регистров суммы и регистров переносов.

2.Устройство по п. 1, отличающееся тем, что с целью расширения его логических возможностей, выходы каждого разряда одной или

обеих пар регистров соединены также со схемами совпадения, выходы которых подключены ко входам каждого разряда другой или других пар регистров, причем к указанным схемам совпадения и трехвходовым сумматорам

подсоединены управляющие шины, сигналы которых разрешают работу схем, необходимых для выполнения нужной операции.

j:

13

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU330451A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Устройство для умножения | 1978 |

|

SU767761A1 |

| Устройство для суммирования | 1978 |

|

SU955036A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для ускоренного умножения | 1977 |

|

SU714395A1 |

| ПАТЕНТНО. *- ТЬХййЭеОКАЯ '" ИБЛЯОТ]Р. П. Жукоэский | 1970 |

|

SU281004A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

3 3

тм

I -I I

О--,

TJ

Cf C2

Авторы

Даты

1969-01-01—Публикация