Это достигается тем, что в предлагаемое устройство введен коммутатор записи байтов второго операнда, вход которого соединен с регистром результата, а выход соединен со вторым входом регистра второго операнда, второй вход коммутатора записи байтов второго операнда соединен со счетчиком адреса первого операнда.

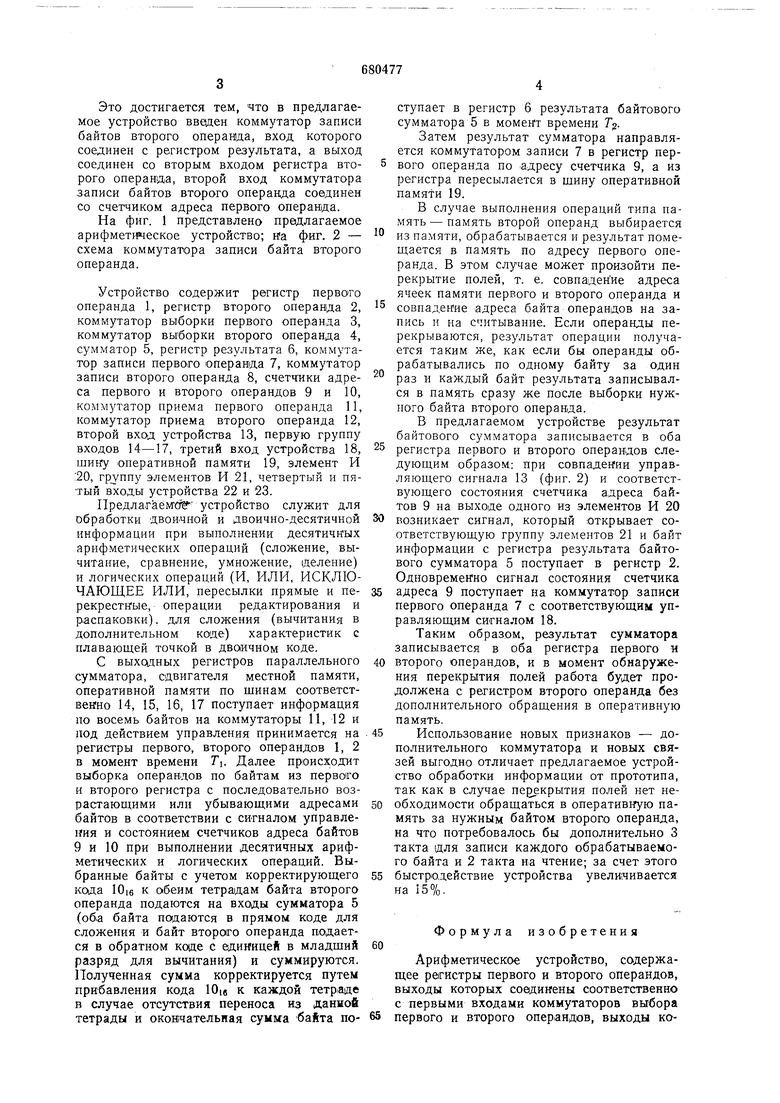

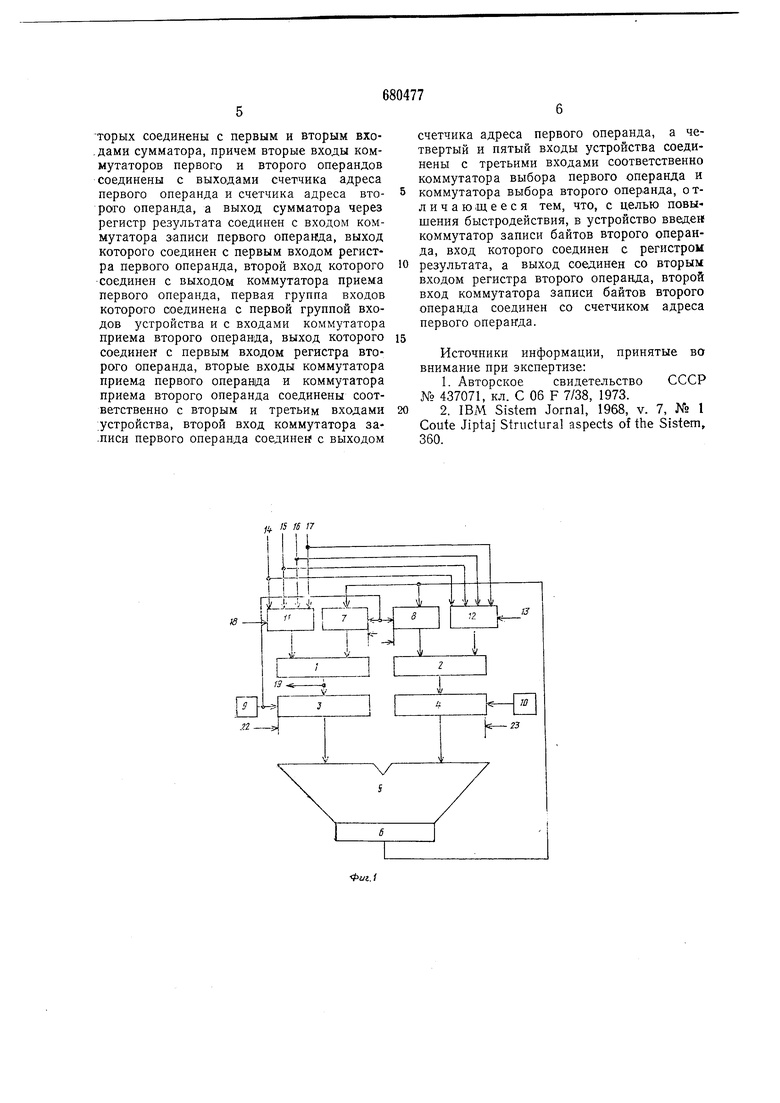

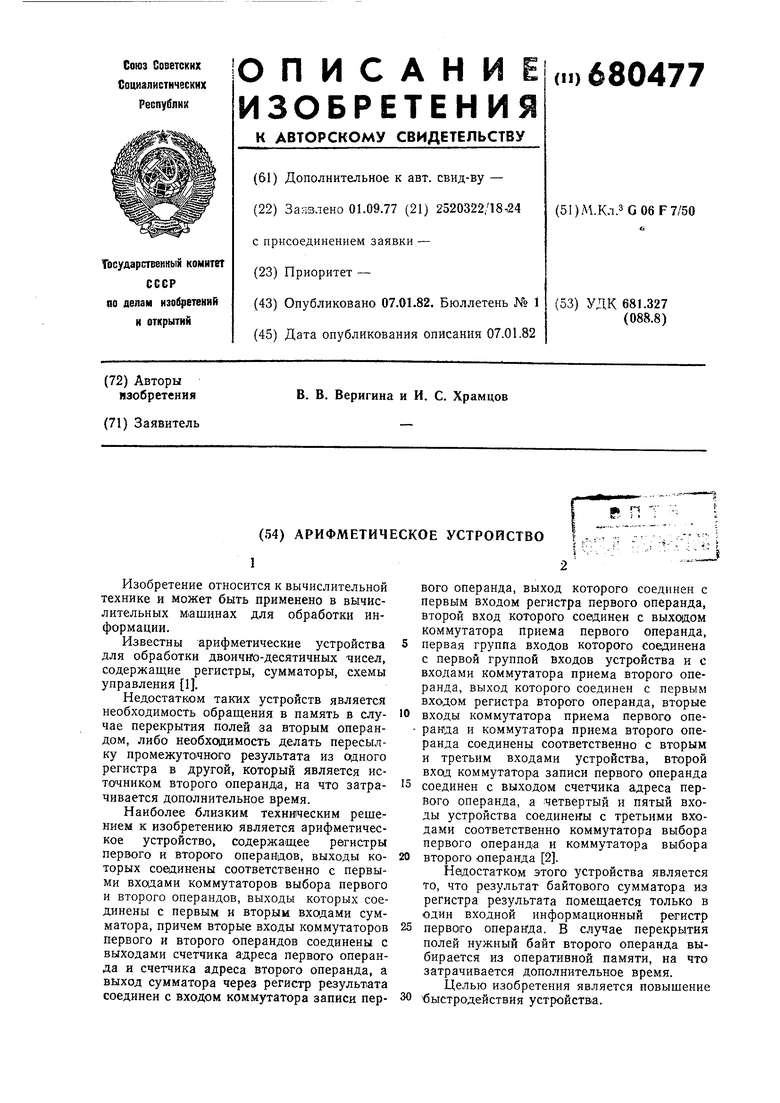

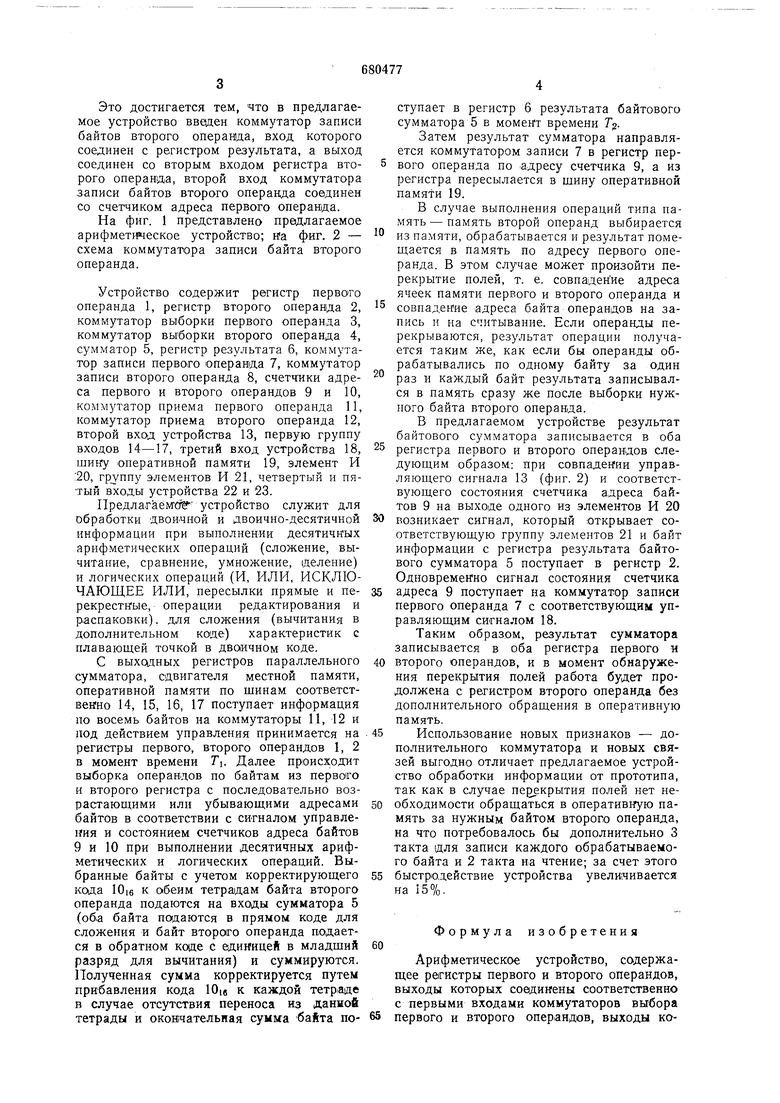

На фиг. 1 представлено предлагаемое арифметическое устройство; на фиг. 2 - схема коммутатора записи байта второго операнда.

Устройство содержит регистр первого операнда 1, регистр второго операнда 2, коммутатор выборки первого опер-анда 3, коммутатор выборки второго операнда 4, сумматор 5, регистр результата 6, коммутатор записи первого операнда 7, коммутатор записи второго операнда 8, счетчики адреса первого и второго операндов 9 и 10, коммутатор приема первого операнда 11, коммутатор приема второго операнда 12, второй вход устройства 13, первую группу входов 14-17, третий вход устройства 18, шину оперативной памяти 19, элемент И :20, элементов И 21, четвертый и пятый входы устройства 22 и 23.

Предлагаемо устройство служит для обработки двоичной и двоично-десятичной информации при выполнении десятичных арифметических операций (сложение, вычитание, сравнение, умножение, деление) и логических операций (И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, пересылки прямые и перекрестные, операции редактирования и р.аспаковки). для сложения (вычитания в дополнительном коде) характеристик с плавающей точкой в двоичном коде.

С выходных регистров параллельного сумматора, сдвигателя местной памяти, оперативной памяти по шинам соответственно 14, 15, 16, 17 поступает информация по восемь байтов на коммутаторы 11, 12 и под действием управления принимается на регистры первого, второго операндов 1, 2 в момент времени TI. Далее происходит выборка операндов по байтам из первого и второго регистра с последовательно возрастающими или убывающими адресами байтов в соответствии с сигналом управления и состоянием счетчиков адреса байтов 9 и 10 при выполнении десятичных арифметических и логических . Выбранные байты с учетом корректирующего кода 10i6 к обеим тетрадам байта второго операнда подаются на входы сумматора 5 (оба байта подаются в прямом коде для сложения и байт второго операнда аодается в обратном коде с единицей в младщий разряд для вычитания) и суммируются. 11олученная сумма корректируется путем прибавления кода Юц к каждой тетр.аде в случае отсутствия переноса из данной тетрады и окончательная сумма байта поступает в регистр 6 результата байтового сумматора 5 в момент времени Ту.

Затем результат сумматора направляется коммутатором записи 7 в регистр первого операнда по адресу счетчика 9, а из регистра пересылается в шину оперативной памяти 19.

В случае выполнения операций типа намять - память второй операнд выбирается из памяти, обрабатывается и результат помещается в память по адресу первого операнда. В этом случае может произойти перекрытие полей, т. е. совпадение адреса ячеек памяти первого и второго операнда и совпадение адреса байта операндов на запись и на считывание. Если операнды перекрываются, результат операции получается таким же, как если бы операнды обрабатывались по одному байту за один раз и каждый байт результата записывался в память сразу же после выборки нужного байта второго операнда.

В предлагаемом устройстве результат байтового сумматора записывается в оба регистра первого и второго операндов следующим образом: при совпадении управляющего сигнала 13 (фиг. 2) и соответствующего состояния счетчика адреса байтов 9 на выходе одного из элементов И 20 возникает сигнал, который открывает соответствующую группу элементов 21 и байт информации с регистра результата байтового сумматора 5 поступает в регистр 2. Одновременно сигнал состояния счетчика адреса 9 поступает на коммутатор записи первого операнда 7 с соответствующим управляющим сигналом 18.

Таким образом, результат сумматора записывается в оба регистра первого и второго операндов, и в момент обнаружения перекрытия полей работа будет продолжена с регистром второго операнда без дополнительного обращения в оперативную память.

Использование новых признаков - дополнительного коммутатора и новых связей выгодно отличает предлагаемое устройство обработки информации от прототипа, так как в случае перекрытия полей нет необходимости обращаться в оперативную память за нужным байтом второго операнда, на что потребовалось бы дополнительно 3 такта для записи каждого обрабатываемого байта и 2 такта на чтение; за счет этого быстродействие устройства увели1чивается на 15%.

Формула изобретения

Арифметическое устройство, содержащее регистры первого и второго операндов, выходы которых соединены соответственно с первыми входами коммутаторов выбора первого и второго операндов, выходы которых соединены с первым и вторым вхо-Дами сумматора, причем вторые входы коммутаторов первого и второго операндов соединены с выходами счетчика адреса первого операнда и счетчика адреса второго операнда, а выход сумматора через регистр результата соединен с входом коммутатора з-аписи первого операнда, выход которого соединен с первым входом регистра первого операнда, второй вход которого соединен с выходом коммутатора приема первого операнда, первая группа входов которого соединена с первой группой входов устройства и с входами коммутатора приема второго операнда, выход которого соединен с первым входом регистра второго операнда, вторые входы коммутатора приема первого операнда и коммутатора приема второго операнда соединены соответственно с вторым и третьим входами устройства, второй вход коммутатора за.писи первого операнда соединен; с выходом

счетчика адреса первого операнда, а четвертый и пятый входы устройства соединены с третьими входами соответственно коммутатора выбора первого операнда и

коммутатора выбора второго операнда, отличающееся тем, что, с целью повышения быстродействия, в устройство введен коммутатор записи байтов второго операнда, вход которого соединен с регистром

результата, а выход соединен со вторым входом регистра второго операнда, второй вход коммутатора записи байтов второго операнда соединен со счетчиком адреса первого операкда.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 437071, кл. С 06 F 7/38, 1973.

2,IBM Sistem Jornal, 1968, v. 7, № 1 Coute Jiptaj Structural aspects of the Sistem, 360.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

Авторы

Даты

1982-01-07—Публикация

1977-09-01—Подача