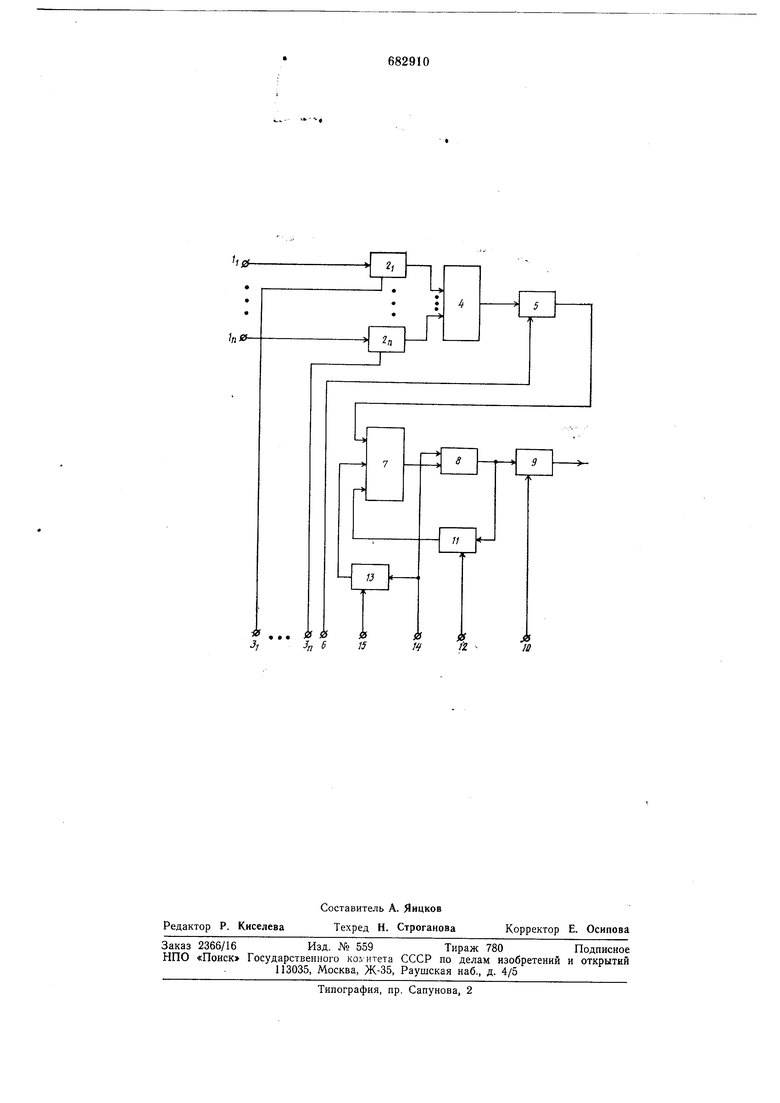

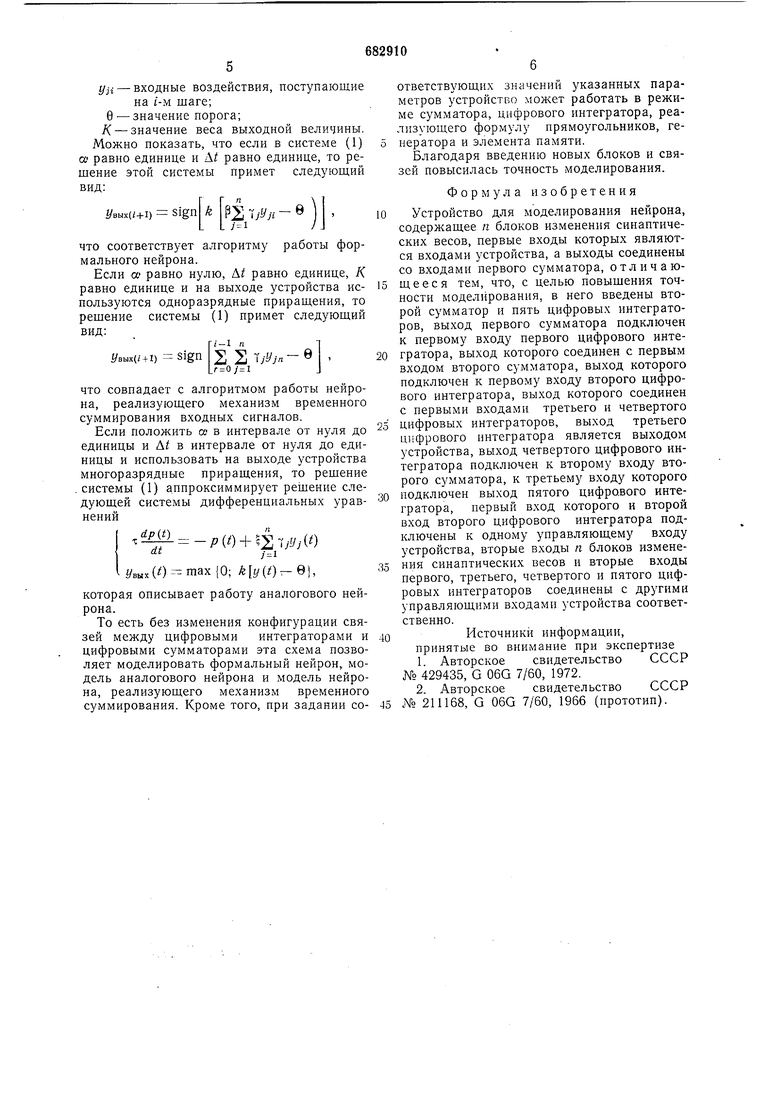

Структурная схема устройства представлена на чертеже.

Устройство содержит входы ,..., In, каждый из которых может быть как возбуждающимТ т-ак и тормозящим; п блоков изменения синаптических весов 2i,..., 2„, выполненные в виде цифровых интеграторов, управляющие входы 3i,..., Зп, подключенные к входам подынтегральных функций (вторые входы) цифровых интеграторов 2, ..., 2п, первый сумматор 4, осуществляющий пространственное суммирование, входных сигналов, первый цифровой интегратор 5, вход 6, соединенный со вторым входом интегратора 5 и управляющий изменением веса пространственного суммирования, второй сумматор 7, второй цифровой интегратор 8, третий цифровой интегратор 9, представляющий собой выходной блок устройства и реализующий пороговый эффект, вход 10, который подключен к второму входу цифрового интегратора 9 и управляет изменением веса выходной величины, четвертый цифровой интегратор 11, вход 12, который подключен ко второму входу интегратора 11 и управляет изменением длительности временного суммирования, пятый цифровой интегратор 13, вход 14, который соединен с входами переменной интегрирования (первые входы) интеграторов 8, 13 и управляет изменением независимой переменной, вход 15 который подключен к второму входу интегратора 13 и управляет изменением значения порога.

Для задания режима функционирования устройства на его управляющие входы 3i, ..., Зп, 6, 12, 10 и 15, подключенные к входам регистров подынтегральных функций цифровых интеграторов 2i, ..., 2„, 5, 11, 9 и 13, подаются соответствующие значения синаптических весов, веса пространственного суммирования, длительности временного суммирования, веса выходной величины и порога, которые записываются и хранятся в регистрах подынтегральных функций соответствующих интеграторов. После этого на специальный вход 14 подаются значения приращений независимой переменной. С данного момента устройство готово к приему входных сигналов, поступающих с выходов других элементов, объединенных с этим элементом в нейроноподобную сеть, либо от датчиков информации, моделирующих рецепторные нейроны. Входные сигналы через входы Ij, ..., 1„ устройства поступают на входы переменных интегрирования цифровых интеграторов 2i, ..., 2п, в которых умножаются на соответствующие значения синаптических весов, хранящихся в регистрах подынтегральных функций этих блоков. Полученные произведения с выходов цифровых интеграторов 2i, ..., 2„ поступают на входы 4. Сумматор 4 осуществляет суммирование поступающих на его входы произведений и передает полученную сумму на

вход переменной интегрирования интегратора 5, в котором эта сумма умножается на соответствующее значение веса пространственного суммирования, записанное в регистре подынтегральной функции этого интегратора. Полученное произведение с выхода интегратора 5 поступает на первый вход сумматора 7, на третий вход которого с выхода интегратора 13 Подается произведение значений порога и независимой переменной, причем значение порога хранится в регистре подынтегральной функции интегратора 13, а значение независимой переменной подается с управляющего входа 14. В этот

же момент значение результата временного суммирования, полученное на предыдущем шаге (на первом шаге оно равно нулю) и хранящееся в регистре подынтегральной функции 8, умножается в нем на значение

независимой переменной (задаваемое с специального входа 14) и поступает на вход переменной интегрирования цифрового интегратора И, в котором дополнительно умножается на значение длительности временного суммирования (записанное в регистре подынтегральной функции интегратора 11) и подается на второй вход сумматора 7. Результат временного суммирования, полученный на данном шаге в сумматоре 7, поступает на вход приращений подынтегральной функции интегратора 8, в котором суммируется со значением временной суммы, полученной на предыдущем шаге. После суммирования значение временной суммы в следующем шаге умножается на приращение независимой переменной. Полученное произведение с выхода интегратора 8 поступает на вход переменной интегрирования интегратора 9, в котором умножается на значениё веса выходной величины, хранящееся в регистре подынтегральной функции этого интегратора, и полученное произведение сравнивается с нулем. Если это произведение больше нуля, то на выходе устройства

появляется выходной сигнал. Если произведение отрицательное, то сигнал на выходе отсутствует.

Процессы, происходящие в устройстве, описываются следующей системой разностных уравнений:

Ai/(/4i) - -yAf + Р 2 ijyji - ®Д

(1)

max{Q- г/вых(М) Д Ai/.A,

значение длительности временного

суммирования;

значение временной суммы, полученной в предыдущем шаге;

приращение независимой переменной;значение веса пространственного

суммирования; синаптические веса; yji - входные воздействия, поступающие на 1-м шаге; 6--значение порога; К - значение веса выходной величины. Можно показать, что если в системе (1) со равно единице и At равно единице, то решение этой системы примет следуюш,ий вид: Г 1 г/вых(/+1) sign k 2 иУл - ® L L что соответствует алгоритму работы формального нейрона. Если го равно нулю, Д равно единице, К равно единице и на выходе устройства используются одноразрядные прираш,ения, то решение системы (1) примет следующий вид: t/Bb,x(/ + I) sign 2 S в что совпадает с алгоритмом работы нейрона, реализующего механизм временного суммирования входных сигналов. Если положить се в интервале от нуля до единицы и Д в интервале от нуля до единицы и использовать на выходе устройства многоразрядные приращения, то решение . системы (1) аппроксиммирует рехнение следующей системы дифференциальных уравнений- -p(} + ±ljyj(t} Увь.х(0-- тах{0; (0г-в), которая описывает работу аналогового нейрона. То есть без изменения конфигурации связей между цифровыми интеграторами и цифровыми сумматорами эта схема позволяет моделировать формальный нейрон, модель аналогового нейрона и модель нейрона, реализующего механизм временного суммирования. Кроме того, при задании соответствующих значении указанных параметров устройство может работать в режиме сумматора, цифрового интегратора, реализующего формулу прямоугольников, генератора и элемента памяти. Благодаря введению новых блоков и связей повысилась точность моделирования. Формула изобретения Устройство для моделирования нейрона, содержащее п блоков изменения синаптических весов, первые входы которых являются входами устройства, а выходы соединены со входами первого сумматора, отличающееся тем, что, с целью повышения точности моделирования, в него введены второй сумматор и пять цифровы.ч интеграторов, выход первого сумматора подключен к первому входу первого цифрового интегратора, выход которого соединен с первым входом второго сумматора, выход которого подключен к первому входу второго цифрового интегратора, выход которого соединен с первыми входами третьего и четвертого цифровых интеграторов, выход третьего цифрового интегратора является выходом устройства, выход четвертого цифрового интегратора подключен к второму входу второго сумматора, к третьему входу которого подключен выход пятого цифрового интегратора, первый вход которого и второй вход второго цифрового интегратора подключены к одному управляющему входу устройства, вторые входы п блоков изменения синаптических весов и вторые входы первого, третьего, четвертого и пятого цифровых интеграторов соединены с другими управляющими входами устройства соответственно. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 429435, G 06G 7/60, 1972. 2.Авторское свидетельство СССР № 211168, G 06G 7/60, 1966 (прототип).

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Устройство для моделирования нейрона | 1978 |

|

SU767788A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| Устройство для моделирования нейрона | 1988 |

|

SU1596356A2 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1479944A1 |

| Устройство для моделирования нейронных ансамблей | 1980 |

|

SU903910A1 |

| Модель адаптивного нейрона | 1978 |

|

SU765823A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

IS

SS 0

3„ 6

3i

0 if.

Js

ЩIZ

la

Авторы

Даты

1979-08-30—Публикация

1977-05-23—Подача