Изобретение относится к бионике и вычислительной технике и может йлть использовано в качестве элемента адаптивных нейронных сетей, для моделирования биологических процессов, в-Устройств ах распознавания образов, а также-в качестве структур, предназначенных для решения систем алгебраических уравнений, дифференциальных уравнений, задач исследования операций, краевых задач теории поля. Известно устройство, моделирующее адаптивные свойства нервных клеток, содержащее блоки моделирования синап са, адаптивный сумматор, схему сравнения, преобразователь напряжения в чдстоту, блок управления смнапсом формирователь выходных сигналов, бло формирования порога, блок управления ре истивным элементом, находящимся, в блоке моделирования синапса, цепь адаптации, по выходному сигналу, содержащую 1-й интегратор, источник питания и цепь, моделирующую увеличение активности нейроподобного эле мента в зависимости от частоты его возбуждения, построенную на первом и втором интеграторах l3 . Однако устройства, основанные на элементах аналоговой техники имеют слишком малую стабильность параметров, особенно в зависимости от времени и температуры, а устранение этого значительно увеличивает стоимость элемента. Кроме того, такие элементы три их совместной работе с ЭВМ, трёбуют дополнительных дорогостоящих преобразователей аналого-цифрового и цифроаналогового типа.. Наиболее близким техническим решением к изобретению является модель адаптивного нейрона, содержащая управляющий вход, который подключен к первому входу первого блока временного сумглирования, к входу независи.мой переменной выходного интегратора и к первому входу блока адаптации, и п входов, каждый из которых подключен к первому входу соответствующего блока моделирования синапса, выход кото.рого соединен с соответствующим входом первого блока пространств нного . суммирования, выход которого подключен к второму входу первого блока временного суммирования, выход которого соединен с прямлм входом блока сравнения с порогом, а его выход подключен

к входу подинтегральной функции выходного интегратора, выход которого является выходом модели 2), Кроме этого, модель содержит цифровые сумматоры, инте граторы и ряд специальных управляющих входов.

Согласно современным представлениям нервной клетке приписывается изве.стная автономность, выражающаяся в оптимизации энергетических процессов и в пластичности, которую связывают с изменением весов синапсов в процессе жизнедеятельности нервной клетки. На формирование пластических изменений в синапсах оказывает влияние выходная активность самого нейрона.Полагают, что обратная связь в нейроне

.может управлять скоростью пластических изменений в синапсах в зависимости не только от внешней активности синапсов, обусловленной внэиними для нейрона, воздействиями, но и от выходной активности нейрона. Степень участия каждого синапса при этом определяется величиной постсинаптического потенциала, генерируемого данным синапсом в момент возникновения ответа. Легко видно, что подобные свойства не нашли свои отражения в известной модели нейрона. Другой погрешностью модели является большое количество специальных входов,.

Цель изобретения - повышение точности моделирования, .

Достигается это тем, что в модель адаптивного нейрона, содержащую первый блок временного суммирования . первый вход которого подключен к управляющему входу, модели, соединенному с входом независимой переменной выходного интегратора и первым входом блока адаптации, блок моделирования синапса, выход которого соединен с соответствующим входом первого блока пространственного суммирования, выход которого подключен к второму входу первого блока временного суммирования выход которого соединен с первым входом блока сравнения, а выход последнего подключен к входу под1(нтегральной функции выходного интегратора, выход которого является выходом модели, введены два блока управления пластичностью, блок -коррекции, лторой блок пространственного суммирования, второй блок временного суммирования и блоки умножения, первые входы которых соединены с соответствующими входами мбдели, управляющий вход которой подкл1рчен к первому входу второго блока временного суммирования, выход

-которого соединен с вторым входом

. блока сравнения и с входом .первого .блока управления пластичностью, выход которого подключен к первомувходу блока коррекции и к вторым входам блоков умножения, выходы которых подключены соответственно к входам второго блока пространственного суммирования, выход которого соединен с вторым входом второго блока временного суммирования, выход первого блока временного суммирования подключен к второму входу блока коррекции, выход которого соединен с вторым входом блока адаптации, выход которого подключен к третьему входу блока коррекции и к входу второго блока управления пластичностью, выход которого соединен с вторыми входами блоков моделирования синапса.

Кроме того, блок управления пластичностью содержит первый интегратор, вход независимой переменной которого подключен к входу блока управления пластичностью, выход первого интегратора подключен к входу независимой переменной второго интегратора, выход которого соединен с входом подинтегральной функции первого интегратора, с инверсным входом под{ нтегральной функции второго интегратора и с выходом блока управления пластичностью. Помимо этого, блок коррекции содержит первый интегратор, вход независимой переменной которого подключен к первому входу блока и к входу подинтегральной функции второго интегратора, быход которого соединен с одним входом первого сумматора другой вход .которого подключен к выхду первого интегратора, вхо подинтегральной функции которого соединен с входом независимой переменной второго интегратора и с вторым входом блока коррекции; выход первого сумматора подключен к входу независимой деременной третьего интегратора и к входу под4 1нтегральной функции четвертого интегратора,выход которого соединен с одним входом второго сумматора, а его другой вход подключен к выходу третьего интегратора, вход подынтегральной функции которого соединен с входом независимой переменно четвертого интегратора и с третьим входом блока коррекции, выход второго сумматора подключен к выходу блока коррекции.

Каждый, блок умножения и каждый блок моделирования синапса состоит и 4-х цифровых интеграторов и двух цифровых сумматоров, соединенных так, что вход независимой переменной первого интегратора соединен с вторым ёходом. Клока, а вход подинтегральной функции соединен с первым входом блока, вход независимой переменной второго интегратора соединен с первым входом блока, а вход подинтегрзльнрй функции соединен с вторым входом б.лока, первый и второй входы первого сумматора соединены соответственно с выходами первого и второго интегратора, вход независимой переменной третьего интегратора соединен с выходом первого сумматора, а вход подинтеграпьной функции соединен с первым . входом блока, вход независимой переменной четвертого интегратора соединэн с первым входом блока, а аход подинтегральной функции соединен с . выходом первого сумматора, первый и второй входы второго сумматора соединены соответственно с выходами третьего и четвертдго интеграторов, выход второго сумматора соединен с выходом блока, каждой из блоков временного сумг ирования и блок адаптаци состоит из трех цифровых интеграторов и одного цифрового сумматора, соединенного так, что входы независимой переменной первого и второго интеграторов подключены к первому входу блока, вход подынтегральной функции первого интегратора соединен с вторым входом блока, инверсный вход подинтегральной функции второго интегратора соединен с выходом третьего интегратора, являющимся выходом блока, первый и второй входы сумматора соединены соответственно с выходами первого и второго интеграторов, а выход этого сумматора -соединен с входом независимой переменной третьего интегратора, а регистр подг интегральной функции которого занесена соответствующая постоянная величина.

Сущность изобретения заключается в том, что в модель введена обратная связь между выходом, первого блока, временного суммирования и вторыми входами- блоков моделирования синапса образованная последовательно соединенными блоком коррекции, блоком адатации и вторым блоком управления пластичностью. При неизменной интенсивности входного воздействия эта связь обеспечивает адаптацию нейрона по выходу, заключающуюся в устранени отклонения величины сигнала на выходе первого блока временного суммирования от величины порога путем изменения весов синапсов Т,е. за счет активного-обучения

нейрона. Оптимизация энергетических процессов в нейроне заключается в. .обеспечении в режиме адаптации минимума целевых функций и осуществляется за счет соответствующего изменения величины порога. Требуемую вели;чину порога вырабатывают последовательно соединенные второй блок пространственного сумтимрования, второй блок временного суммирования и первый блок управления пластичностью, выход которого соединен с вторыми .входами блока перемножения, С выхода второго блока управления пластичностью в блок коррекции вводится величина обратная величине порога. Выход второго блока временного суммирования, вырабатывающего значение величины порога, соединен с инверсным входом блока сравнения с порогом, за счет чего осуществляется плавное падение частоты выдачи приращений , на выходе устройства и режиме адаптации.

Блок коррекции обеспечиваем получение по текущим значениям сигнала на выходе блока адаптации и отношения величины сигнала на выходе первого блока временного суммирования к величине порога управляющего воздействия

0 отрабатываемого блоком адаптации со . скоростью, определяемой постоянной времени блока адаптации.

Выходной сигнал блока адаптаидии преобразуется вторым блоком управле5ния пластичностью в величину ему обратную, которад и изменяет вес синапсов .

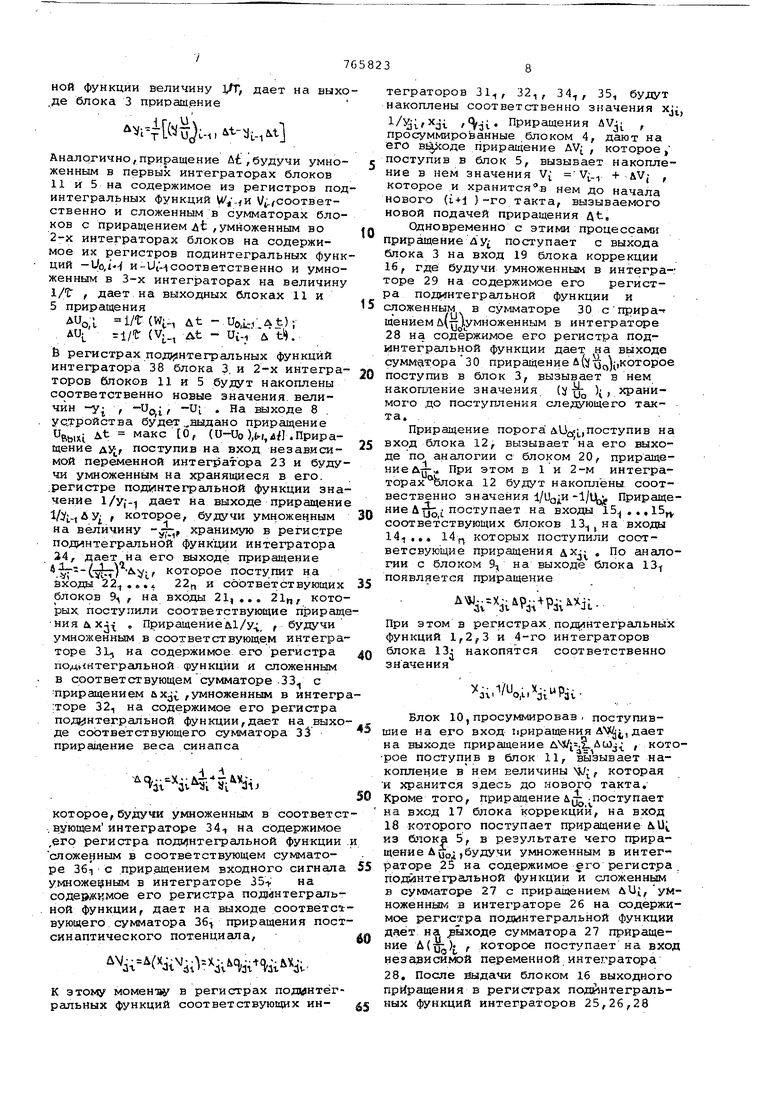

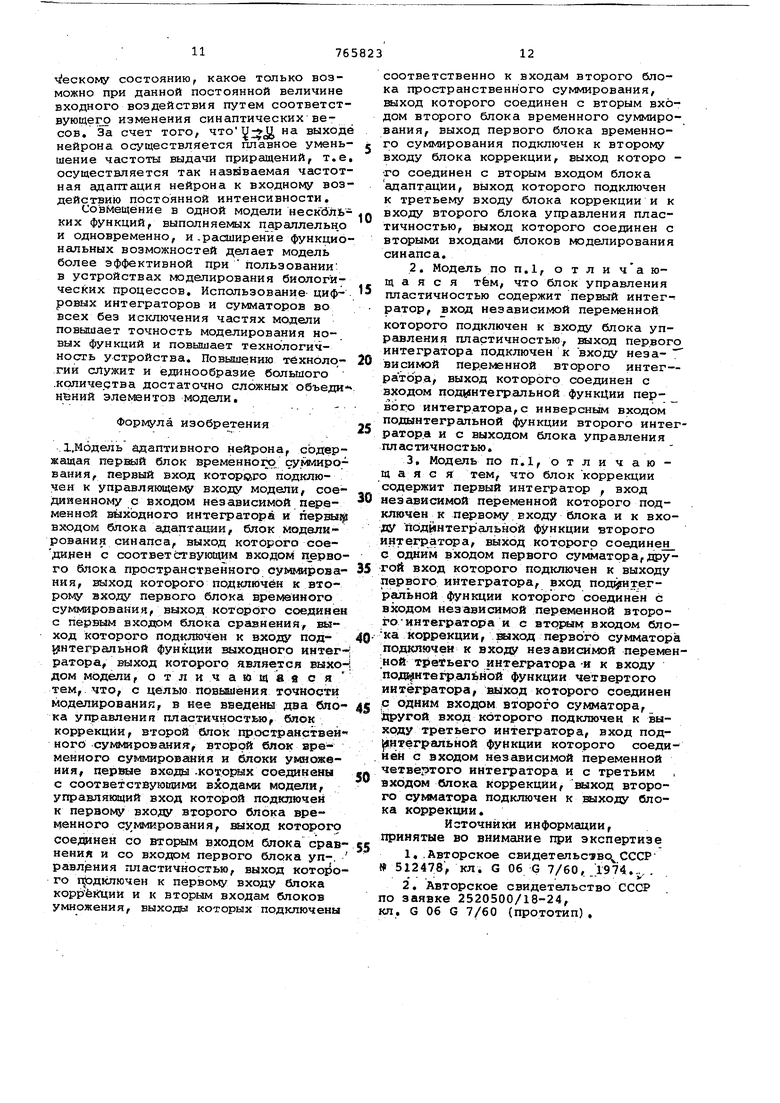

На чертеже дана схема моделирования адаптивного нейрона.

0

Она содержит входы устройства 1, ,,.1п, вход 2, управляющий изменением длительности периода возбуждения, блок адаптации 3, первый блок 4 пространственного суммирования пер5вый блок 5 временного суммирования, блок 6 сравнения, выходной интегратор 7, выход устройства 8, блоки 9, , 9,j...9n моделирования синапса, рторой блок 10 пространственного сумми0рования, второй блок 11 временного суммирования, первый блок 12 управления пластичностью, блоки 13,, 130 .. 13, перемножения, первый вход 14 и второй вход 15 соответствующего блока 13 , блок коррекции 16, имекяций пер5вый вход l7 второй вход 18 и третий вход 19, второй блок 20 управле;ния пластичностью, первый вход 21, и второй вход 22 соответствующего бло-ка 9т , первый интегратор 23 к второй

0 интегратора 24 блока 20, первый интегратор 25, второй интегратор 26, первый сумматор 27, третий интегратор 28, четвертый интегратор 29, второй сумматор 30 блока 16, первый

5 интегратор , второй интегратор 32|, первый сумматор 33 третий интегратор 34, четвертый интегратор 35i и второй сумматор 36, блока 9, , первый интегратор 37, второй интегратор 38,

0 третий интегратор 39 и сумматор 40 блока 3.

Функционирование устройства осуществляется следующим образом. Пусть в i-OM также на входы 1, Ij ... If по5даны соответствующие приращения Лхл, а в блоки 3, Ilj5 и 7 подано с входа 2 приращение At, которое, будучи умноженным в интеграторе 37 на содержимое его регистра под{4нтегральной функции (yU/4j)t-i и сложенным в сумматоре

0 40 с приращением fit, умноженным в интеграторе 38 на содержимое его регистра подынтегральной функции и умноженным в интеграторе 39 на содер.жащуюся в его регистре подинтеграль5ной функции величину /Г, дает на выхо .де блока 3 приращение aVi4ton-JtM.-i)i.-i Аналогично,приращение Д будучи умноженным в первых интеграторах блоков 11 и 5 на содержимое из регистров под интегральных функций /,соответственно и сложенным в сумматорах блоков с приращением At ,умноженным во 2-х интеграторах блоков на содержимое их Езегистров подинтегральных функ ций -Uo,- и-ийсоответственно и умноженным в 3-х интеграторах на величину i/t f дает на выходных блоках 11 и 5 приращения i/f (Wi. At - Uo,i.-,- At); i/f (V;. At - Ui-, л t. Ь регистрах под1 нтегральных функций интегратора 38 блока 3. и 2-х интеграторов блоков 11 и 5 будут накоплены соответственно новые значения, величин -у| , -Ujj, -Ut . На илкоде 8 устройства будет выдано приращение At макс О, (инио)1,А.Приращение ду, поступив на вход независи мой переменной интегратора 23 к будучи умноженным на хранящиеся в его. .регистре подынтегральной функции значение 1/У,-- дает на выходе приращение /.;,„, Л У г которое, будучи умноженным на величину -, хранимую в регистре подинтегральной функции интегратора 24, дает на его выходе приращение ((|г7) которое поступит на Ёходы 22,,.X 22f, и соответствующих блоков 9-1 , на входы 21, ... которых, поступили соответствующие приращ ниялх.-( , ПриращениеЛ1/У..;, , будучи умноженньзм в соответствующем интегра торе 3L, на содержимое его регистра пoмv нтeгpaльнoй функции и сложенным в соответствующем сумматоре 33 с приращением ax-j ,умноженным в интегр торе 32., на содержимое его регистра под нтегральной функции,дает на выхо де соответствующего су чматора ЗЗ прираидение веса синапса . которое,будучи умноженным в соответст .вующеминтеграторе 341 на содержимое ,его регистра под«1нтегральной функции споже5}ным в соответствующем сумматоре Збт с прир.ащением входного сигнала умноже ным в интеграторе 35V на содержимое его регистра подантеграпьной функции, дает на выходе соответст вующего сумматора Зб| приращения пост синаптического потенциала, . К этому момен-ау в регистрах пoд нтёгральных функций соответствующих интеграторов 31, 32,, 34,, 35, будут накоплены соответственно значения xj{, l/yj;,X.ji ,. Приращения AVjj , просуммированные блоком 4, дают на его В5арсоде приращение ДУ , которое, поступив в блок 5, вызывает накопление в нем значения V{ ., + &V,- , которое и хранится в нем до начала нового (i+1 )-го такта, вызываемого новой подачей приращения At, Одновременно с этими процессами приращение ау поступает с выхода блока 3 на вход 19 блока коррекции 16, где будучи умноженным в интеграторе 29 на содержимое его регистра подинтегральной функции и сложенным в сумматоре 30 сприра-f щением й(-г умноженным в интеграторе 28 на содержимое его регистра подинтегральной функции дает на выходе сумматора 30 приращение А{ yj,KOTOpoe поступив в блок 3, вызывает в нем накопление значения (V ь )(; хранимого до поступления следующего такта. . Приращение порога , поступи в на вход блока 12, вызываетна его выходе по аналогии с блоком 20, приращение д-д-.. При этом в 1 и 2-м интеграторах Ьлока 12 будут накоплены соотвественно значения l/UQ n-1/1 Приращение Д поступает на входы 15..,15, соответствующих блоков 13 , на входы 14,,,, 14р которых поступили соответсвующие приращения AXj , По аналогии с блоком 9 на выходе блока 13 появляется приращение - dx VP l JlПри этом в регистрах, под лнтегральных функций 1,2,3 и 4-го интеграторов блока 13- накопятся соответственно значения ..u jiUPai. Блок 10, просуммировав , поступившие на его вход 11риращекия A(j,, дает на выходе приращение .AUj , которое поступив в блок 11, вызывает накопяен.и.е внем величины 3J{, которая И хранится здесь до нового такта. Кроме того, приращение л поступает на вход 17 блока коррекции, на вход 18 которого поступает приращение Mli. КЗ бипока 5, в результате чего приращение А иоД )бУДУЧ умноженным в интеграторе 25 на содержимое его регистра . подинтегральной Функции и сложенным в сумматоре 27 с прираи ением uUt,уМноженным 2 интеграторе 26 на содержимое регистра подинтегральной функции дает на ыходе сумматора 27 приращение Д{и); f которое поступает на вход независинюй переменной интет.-ратора 28. После йыдачи блоком 16 выходного прИращения в регистрах подынтегральных функций интеграторов 25,26,28 и 29 сказываются накопленными знач ния Ui,ij5,,(4)i. соответственно. Приращение Uj , ЛОоД f поступи соответственно на прямой и инверсн входл блока 6, вызывают на его вых де появление приращения A(U-tb)u.i торое поступив в выходной .интеграт 7, вызывает накопление в нем значе ния (U-Uo )i Л которое и хранится д .наступления следующего такта. Разностный алгоритм работы моде записивается следующим образом. viTfou-oV. ЬМ;: Х|Г гЛ%Ч %Ч аЧ 41 AVJo,,M i А л1 З Ра1ГРзг 1 .г-де ,ьиДЛЧз1Л / й,.1, , приращения на выходе соот ственно блоков 3,5,4,9 сум матора 33ч блоков 20,11,10 12 первого сумматора соотв ствующих блоков 13 . B-i-M такте; -величина периода возбужденного на входе 2; -приращение входного сигнала j входа в 1-м такте; Т,/, - содержимое регистров под нтегральной функции соответсвенно интегратора 39 и трех интеграЮроз блоков 5 и 11; / ,, - содержимое регистров поД L-иЧм интегральных функций ин-и{.,,- теграторов 37, 38-го и чл -11 BTODOro интегоатопоп fino t.-i)4i--i ка 56, интегратора 24, 1 и 2-го интеграторов олока 11,2-го интегратора блока 12 в i-OM такте, X.J{,V4,y:f содержимое регистров под -г нтегральных функций, соот di) ветственно интеграторов 31, , 34, , 1 и 3-го интеграторов блока 13, , 35LJ (вес j-ro синапса) 32j и 23 и 4-го интегратора блока 13,, 1-го интегратора блока 12 в 1-м такте. от алгоритм вытекает из следуюистемы уравнений Шеннона: ) WQ (Vdt-Udt) Vi-d l J dli-.dv dUo-i/f(4}jdt-Uodt) dXW-Idu):; 3-1 du); -Ч та система уравнений в свою очевытекает из следующей система: Tdv/dt V-VTL ° rtf. 1 1Ур,а1Л. ри условии постоянства входного ействия и tiiT система имеет решакоторое с течением времени прит к достаточной точности к ратву и U0 у |. х ля модели нейрона-можно построить вые функции, соответствукицие приннаименьшего взаимодействия , инципу оптимального воздействия Fb-iu-Uol;M -v| они имеют минимум при значениях менных, соответствующих решению екы дифференциальных уравнений, i$-t/3 -r--U«U, ак модель нейрона, функционируюпо приведенному выше разностногоритму, стремится с течением ни к самому наинизшему энергетич1ескому состоянию, какое только возможно при данной постоянной величине входного воздействия путем соответствующего изменения синаптических весов. За счет того, ЧТОУ: на выходе нейрона осуществляется плавное уменьшение частоты выдачи приращений, т.е. осуществляется так называемая частотная адаптация нейрона к входному воздействию постоянной интенсивности.

Совмещение в одной модели нескТЗльких функций, выполняемых п араллельн.о и одновременно, и.расширение функциональных возможностей делает модель более эффективной при пользовании в устройствах моделирования биологических процессов. Использование- циф ровых интеграторов и сумматоров во

всех без исключения частях модели повышает точность моделирования но-, вых функций и повышает технблогичносгь устройства. Повышению техноло гии служит и единообразие большого .капичертва достаточно сложных объеди нйний элементов модели,

изобретения

.1,Мбдель адаптивного нейрона, содержащая першлй блок временного суквлирования, первый вход которого подключен к управляющему входу модели, соединeннo y с входом независимой перемен ной выходного интегратора и первы взюдом блока адаптации, блок модопкрования синапса, выход которого Соединен с соответствующим входом первого блока пространственного суммирования, выход которого подключён к второму BXOW первого блока временного суладирования, выход которого соединен с первым входом блока сравнения, выход которого подключен к входу под интегральной функции выходного интегратора, выход которого является рыхоН дом модели, о тли ч а и щ а я о я тем, что, с целью повышения точности моделирования, в иее введены два блока управления пластичностью, блок коррекции, второй блок пространствен ного суммировш1ия, второй блок временного суммирования и блоки умнхжения, перщле входам-которых соединены с соответствующими входами модели, управляющий вход которой подключен к первому входу второго блока временного суммирования, выход которого

соеданен со ВТОЕДЛМ входом блока сравнения и со входом перрого блока уп-, пластичностью, выход которого грдключен к первому входу блока коррёвгций и к вторым входам блоков умножения, выходы которых подключены

соответственно к входам второго блока пространственного суммирования, клход которого соединен с вторым входом второго блока временного суммирования, выход первого блока временного суммирования подключен к второму входу блока коррекции, выход которо го соединен с вторым входом блока адаптации, выход которого подключен к третьему входу блока коррекции и к входу второго блока управления пластичностью, выход которого соединен с вторыми входами блоков моделирования синапса.

2.Модель по П.1, о т л и ча ющ а я с я тем, что блок управления пластичностью содержит первый интегратор, вход независимой переменной

которого подключен к входу блока управления пластичностью, выход первог интегратора подключен к входу неза- висимой переменной второго интег- ратора, выход которого соединен с входом под()нтегральной функции пер- вого интегратора,с инверсным входом подынтегральной функции второго интератора и с выходом блока управления пластичностью.

3,Модель по П.1, о т л и ч а ю щ а я с я тем, что блок коррекции содержит первый интегратор , вход независимой переменной которого подключен к первому входу блока и к входу подннтегральной функции второго интегратс за, выход которого соединен с входом первого сумматора, другой вход которого подключен к выходу первого интегратора, вход под%|гатегральной функции которого соединен с входом независимой переменной второго интегратора и с втрЕим входом блока коррекции, выход первого сумматор подключен к входу независимой перелге;ной Tpetbero интегр-атора -и к входу пооднтетральной функции четвертого интегратора, выход которого соединен

с одним входом второго сумматора, другой вход которого подключен к выходу третьего интегратора, вход под нтеграпьной функции которого соеди. нён с входом независимой переменной четвертого интегратора и с третьим входом блока коррекции, выход второго сулвиатора подключен к выходу блока коррекции.

Источники информации, принятые во внимание при экспертизе

1,.Авторское свидетельство СССР 512478, кл. G 06 G 7/60, .1974..., .

2. Авторское свидетельство СССР по заявке 2520500/18-24, кл, G 06 G 7/60 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| Устройство для моделирования нейрона | 1988 |

|

SU1596356A2 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| Устройство для моделирования нейрона | 1978 |

|

SU767788A1 |

| Устройство для моделирования нейронных ансамблей | 1980 |

|

SU903910A1 |

| Устройство для моделирования нейрона | 1982 |

|

SU1075632A1 |

Авторы

Даты

1980-09-23—Публикация

1978-08-15—Подача