тур в системах управления. Цель изобретения - расширение функциональных возможностей за счет управления модификацией синаптических весов. Поставленная цель реализуется путём введения п блоков 3 ,...,3 модификации синаптических весов. Введение 1 5 6 ,...,3„ модификации синаптиблоков 3 ческих весов позволяет автоматически осуществлять изменение значений синаптических весов интегральной характеристикой устройства в зависимо- сти от входной активности. 2 ил., 1 п.ф-лы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| Устройство для моделирования нейрона | 1977 |

|

SU682910A1 |

| Устройство для моделирования нейрона | 1978 |

|

SU767788A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| Модель адаптивного нейрона | 1978 |

|

SU765823A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1479944A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| Устройство для моделирования нейрона | 1982 |

|

SU1075632A1 |

Изобретение относится к области бионики и вычислительной техники и может быть использовано в качестве элемента нейронных сетей для моделирования процессов, в устройствах распознавания образов, а также в качестве элемента анализаторных структур в системах управления. Цель изобретения - расширение функциональных возможностей за счет управления модификацией синаптических весов. Поставленная цель реализуется путем введения N блоков 3 1...3 N модификации синаптических весов. Введение блоков 3 1...3 N модификации синаптических весов позволяет автоматически осуществлять изменение значений синаптических весов интегральной характеристикой устройства в зависимости от входной активности. 2 ил., 1 п. ф-лы.

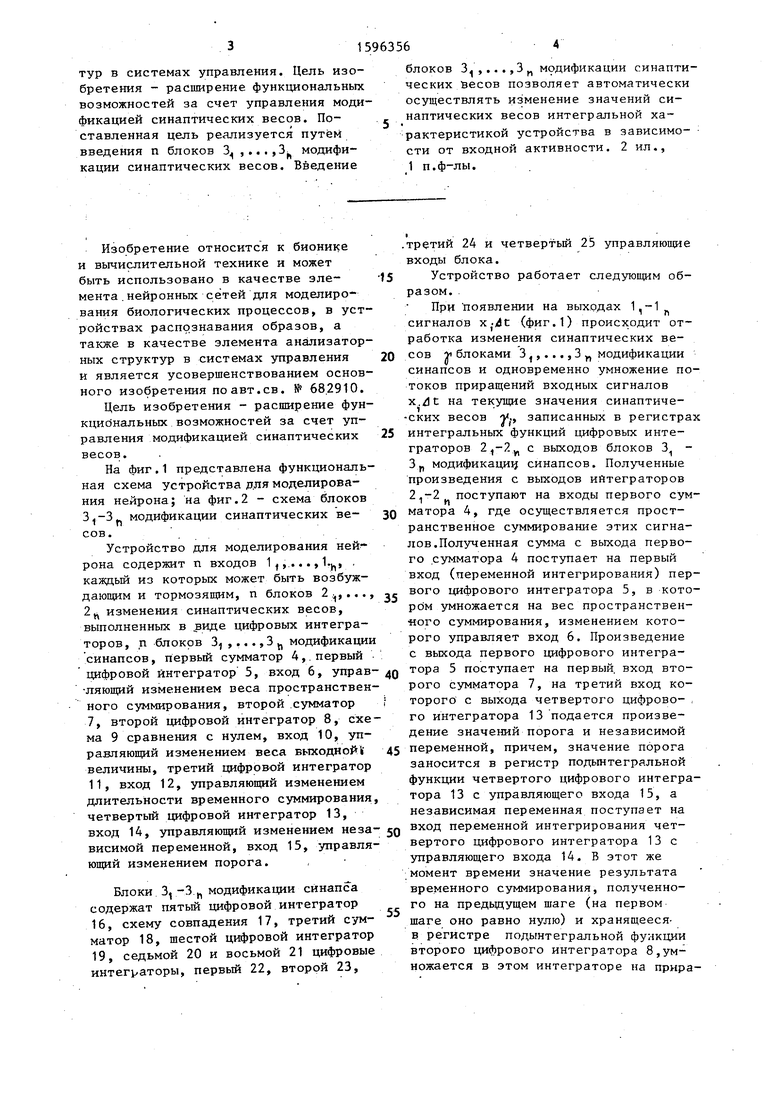

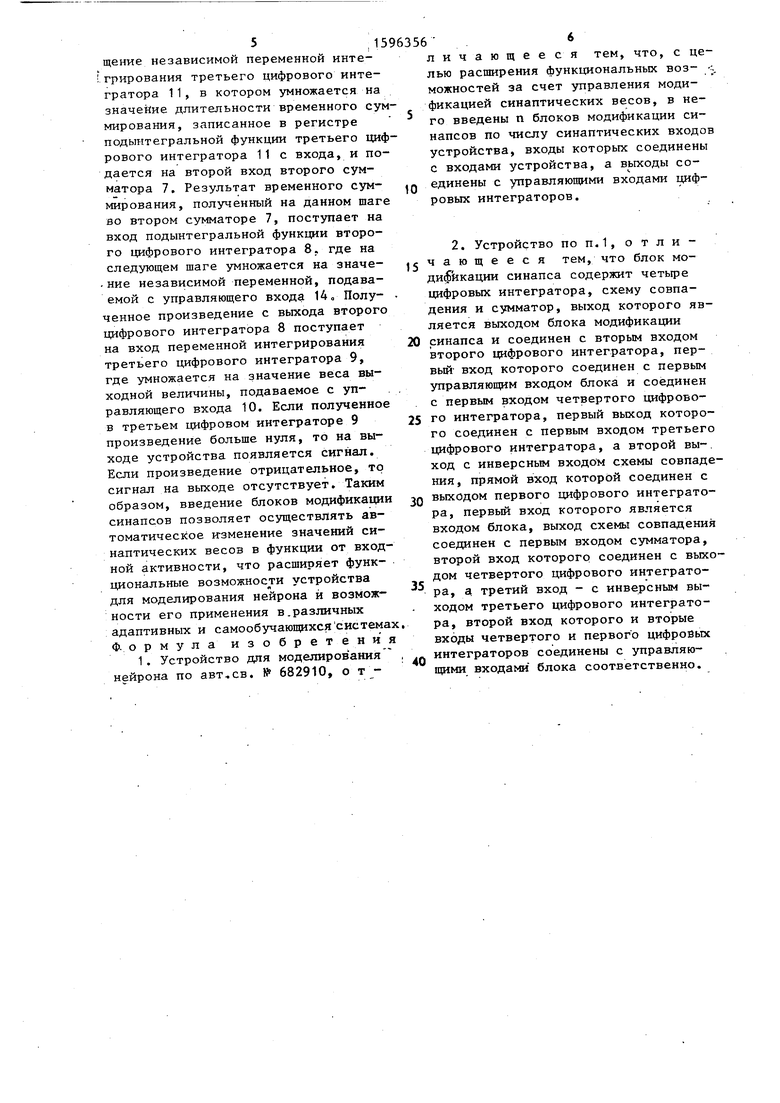

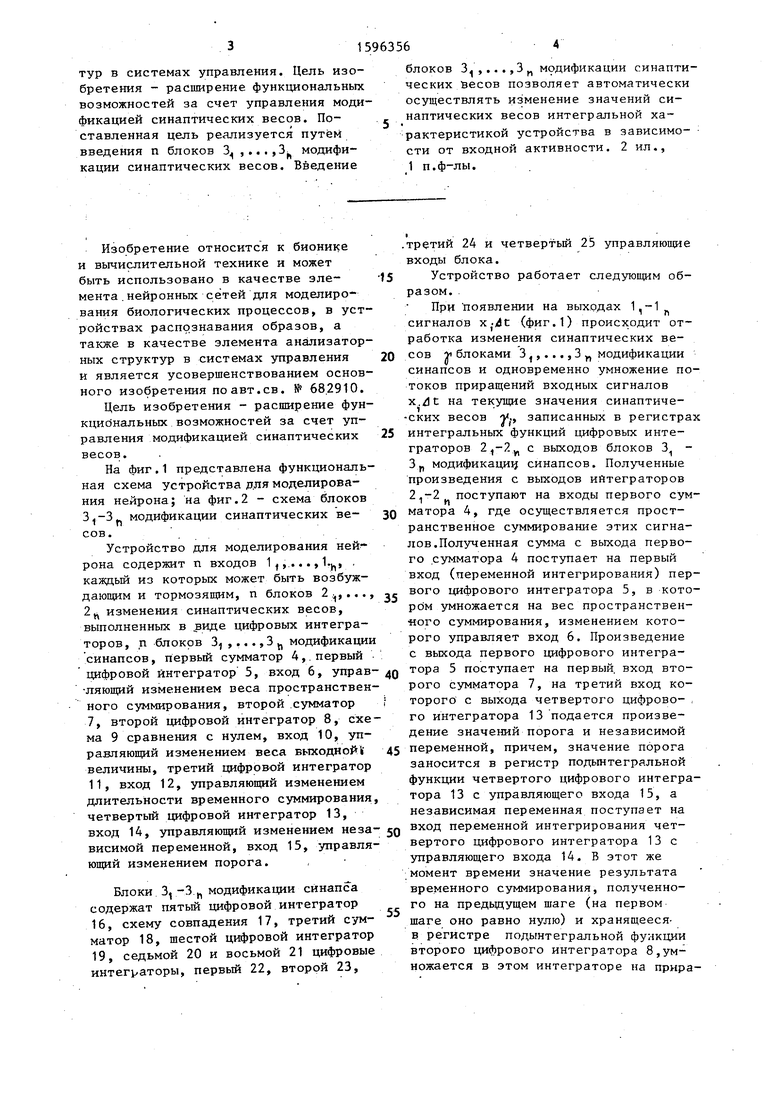

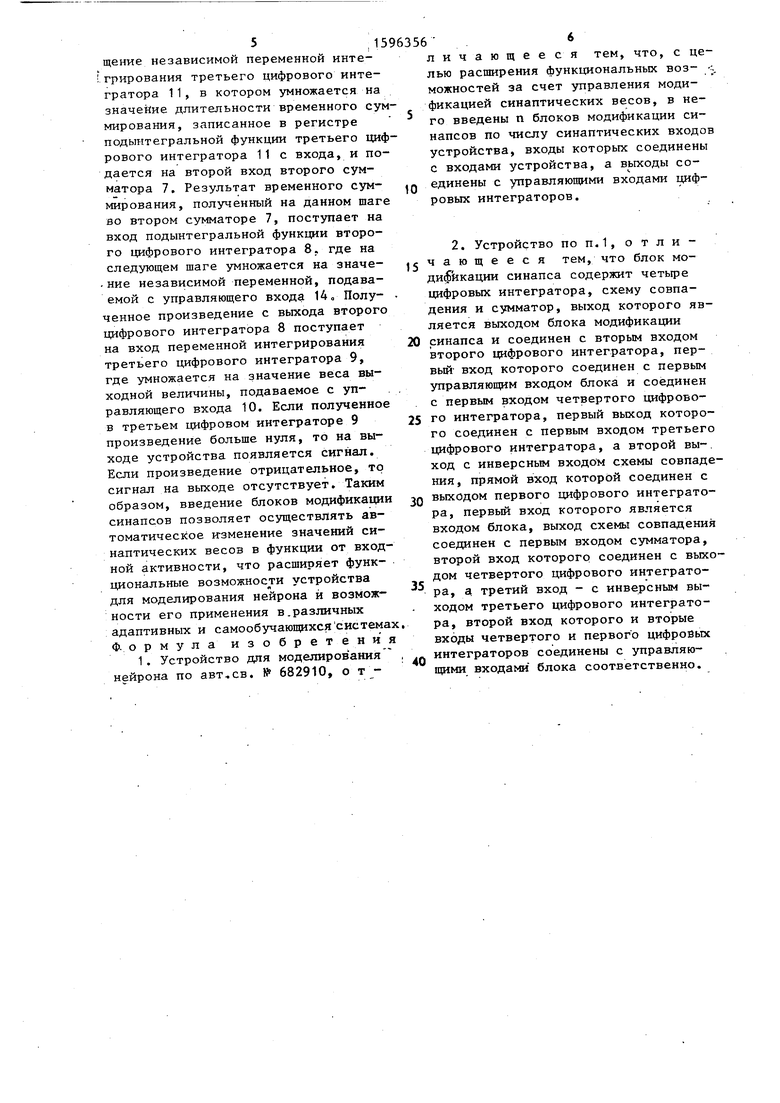

Изобретение относится к бионике и вычислительной технике и может быть использовано в качестве элемента.нейронных сетей для моделирования биологических процессов, в устройствах распознавания образов, а также в качестве элемента анализаторных структур в системах управления и является усовершенствованием основного изобретения по авт.св. № 68.2910. Цель изобретения - расширение функцибнальных возможностей за счет управления модификацией синаптических весов. На фиг.1 представлена функциональная схема устройства для моделирования нейрона; на фиг.2 - схема блоков модификации синаптических весов. Устройство для моделирования нейрона содержит п входов 1 ,,...., 1.j, . каждый из которых может быть возбуждающим и тормозящим, п блоков 2.;,... 2 изменения синаптических весов, выполненных в Jвидe цифровых интеграторов, п блоков 3, ,..., 3 ji модификации синапсов, первый сумматор 4,. первый цифровой интегратор 5, вход 6, управ ляющий изменением веса пространствен ного суммирования, второй .сумматор 7, второй цифровой интегратор 8, схе ма 9 сравнения с нулем, вход 10, управляющий изменением веса выходной величины, третий цифровой интегратор 11, вход 12, управляющий изменением длительности временного суммирования четвертый цифровой интегратор 13, вход 14, управляющий изменением неза висимой переменной, вход 15, управля ющий изменением порога. Блоки .f, модификации синапса содержат пятый цифровой интегратор 16, схему совпадения 17, третий сумматор 18, шестой цифровой интегратор 19, седьмой 20 и восьмой 21 цифровые интеграторы, первый 22, второй 23, третий 24 и четвертый 25 управляющие входы блока. Устройство работает следующим образом. . При появлении на выходах 1,-1 „ сигналов X-At (фиг.1) происходит отработка изменения синаптических весов у блоками 3 ,..., 3 у, модификации синапсов и одновременно умножение потоков приращений входных сигналов x.lt на текущие значения синаптических весов у., записанных в регистрах интегральных функций цифровых интеграторов , с выходов блоков 3. Зр модификациц синапсов. Полученные произведения с выходов интеграторов 2;,-2 поступают на входы первого сумматора 4, где осуществляется пространственное суммирование этих сигналов.Полученная сумма с выхода первого сумматора 4 поступает на первый вход (переменной интегрирования) первого цифрового интегратора 5, в котором умножается на вес пространственного суммирования, изменением которого управляет вход 6. Произведение с выхода первого цифрового интегратора 5 поступает на первый, вход второго сумматора 7, на третий вход которого с выхода четвертого цифрово- , го интегратора 13 подается произведение значений порога и независимой переменной, причем, значение порога заносится в регистр подынтегральной функции четвертого цифрового интегратора 13 с управляющего входа 15, а независимая переменная поступает на вход переменной интегрирования четвертого цифрового интегратора 13с управляющего входа 14. В этот же момент времени значение результата временного суммирования, полученного на предьщущем шаге (на первом шаге оно равно нулю) и хранящеесяв регистре подынтегральной функции второго цифрового интегратора 8,умножается в этом интеграторе на приращение независимой переменной интеiгрирования третьего цифрового интегратора 11, в котором умножается на значение длительности временного суммирования, записанное в регистре подынтегральной функции третьего цифрового интегратора 11с входа, и подается на второй вход второго сумматора 7, Результат временного суммирования, полученный на данном шаге во втором сумматоре 7, поступает на вход подынтегральной функции второго цифрового интегратора 8. где на следующем шаге умножается на значе. кие независимой переменной, подаваемой с управляющего входа 14 о Полученное произведение с вькода второго цифрового интегратора 8 поступает на вход переменной интегрирования третьего цифрового интегратора 9, где умножается на значение веса выходной величины, подаваемое с управляющего входа 10. Если полученное в третьем цифровом интеграторе 9 произведение больше нуля, то на выходе устройства появляется сигнал. Если произведение отрицательное, то сигнал на выходе отсутствует. Таким образом, введение блоков модификации синапсов позволяет осуществлять автоматическое и-зменение значений синаптических весов в функции от входной активности, что расширяет функциональные возможности устройства для моделирования нейрона и возможности его применения в.различных адаптивных и самообучающихсясистемах Ф-ормула изобретения 1 . Устройство для моделирования нейрона по авт,св. № 682910, о т личающееся тем, что, с целью расширения функциональных воз- -., можностей за счет управления модификацией синаптических весов, в него введены п блоков модификации синапсов по числу синаптических входов устройства, входы которых соединены с входами устройства, а вьпсоды соединены с управляющими входами цифровых интеграторов.

синапса и соединен с вторым входом второго цифрового интегратора, первый- вход которого соединен с первым управляющим входом блока и соединен с первым входом четвертого цифрового интегратора, первый выход которого соединен с первым входом третьего цифрового интегратора, а второй вы-, ход с инверсным входом схемы совпадения , прямой вход которой соединен с

выходом первого цифрового интегратора, первый вход которого является входом блока, выход схемы совпадения соединен с первым входом сумматора, второй вход которого соединен с выхоом четвертого цифрового интегратора, а третий вход - с инверсным выходом третьего цифрового интегратоа, второй вход которого и вторые входы четвертого и первого цифровых

нтеграторов соединены с управляюими входами блока соответственно.

Фиг. 2

| Элеватор для беззамковых бурильных труб | 1941 |

|

SU68291A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1988-10-10—Подача