1

Изобретение относится к области запоминающих устройств.

Известны устройства для контроля блоков постоянной памяти.

Одно из известных устройств содержит регистр числа, счетчик адреса, блок сравнения, логические элементы, блок управления {. Быстродействие этого устройства небольшое, область применения узкая.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля блоков постоянной памяти, содержащее блоки управления, первые входы которых соединены соответственно со входом устройства и одним из выходов эталонного блока постоянной памяти, а первые выходы - соответственно с первым и вторым входами блока сравнения, последовательно соединенные генератор импульсов, блок пуска и останова и распределитель синхроимпуль-сов. Первый и второй выходы последнего подключены соответственно ко вторым входам блоков управления и третьему входу блока сравнения. Устройство содержит также триггеры, выходы которых соединены со входами блока пуска и останова, и усилители 2.

При контроле блоков памяти последовательно но всем адресам в случае, когда по

ряду адресов информация не записывалась, на выходных разрядных шинах блока памяти могут наводиться помехи, приводящие к сбою, останову устройства и прекращению дальнейшего контроля. Кроме того, при различном конструктивном построении подвергаемых контролю блоков памяти, связанных с унифицированным блоком управления, контроль таких блоков памяти невозможен из-за различия в коммутации между блоками памяти и блоком уцравления. Все это сужает область применения устройства.

Целью настоящего изобретения является устранение указанных недостатков, а именно: расширение области применения устройства путем обхода отдельных ячеек памяти при контроле.

Поставленная цель достигается тем, что устройство содержит дополнительные триггеры, элементы И и коммутатор. Входы коммутатора подключены ко вторым выходам блоков управления, а выходы - соответственно к выходу устройства и входу

эталонного блока постоянной памяти, входы одного из элементов И соединены с выходами блока сравнения и первого дополнительного триггера, а выход - с входом первого триггера. Одни из входов других

элементов И связаны соответственно с выходами второго и третьего дополнительных триггеров, другие входы - с третьим выходом распределителя синхроимпульсов, а выходы - соответственно со входом второго триггера, одними из входов нервого дополнительного триггера и третьими входами блоков управления. Другие входы первого дополнительного триггера и счетные входы второго и третьего дополнительных триггеров подключены через усилители к другим выходам эталонного блока постоянной памяти.

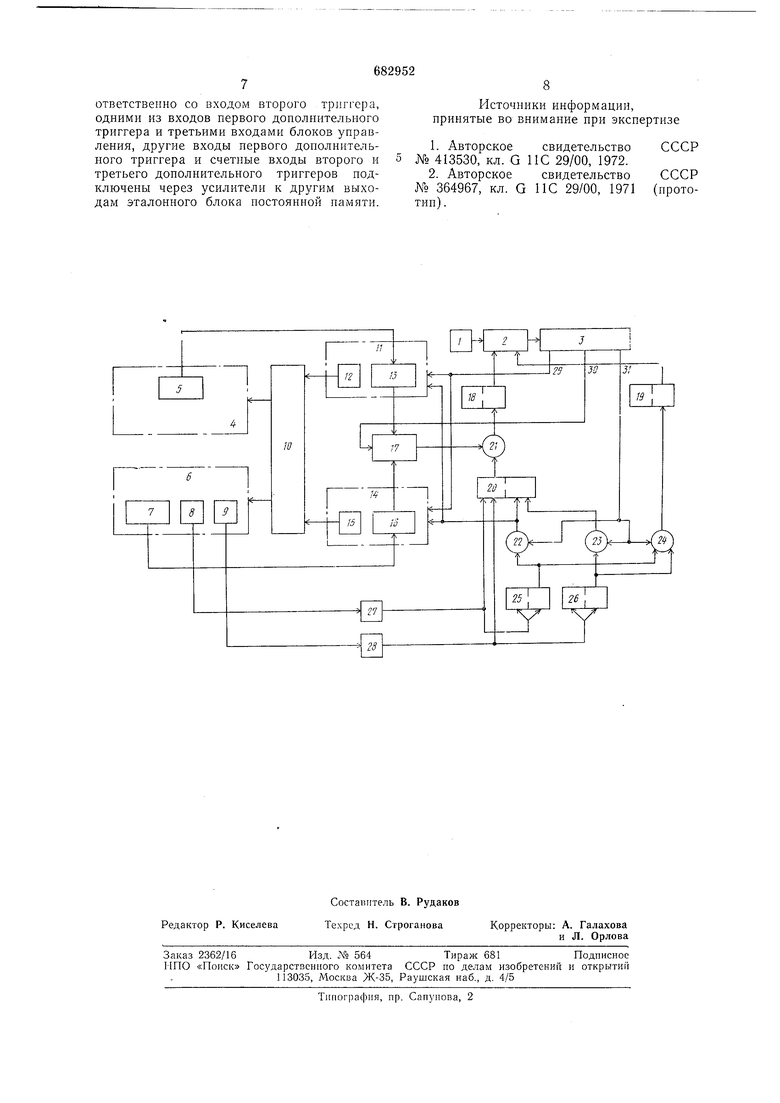

На чертеже представлена структурная схема предложенного устройства.

Устройство содержит генератор 1 импульсов, блок 2 пуска и останова, распределитель 3 синхроимпульсов. Оно подключается к контролируемому блоку 4 постоянной памятп с выходными обмотками 5 информационных разрядов.

Устройство также содержит эталонный блок 6 постоянной памяти с выходными обмотками 7 пиформацнонпых разрядов и двумя обмотками 8 и 9 дополнительных разрядов, коммутатор 10, блок И управления с дешифратором 12 программ и регистром

13числа, блок 14 управления с дешифратором 15 программ и регистром 16 числа, блок 17 сравнения, первый 18 и второй 19 триггеры, первый дополнительный триггер 20, элементы И 21-24, второй 25 и третий

26дополнительные триггеры и усилители

27и 28.

Первые выходы блоков управления подключены к первому и второму входам блока 17, входы коммутатора 10 - ко вторым выходам блоков управления, а выходы - соответственно-к выходу устройства и входу блока 6. Входы элемента И 21 подключены к выходам блока 17 и триггера 20, а выход - ко входу триггера 18. Один из входов элементов И 22-24 соединены соответственно с выходами триггеров 25 и 26. Первый 29 и второй 30 выходы распределителя 3 синхроимпульсов подключены соответственно к одним из входов блоков 11 и

14и третьему входу блока 17. Другие входы элементов И 22-24 соединены с третьим 31 выходом распределителя синхроимпульсов, а выходы - соответственно со входом триггера 19, одним из входов блоков управления И и 14, другие входы триггера 20 и счетные входы триггеров 27 и

28- с выходами блока 6.

Устройство для контроля блоков постоянной памяти работает следующим образом.

Перед запуском автоматического режима контроля блок 4 подключается к устройству (блок 6 также является сменным в устройстве). При этом .элементы коммутатора 10 устанавливаются в положения, обеспечивающие коммутацию выходных щин дешифраторов программ 12 и 15 входными шипами блоков 4 и 6. Триггеры устройства, регистры числа, адресные счетчики

(счетчики программ и тактов) блоков управления 11, 14 устанавливаются в нулевые состояния.

При запуске блока 2 пуска и остаиова импульсы с генератора i импульсов поступают на вход распределителя 3 импульсов, в котором формируются последовательности синхроимпульсов одинаковой частоты СИ1, СИ2, СИЗ, сдвинутые по фазе относительно друг друга.

Импульсы СИ1 с выхода 29 поступают на счетные входы счетчиков тактов (на чертеже не показаны) и в качестве импульсов «Обращение в блоки управления 11, 14. Считанные по команде «Обрап ение коды чисел поступают с выходных обмоток 5 и 7 информационных разрядов блоков 4 и 6 на регистры 13 и 16 числа. При этом подготавливаются входы блока 17 сравнения.

При опросе блока сравнения импульсами СИ2, поступающими с выхода 30 распределителя синхроимпульсов в случае неравенства кодов чисел, импульс с выхода блока сравнения проходит через подготовленный триггером 20 элемент И 21 и поступает на вход «1 триггера 18. Переключенный в состояние «1 триггер 18 запрещает прохождение импульсов с генератора 1. При этом элементы индикации счетчиков программ и тактов блоков 11 и 14 управления определяют адрес числа, при обращении по которому произошел сбой, а визуальным поразрядным сравнением состояний элементов индикации регистров числа определяется разряд числа контролируемого блока 4, в котором произошел сбой.

При равенстве кодов чисел, считанных при обращении но первому адресу, после автоматической установки «О регистров 13 и 16 числа последующими импульсами СИ1 осуществляется контроль кодов чисел по другим адресам (кодам счетчиков тактов).

При обращении к блоку 4 по последнему такту каждой программы с обмотки 8 дополнительного разряда снимается сигнал «1, передаваемый через усилитель воспроизведения 27 на вход «О триггера 20, чем продолжается подготовка потенциального входа элемента И 21. Этот же сигнал «1 с усилителя 27 воспроизведения устанавливает в состояние «1 триггер 25. При этом вход элемента И 22 подготавливается потенциалом с выхода триггера 25.

После опроса импульсом СИ2 блока 17 сравнения и при отсутствии сбоя импульс СИЗ с выхода 31 проходит с распределителя 3 через элемент И 22 в блоки 11 и 14 управления для установки в состояние «О счетчиков тактов. Этот же импульс поступает на счетные входы счетчиков программ блоков управления, чем осуществляется подготовка к обращению по тактам следующей программы. Одновременно импульс СИЗ с выхода элемента И 22 устанавливает состояние «1 триггер 20.

При обращении к блоку 4 по иервому такту всех программ, начиБая со второй, с обмотки 8 дополнительного разряда сиимается сигнал «1, возвращающий триггеры 20 и 25 в состояние «О, чем обеспечивается останов при сбое и запрет элемента И 22 при дальнейшем контроле блока 4.

При наличии прерывания в ирограммах, например, с программы до програмл1Ы включительно, необходимо отключить блок 2 при сбое. Для этого при обращении к блоку 4 по последнему такту программы - «1 сигналом «1, снимаемым с обмотки 8 дополнительного разряда, триггер 25 устанавливается в состояние «1. После опроса импульсом СИ2 импульсы СИЗ проходят через подготовительный элемент И 22 на установку в состояние «1 триггера 20, а также в блоки управления 11 и 14, на счетные входы счетчиков программ и входы установки «О счетчиков тактов. При этом вход элемента И 21 запрещен потенциалом с триггера 20, а счетчики программ блоков управления 11 и 14 импульсами СИЗ последовательно переводятся к коду программ

При обращении к блоку 4 по первому такту программ «+1 сигналом «1, снимаемым с обмотки 8 дополнительного разряда, триггеры 20 и 25 возвращаются в состояния «О, чем обеспечивается останов прп сбое и запрет элемента И 22 при дальнейшем контроле блока 4.

При наличии прерывания в тактах некоторых программ, например с такта до такта включительно, необходимо отключить блок 2 при сбое. Для этого при обращении к блоку по такту «-1 с обмотки 9 дополнительного разряда снимается сигнал «1, передаваемый через усилитель 28 воспроизведення на вход «О триггера 20 и на счетный вход триггера 26, переключая его в состояние «1. При этом вход элемента И 23 оказывается подготовительным потенциалом с триггера 26.

После опроса импульсом СИ2 блока 17 сравнения и при отсутствии сбоя импульсы СИЗ с выхода 31 распределителя 3 проходят через элемент И 23 на вход «1 триггера 20, чем обеспечивается запрет элемеита И 21 и отключение блока 2 при сбое.

Последующими импульсами СИ1 с выхода 29 осуществляется последовательный переход счетчиков тактов блоков управления 11 и 14 к коду такта «-|-1.

При обращении к блоку 4 по такту «+1 с обмотки 9 дополнительного разряда вновь снимается сигнал «1, возвращающий в состояние «О триггеры 20 и 26, чем обеспечивается останов при сбое и запрет элемента И 23 при дальнейшем контроле блока 4.

При обращении к блоку 4 по последнему такту последней программы для фиксации окончания автоматического контроля блока

памяти 4 и останова с обмоток 8 и 9 дополнительных разрядов снимаются сигналы «1, переключающпе в состояние «1 триггеры 25 и 26. При этом входы элемента

И 24 подготавливаются потеицпаламн с выходов триггеров 25, 26. После опроса импз льсом СИ2 блока 17 сравнения и прп отсутствии сбоя импульс СИЗ проходит через элемент И 24 и переключает в состояние

«1 триггер 19, связанный с блоком 2. Прп переключении в состояние «1 триггера 19 прекращается поступление импульсов и генератора 1 и осуществляется останов автоматического контроля блока 4. При этом

элементы индикации счетчиков тактов н программ блоков управления И и 14 определяют коды последнего адреса,по которому производилось обращение к блоку 4, а элемент индикации останова - конец автоматического контроля блока 4.

Описанное устройство позволяет производить автоматический контроль ряда блоков постоянной памяти, пмеюп1,пх конструктивные особенности и отлпчающи.хся коммутацией. Кроме того, расширяется область примеиения устройства, позволяющего пропзводить контроль блоков памяти, имеющих прерывания в адресах. Тем самым сокращаются и затраты труда, связанные с ручным

контролем блоков памяти.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее блоки управленпя,

первые входы которых соединены соответственно со входом устройства и одним из выходов эталонного блока постоянной памяти, а первые выходы - соответственно с первым и вторым входами блока сравнення, последовательно соединенные генератор импульсов, блок пуска и останова п распределптель синхроимпульсов, первый и второй выходы которого подключепы соответственно ко вторым входам блоков управленпя п третьему входу блока сравнения, триггеры, выходы которых соединены со входами блока пуска и останова, п усилители, отличающееся тем, что, с целью расширения области применения устройства

путем обеспечения возможности обхода отдельных ячеек памяти прп контроле, оно. содержит дополнительные триггеры, элементы И и коммутатор, входы которого подключены ко вторым выходам блоков

управления, а выходы - соответственно к выходу устройства п входу эталонного блока постоянной памяти, входы одного пз элементов И подключены к выходам блока сравнения и первого дополнительного триггера, а выход - ко входу первого триггера, одни из входов других элементов И соединены соответственно с выходами второго п третьего дополнительных триггеров, другие входы - с третьим выходом распределителя синхроимпульсов, а выходы - соответственно со входом второго Tpiirrepa, одними из входов первого дополнительного триггера и третьими входами блоков управления, другие входы первого доиолпительного триггера и счетные входы второго и третьего дополнительного триггеров подключены через усилители к другим выходам эталонного блока постоянной памяти.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 413530, кл. G НС 29/00, 1972.

2.Авторское свидетельство СССР Ло 364967, кл. G ПС 29/00, 1971 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для управления ленточным перфоратором | 1982 |

|

SU1049934A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

Авторы

Даты

1979-08-30—Публикация

1977-05-19—Подача