Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматического контроля оперативной памяти,

Целью изобретения является повышение достоверности контроля.

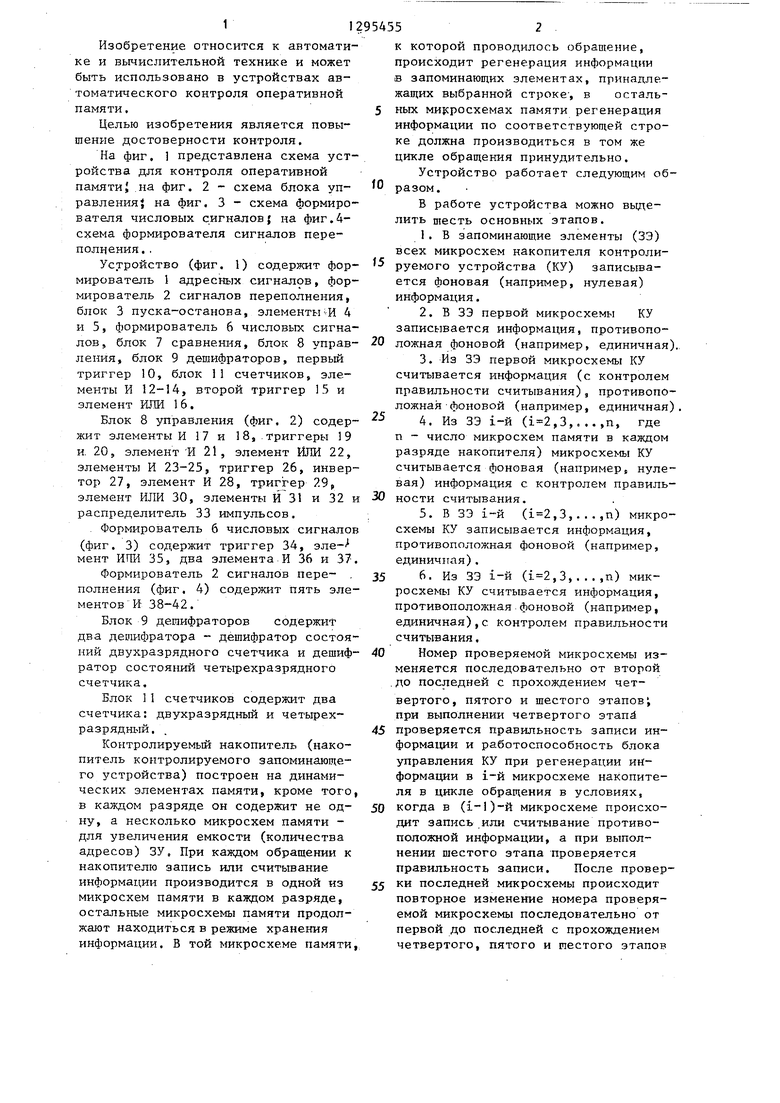

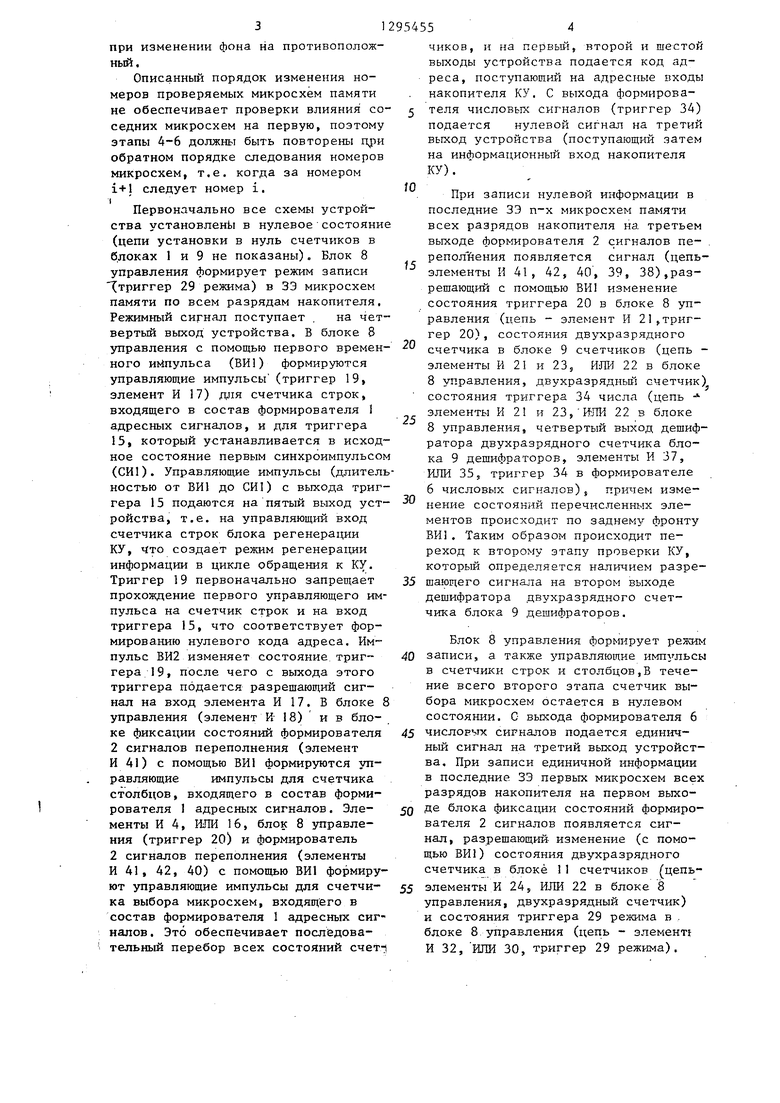

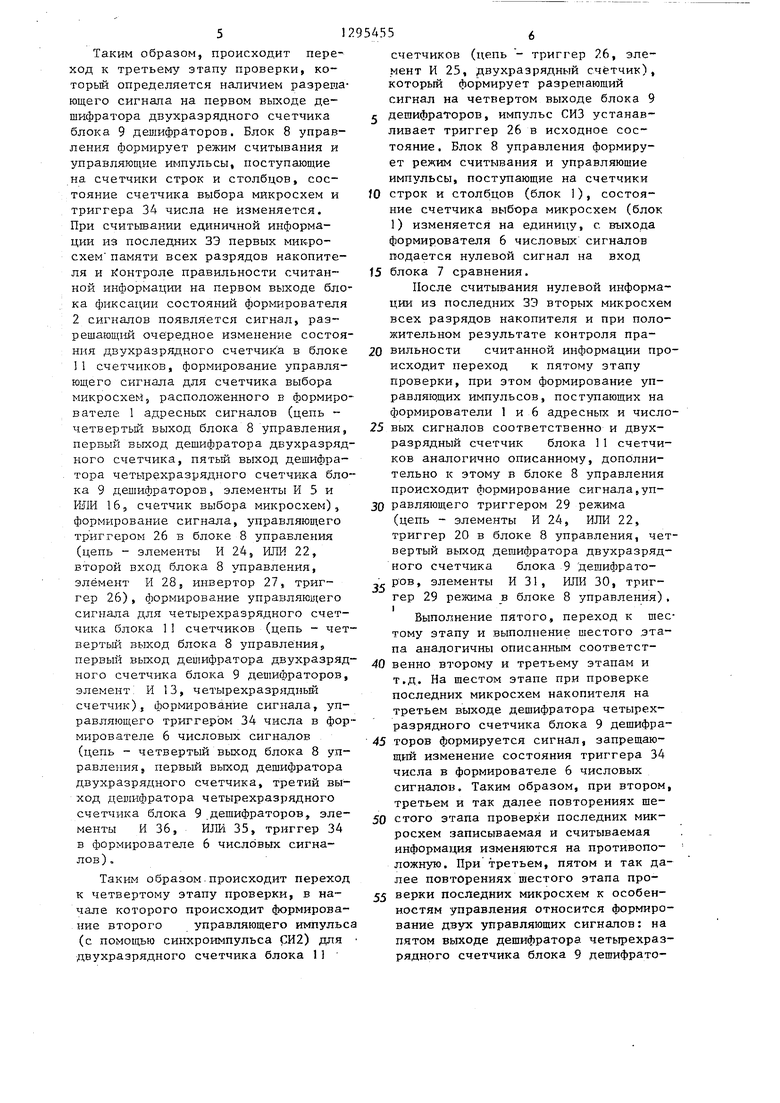

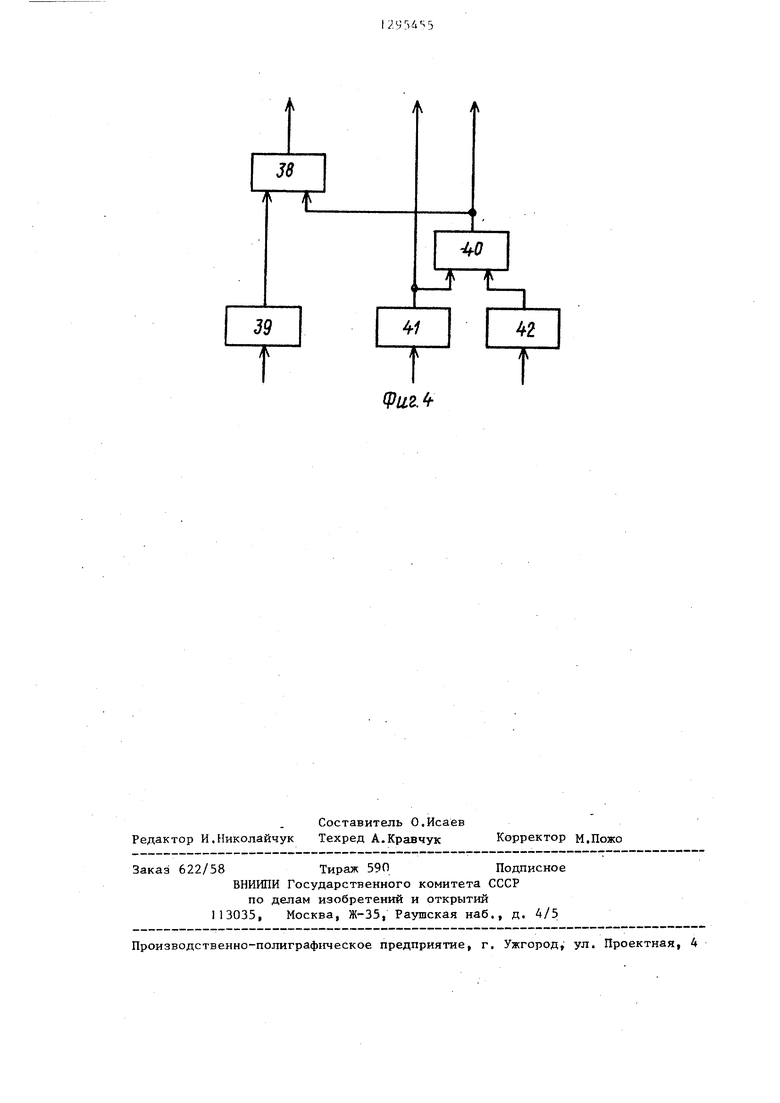

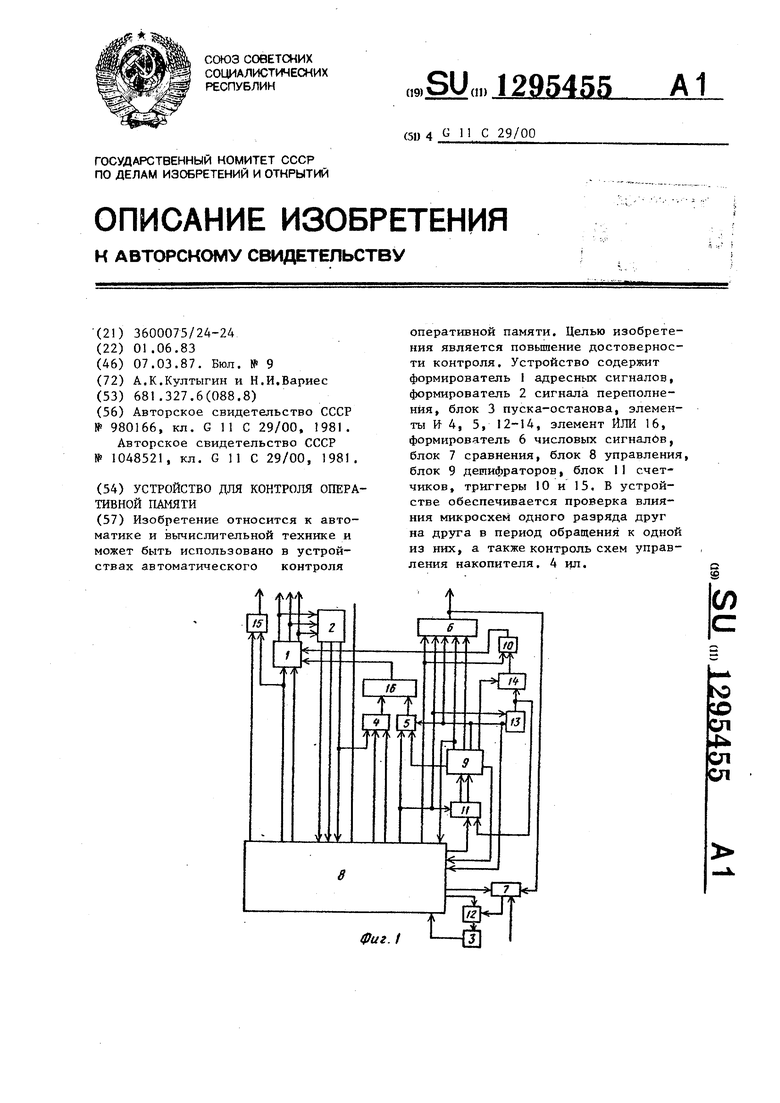

На фиг. представлена схема устройства для контроля оперативной памятиJ на фиг, 2 - схема блока уп- равления} на фиг. 3 - схема формирователя числовых сигналов} на фиг.4- схема формирователя сигналов переполнения . ,

Устройство (фиг. 1) содержит фор- мирователь 1 адресных сигналов, формирователь 2 сигналов переполнения, блок 3 пуска-останова, элементы--И 4 и 5, формирователь 6 числовых сигналов, блок 7 сравнения, блок 8 управления, блок 9 дешифраторов, первый триггер 10, блок 11 счетчиков, элементы И 12-14, второй триггер 15 и элемент ИЛИ 16,

Блок 8 управления (фиг. 2) содержит элементы И 17 и 18,.триггеры 19 и. 20, элемент И 21, элемент ИЛИ 22, элементы И 23-25, триггер 26, инвертор 27, элемент И 28, триггер 29, элемент ИЛИ 30, элементы И 31 и 32 и распределитель 33 импульсов.

Формирователь б числовых сигналов (фиг. 3) содержит триггер 34, эле- мент ИПИ 35, два элемента И 36 и 37

Формирователь 2 сигналов пере- . полнения (фиг. 4) содержит пять элементов И 38-42.

Блок 9 дешифраторов содержит два дешифратора - дешифратор состояний двухразрядного счетчика и дешиф- ратор состояний четырехразрядного счетчика.

Блок 11 счетчиков содержит два счетчика: двухразрядный и четырехразрядный. ,

Контролируемый накопитель (накопитель контролируемого запоминающего устройства) построен на динамических элементах памяти, кроме того в каждом разряде он содержит не од- ну, а несколько микросхем памяти - для увеличения емкости (количества адресов) ЗУ. При каждом обращении к накопителю запись или считывание информации производится в одной из микросхем памяти в каждом разряде, остальные микросхемы памяти продолжают находиться в режиме хранения информации. В той микросхеме памяти

0

5

5

0

5

0 5

к которой проводилось обращение, происходит регенерация информации в запоминающих элементах, принадлежащих выбранной строке , в остальных ми|сросхемах памяти регенерация информации по соответствующей строке должна производиться в том же цикле обращения принудительно.

Устройство работает следующим образом,

В работе устройства можно выделить шесть основных этапов.

1.В запоминающие элементы (ЗЭ) всех микросхем накопителя контролируемого устройства (КУ) записывается фоновая (например, нулевая) информация.

2.В ЗЭ первой микросхемы КУ записывается информация, противоположная фоновой (например, единичная).

3.Из ЗЭ первой микросхемы КУ считывается информация (с контролем правильности считывания), противоположная -фоновой (например, единичная).

4.Из ЗЭ i-й (,3,..,,п, где п - число микросхем памяти в каждом разряде накопителя) микросхемы КУ считывается фоновая (например, нулевая) информация с контролем правильности считывания.

5.В ЗЭ i-й (,3,...,п) микросхемы КУ записывается информация, противоположная фоновой (например, единичная).

6.Из ЗЭ 1-й (,3,...,п) микросхемы КУ считывается информация, противоположная фоновой (например, единичная),с контролем правильности считывания.

Номер проверяемой микросхемы изменяется последовательно от второй .до последней с прохождением четвертого, пятого и шестого этапов , при выполнении четвертого этапй проверяется правильность записи информации и работоспособность блока управления КУ при регенерации информации в 1-й микросхеме накопителя в цикле обращения в условиях, когда в (1-1)-и микросхеме происходит запись HJ:m считывание противоположной информации, а при выполнении шестого этапа проверяется правильность записи. После проверки последней микросхемы происходит повторное изменение номера проверяемой микросхемы последовательно от первой до последней с прохождением четвертого, пятого и шестого этапов

при изменении фона на противоположный.

Описанный порядок изменения номеров проверяемых микросхем памяти не обеспечивает проверки влияния соседних микросхем на первую, поэтому этапы 4-6 должны быть повторены дри обратном порядке следования номеров микросхем, т.е. когда за номером

i+1 следует номер i.

1

Первоначально все схемы устройства установленЬ в нулевое состояни (цепи установки в нуль счетчиков в блоках 1 и 9 не показаны), Блок 8 управления формирует режим записи триггер 29 режима) в ЗЭ микросхем памяти по всем разрядам накопителя, Режимный сигнал поступает . на четвертый выход устройства. В блоке 8 управления с помощью первого временного импульса (БИ1) формируются управляющие импульсы (триггер 19, элемент И 17) для счетчика строк, входящего в состав формирователя 1 адресных сигналов, и для триггера 15, который устанавливается в исходное состояние первым синхроимпульсом (СИ1). Управляющие импульсы (длительностью от ВИ1 до СИ1) с выхода триггера 15 подаются на пятый выход устройства, т.е. на управляющий вход счетчика строк блока регенерации КУ, Что создает режим регенерации информации в цикле обращения к КУ. Триггер 19 первоначально запрещает прохождение первого управляющего импульса на счетчик строк и на вход триггера 15, что соответствует формированию нулевого кода адреса. Импульс ВИ2 изменяет состояние триггера 19, после чего с выхода этого триггера подается разрешающий сигнал на вход элемента И I7. Б блоке 8 управления (элемент И I8) и в блоке фиксации состояний формирователя

2сигналов переполнения (элемент

И 41) с помощью ВИ1 формируются управляющие импульсы для счетчика столбцов, входящего в состав формирователя 1 адресных сигналов. Элементы И 4, ИЛИ 16, блок 8 управления (триггер 20) и формирователь 2 сигналов переполнения (элементы И 41, 42, 40) с помощью ВИ1 формируют управляющие импульсы для счетчика выбора микросхем, входящего в состав формирователя 1 адресных сигналов . Это обеспечивает послйдова- тельный перебор всех состояний счет-1

О

5

0

5

0

5

чиков, и на первый, второй и шестой выходы устройства подается код адреса, поступающий на адресные входы накопителя КУ. С выхода формирователя числовых сигналов (триггер 34) подается нулевой сигнал на третий выход устройства (поступающий затем на информационный вход накопителя КУ).

При записи нулевой информации в последние ЗЭ п-х микросхем памяти всех разрядов накопителя на третьем выходе формирователя 2 сигналов пе- . репол йения появляется сигнал (цепь- элементы И 41, 42, 40, 39, 38),разрешающий с помощью ВИ1 изменение состояния триггера 20 в блоке 8 управления (пепь - элемент И 21,триггер 20), состояния двухразрядного счетчика в блоке 9 счетчиков (цепь - элементы И 21 и 23j ИЛИ 22 в блоке 8 управления, двухразрядный счетчик) состояния триггера 34 числа (цепь элементы И 2 и 23, ИЛИ 22 в блоке 8 управления, четвертый выход дешифратора двухразрядного счетчика блока 9 дешифраторов, элементы И 37, ИЛИ 35, триггер 34 в формирователе 6 числовых сигналов), причем изменение состояний перечисленных элементов происходит по заднему фронту ВИ1. Таким образом происходит переход к второму этапу проверки КУ, который определяется наличием разрешающего сигнала на втором выходе дешифратора двухразрядного счетчика блока 9 дешифраторов.

Блок 8 управления формирует режим

записи, а также управляющие импульсы в счетчики строк и столбцов,В течение всего второго этапа счетчик выбора микросхем остается в нулевом состоянии. G выхода формирователя 6

числовых сигналов подается единичный сигнал на третий выход устройства. При записи единичной информации в последние ЗЭ первых микросхем всех разрядов накопителя на первом выходе блока фиксации состояний формирователя 2 сигналов появляется сигнал, разрешающий изменение (с помощью ВИ) состояния двухразрядного счетчика в блоке 11 счетчиков (цепьэлементы И 24, ИЛИ 22 в блоке 8 управления, двухразрядный счетчик) и состояния триггера 29 режима в , блоке 8 управления (цепь - элемент И 32, или 30, триггер 29 режима).

5)

Таким образом, происходит переход к третьему этапу проверки, ко- торьй определяется наличием разрешающего сигнала на первом выходе дешифратора двухраэрядного счетчика блока 9 дешифраторов. Блок 8 управления формирует режим считывания и управляющие импульсы, поступающие на счетчики строк и столбцов, состояние счетчика выбора микросхем и триггера 34 числа не изменяется. При считьшаиии единичной информации из последних 33 первых микросхем памяти всех разрядов накопителя и Контроле правильности считанной информации на первом выходе блока фиксации состояний формирователя 2 сигналов появляется сигнал, раз- решающж очередное изменение состояния двухразрядного счетчик а в блоке 11 счетчиков, формирование управляющего сигнала для счетчика выбора микросхем, расположенного в формирователе 1 адресных сигналов (цепь четвертьй выход блока 8 управления, первый выход дешифратора двухразрядного счетчика, пятьй выход дещифра- тора четырехразрядного счетчика блока 9 дешифраторов, элементы И 5 и ГШИ 16 5 счетчик выбора микросхем), формирование сигнала, управляющего триггером 26 в блоке 8 управления (цепь - элементы И 24, ИЛИ 22, второй вход блока 8 управления, элемент И 28, инвертор 27, триггер 26), формирование управляющего сигнала для четырехразрядного счетчика блока 1I счетчиков (цепь - четвертьй выход блока 8 управления, первый выход дешифратора двухразрядного счетчика блока 9 дешифраторов, элемент И 13, четырехразрядньй счетчик), формирование сигнала, управляющего триггером 34 числа в формирователе 6 числовых сигналов (цепь - четвертый выход блока 8 управления, первый выход дешифратора двухразрядного счетчика, третий выход дешифратора четырехразрядного счетчика блока 9 дешифраторов, элементы И 36, ИЛИ 35, триггер 34 в формирователе 6 числовых сигналов).

Таким образом-происходит переход к четвертому этапу проверки, в начале которого происходит формирование второго управляющего импульс (с помощью синхроимпульса СИ2) для двухразрядного счетчика блока 1

счетчиков (цепь - триггер 26, элемент И 25, двухразрядный счетчик), который формирует разрешающий сигнал на четвертом выходе блока 9

дешифраторов, импульс СИЗ устанавливает триггер 26 в исходное состояние , Блок 8 управления формирует режим считывания и управляющие импульсы, поступающие на счетчики строк и столбцов (блок 1), состояние счетчика выбора микросхем (блок 1) изменяется на единицу, с. выхода формирователя 6 числовых сигналов подается нулевой сигнал на вход

5 блока 7 сравнения.

После считывания нулевой информации из последн1гх ЗЭ вторых микросхем всех разрядов накопителя и при положительном результате контроля пра0 вильности считанной информации происходит переход к пятому этапу проверки, при этом формирование уп- равляю.щих импульсов, поступающих на формирователи 1 и 6 адресных и число5 вых сигналов соответственно и двухразрядный счетчик блока 11 счетчиков аналогично описанному, дополнительно к этому в блоке 8 управления происходит формирование сигнала,уп0 равляющего триггером 29 режима (цепь - элементы И 24, ИЛИ 22, триггер 20 в блоке 8 управления, четвертый выход дешифратора двухразрядного счетчика блока ,9 дешифраторов, элементы И 31, ИЛИ 30, триггер 29 режима в блоке 8 управления), I

Выполнение пятого, переход к шестому этапу и выполнение шестого этапа аналогичны описанным соответст0 венно второму и третьему этапам и т.д. На шестом этапе при проверке последних микросхем накопителя на третьем выходе дешифратора четырехразрядного счетчика блока 9 дешифра5 торов формируется сигнал, запрещающий изменение состояния триггера 34 числа в формирователе 6 числовых сигналов. Таким образом, при втором, третьем и так далее повторениях ше0 стого этапа проверки последних микросхем записываемая и считываемая информация изменяются на противоположную. При третьем, пятом и так далее повторениях шестого этапа про5 верки последних микросхем к особенностям управления относится формирование двух управляющих сигналов: на пятом выходе дешифратора четьфехраз- рядного счетчика блока 9 дешифрато5

ров формируется сигнал, запрещающий формирование управляющего импульса, поступающего на счетчик выбора микросхем, а на шестом выходе - сигнал, разрешаюпшй формирование управляющего импульса, поступающего на триггер 10 (цепь - четвертый выход блока 8 управления, элементы И 13 и 14, триггер 10). Таким образом, изменение состояния триггера 10 переключает режим работы счетчика выбора микросхем на реверсивный и обратно, При вьшолнении четвертого и шестого этапов проверки КУ производится контроль считанной информации блоком 7 сравнения, на второй вход которого поступает считанная из КУ информация. Если результат сравнения отрицательный, то на выходе этой схемы формируется yпpaвляю ий импульс с помощью ВИЗ, который производит останов работы распределителя 33 импульсов в блоке 8 управления (цепь - триггер 29 режима в блоке 8 управления, элемент И 12, блок 3 пуска-останова, распределитель 33 импульсов), Останов устройства определяет неисправности в КУ либо в блоке управления (отсутствие организации регенерации в цикле обращения) , либо несоответствие времени выборки адреса необходимым требованиям. В первом случае остановы устройства наблюдаются при проверке каждых микросхем, во втором случае - при проверке одной, двух микросхем.

Формула изобретения

Устройство для контроля оперативной памяти, содержащее блок управления, первый и второй выходы которого соединены с первым и вторым входами формирователя адресных сигналов , выходы первой и второй групп которого являются выходами младших разрядов адреса устройства, а выходы первой группы соединены с входами первой группы формирователя сигналов переполнения, первый выход которого подключен к первым входам первого элемента И и первому входу блока управления, третий выход которого соединен с вторым входом первого элемента И, четвертый выход блока управления подключен к первым входам второго элемента И и блока счетчи-. ков, второй вход которого соединен с пятым выходом блока управления.

15

5

первый выход блока счетчиков подключен к первому входу блока дешифраторов, первый выход которого соединен с вторыми входами второго элемента 5 И и блока управления, с первыми входами третьего элемента И и формирователя числовых сигналов, выход которого является информационным выходом устройства и,подключен к одним О информационным входам блока сравнения, другие информационные входы которого являются информационными входами устройства, управляющий вход соединен с шестым выходом блока управления, а выход соединен с первым входом четвертого элемента И, второй вход которого подключен к седь- мому выходу блока управления, а выход соединен с входом блока пуска- 0 останова, выход которого подключен к третьему входу блока управления, четвертый вход которого соединен с вторым выходом блока дешифраторов, а восьмой выход блока управления является выходом записи-считывания устройства, выход пятого элемента И подключен к одному входу первого триггера, другой вход которого соединен с. девятым выходом блока управ- 0 ления и вторым входом формирователя числовых сигналов, отличающееся тем, что, с целью повьше- ния достоверности контроля, в устройство введены второй триггер и эле- 5 мент ИЛИ, причем первый и второй входы второго триггера соединены соответственно с первьм и десятьм выходами блока управления, а выход является выходом управления регене- 0 рацией устройства, выходы третьей группы формирователя адресных сигналов являются выходами старших разрядов адреса устройства, а выходы второй и третьей групп соединены с 5 входами второй и третьей групп формирователя сигналов переполнения, второй и третий выходы которого подключены к пятому и шестому входам блока управления, четвертый выход 0 которого подключен к пятому входу формирователя числовых сигналов и второму входу третьего элемента И, выход которого соединен с первым входом пятого элемента И и третьим 5 входом блока счетчиков, второй выход которого подключен к второму входу блока дешифраторов, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с

91

третьим, четвертым входами формирователя числовых сигналов, с седьмым входом блока управления, вторым входом пятого элемента И, вторым входом второго элемента И, выход ко торого подключен к первому входу элемента ИЛИ, третий вход первого

29545510

элемента И соединен с одиннадцатым выходом блока управления, а выход - с вторым входом элемента ИЛИ, выход которого и выход первого триг- 5 гера подключены соответственно к

третьему и четвертому входам формирователя адресных сигналов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для регенерации информации в динамической памяти | 1983 |

|

SU1193729A1 |

| Устройство для контроля памяти | 1979 |

|

SU769642A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Кодовый трансмиттер для рельсовых цепей | 1987 |

|

SU1527062A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматического контроля оперативной памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит формирователь I адресных сигналов, формирователь 2 сигнала переполнения, блок 3 пуска-останова, элементы И 4, 5, 12-14, элемент ИЛИ 16, формирователь 6 числовых сигналив, блок 7 сравнения, блок 8 управления, блок 9 дешифраторов, блок I1 счетчиков , триггеры 10 и 15. В устройстве обеспечивается проверка влияния микросхем одного разряда друг на друга в период обращения к одной из них, а также контроль схем управления накопителя. 4 ил. (Л фиг. t

fpuB.3

Л

39

Составитель О.Исаев Редактор И.Николайчук Техред А.Кравчук

Заказ 622/58Тираж 59ППодписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграф1гческое предприятие, г, Ужгороду ул. Проектная, 4

bL

42

Т

Корректор М.Пожо

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-07—Публикация

1983-06-01—Подача