вания, .первые выходы которых через блок разрешения подключены к одному -из входав ключа, дополнительно введен блок вычитания, входы которого подключены к выходам блока Памяти. Выходы блока вычитания поразрядно соединены с входами блока вывода результата. Выход генератора .импульсо.в подключен к четвертому входу каждого канала иреобразовання, вторые выходы .которых соединены с соответствующими входами блока управления. Третьи и четвертые выходы каждого канала преобразоваиня соединены с адресными входами блока памяти.

Кроме того, каждый .канал преобразоваиия содержит триггер основной па-мяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И. Прямой выход триггера основной памяти лодключеп к первому входу сумматора по модулю два, первому входу первого элемента И, первому выходу канала преобразования и к прямому входу триггера пуска, инверсный вход которого является четвертым входом канала преобразования. Пря.мой выход триггера пуска лодключен непосредственно к перво.му .входу второго элемента И и через сумматор по модулю два .к управляющему входу триггера дополнительной памяти ;и к второму выходу канала преобразования. Выход триггера дололнительной памяти соединен с вторыми входами первого и второ.го элементов И, выходы которых являются соответственно третьи-м и четверты.м выходами канала преобра-зования. Инверсный выход триггера осяовной памяти соединен с третьим входом второго элемента И, а инверсный выход триггера соединен с третьим .входом первого эле.мента И. Прямой и инверсный входы триггера дополнительной памяти являются соответственно вторым и третьим входами ка|Нала преобразования.

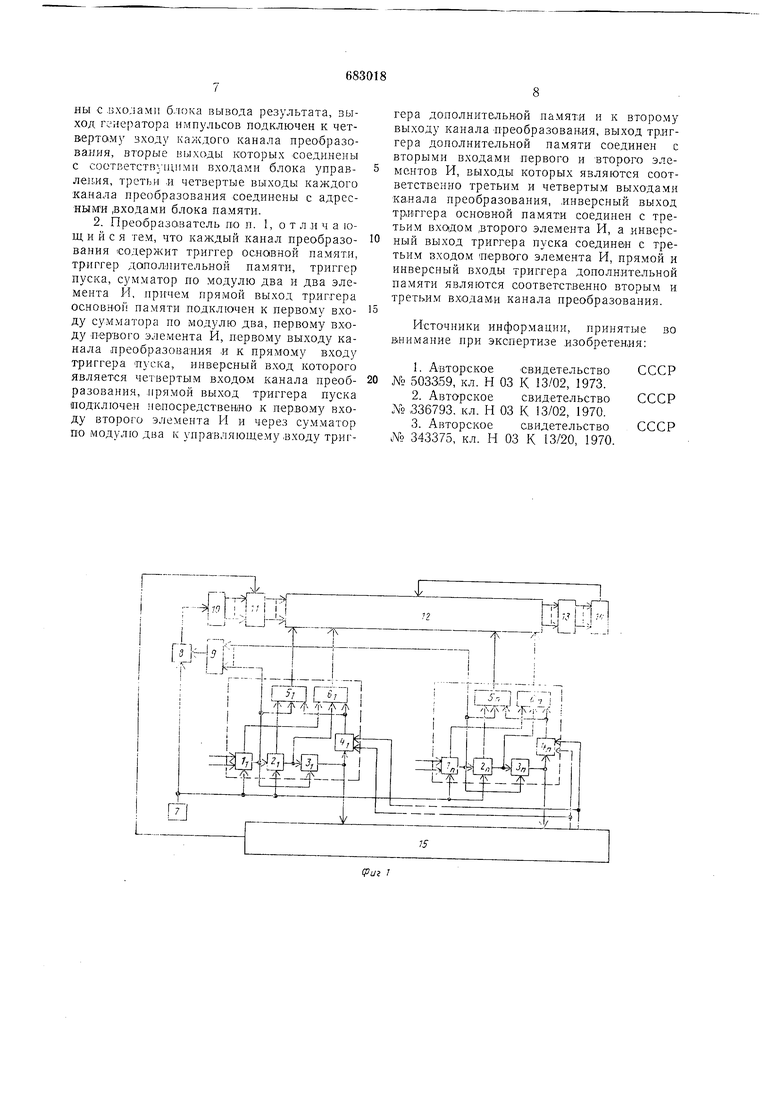

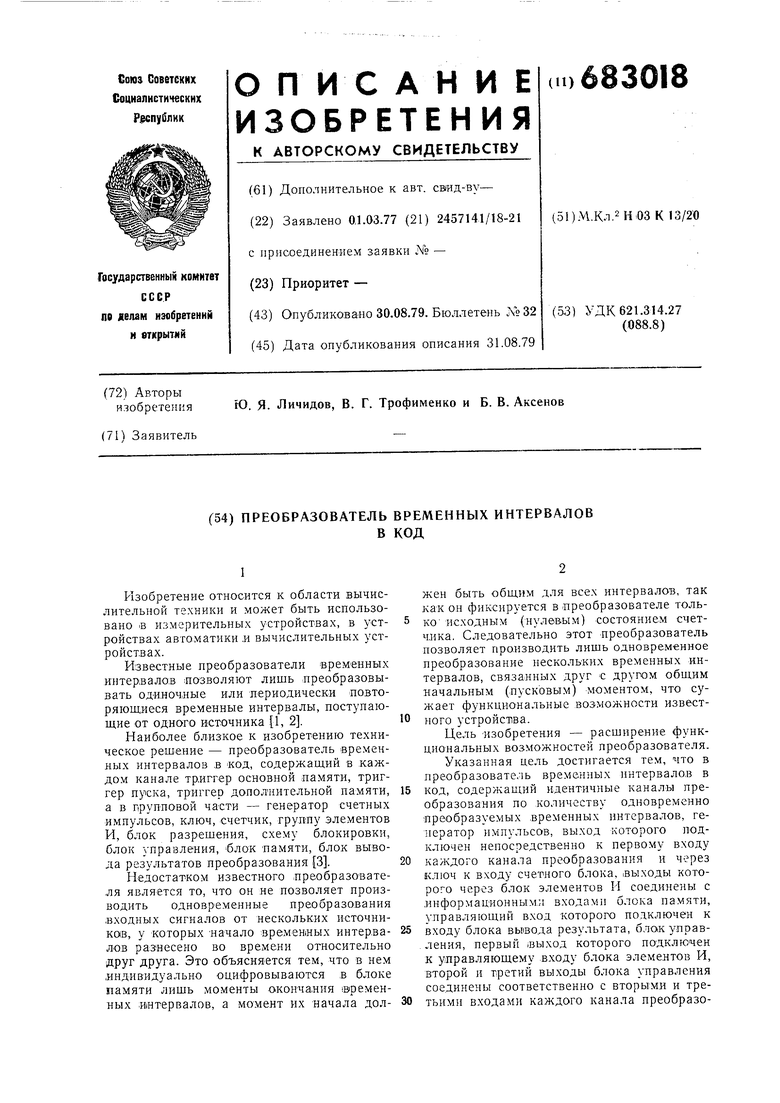

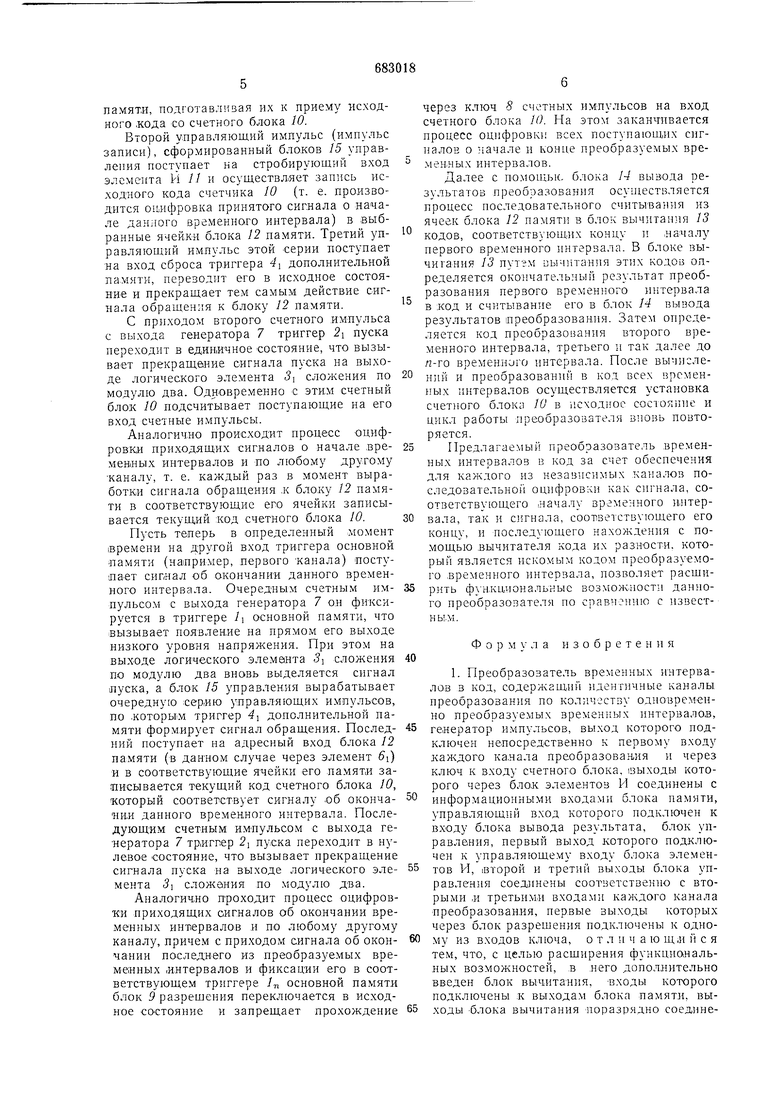

Ма фиг. 1 пр.иведена структурная схема предлагаемого преобразователя; на фиг. 2 - временная диаграмма его работы.

Преобразователь содержит входную часть, разбитую на п независимых каналов (по числу временных интервалов), и групповую часть. На фит. 1 обозначены входы, на которые поступает сигнал, соответствующий началу одного из преобразуемых временных интервалов, в.ходы, на .которые поступает сигнал, соответствующий концу одного 1из этих интервалов, триггеры /ь . . . , Л, основной памяти, триггеры 2, . . . , 2„ пуска, .информа.нионные входы которых подключены к прямым .выходам соответствуюп их триггеров осповной памяти, логнческ.ие элементы 5, . . ., 3„ сложения по . .два, входы которых связаны с прямыми выходами триггеров основной па.мятп и триггеров пуска, а выходы- с информационным.и входами триггеров 4,..., 4,1 дополнительной памяти, прямые

выходы последнего связаны с соответствующими входами элементов И 5i, . . . , 5п и (1, . . . , 6„.

Групповая часть преобразователя содержит генератор 7 счетных импульсов, выход которого соединен с одни.м .из входов ключа 8 и с сиихронкзирующим.и входами триггеров основной памяти и триггеров пуска всех :ка:нало.в, другой вход ключа подключен к выходу блока 9 разрещения, входы которого связаны с прямыми выходами всех триггеров основной памяти. Выход ключа подключен к счетному входу счетного блока 10, выходы которого через эле-мент И // соединены с информационными входа.м.н бло.ка /2 па.мяти, адресные входы которого подключены к выходам соответствующих эле.ментов И 5, . . . , 5„ и элементов И (,..., 6,1, а информационные выходы блока 12 памяти через вычитатель 13 соединены с входами блока М вывода результатов преобразо-ван.ия, управляющий выход которого подключен .к управляющему входу блока памяти. Входы блока 15 управления связаны с выходами логических элементов сложения по модулю два, а один из входов блока управления соединен со стробирующими входами грунпы элементов И /У, два других (Выхода бло.ка управления подключены к соот1ветствующим синхронизирующим входам всех триггеров дополнительной памяти.

Преобразователь работает следующим oi6pa30M.

Пусть на один .из входов триггера основной памяти, паприм.ер, первого канала поступил сигнал, соответствующий первого временного интервала. По первому счетному .импульсу с генератора 7 он фиксируется в триггере /i основной памяти. С появлением на njjriMOM выходе триггера 1 основной памяти высокого уровня напряжения бло.к 9 разрещания переключается, формируя на выходе сигнал управленпя ключом 8. С этого .момента последующие счетные импульсы с выхода генератора 7 начинают поступать через ключ 8 на вход счетного блока 10.

Одновременно с момента фиксации в триггере /, основной памяти сигпала о начале данного временного интервала на выходе логического элемента 3i .сложения по модулю два начинает фор.мироваться сигнал пуска, который поступает на инфор.мапионный вход тр.иггера 4 дополнительной памяти и на вход блока 15 управления. По этому сигналу блок 15 управления вырабатывает три управляющих импульса. Первый управляющий им;пульс .этой сери.и фиксирует сигнал иуска в триггере 4, дополнительной памяти. На его прямом выходе появляется сигнал с высоким уровнем напряжения, который через элемент 5| поступает на адресный вход блока 12 памяти как сигнал обпанк-мшя к огп ппп.-.-,,:,,,,,. „..,.....-..

памяти, подготавливая их к приему исходного .кода со счетного блока 10.

Второй управляющий имиульс (импульс записи), сформирозанный блоков 15 управления поступает ка стробирующий вход элемента И // и осуществл-яет запись исходного кода счетчика 10 (т. е. производится оцифровка принятого сигнала о начале временного интервала) в выбранные ячейки блока 12 памяти. Третий уиравляющий имлульс этой серии поступает на вход сброса триггера 4 дополнительной памяти, переводит его в исходное состояние и прекращает тем самым действие сигнала обращения к блоку 12 памяти.

С приходом второго счетного импульса с выхода генератора 7 триггер 2 пуска переходит в единичное состояние, что вызывает прекращение сигнала пуска на выходе логического элемента 3 сложения по модулю два. Одновременно с этим счетный блок 10 подсчитывает поступающие на его вход счетные импульсы.

Аналогично происходит процесс оцифровки приходящих сигналов о начале ,времеЕных интервалов и по любому другому каналу, т. е. каждый раз в момент выработки сигнала обращения ,к блоку 12 памяти в соответствующие его ячейки записывается текущий код счетного блока 10.

Пусть теперь в определенный момент времени на другой вход триггера основной памяти (например, первого канала) поступа-ет сиггнал об окончании данного временного интервала. Очередным счетным импульсом с выхода генератора 7 он фиксируется в триггере Л основной памяти, что вызывает появление па прямом его выходе низкого уровня напряжения. При этом на выходе логического элемента 5 сложения по модулю два вновь выделяется сигнал луска, а блок 15 управления вырабатывает очередную ;сер,ию управляющих импульсов, по которым триггер 4 дополнительной памяти формирует сигнал обращения. ПоследНИИ поступает на адресный вход блока 12 памяти (в данном случае через элемент б,) и в соответствующие ячейки его памяти записывается текущий код счетного блока 10, который соответствует сигналу об окончаНИИ данного временного интервала. Последующим счетным импульсом с выхода генератора 7 триггер 2i пуска переходит в нулевое состояние, что вызывает прекращение сигнала пуска на выходе логического элемента З сложения по модулю два.

Аналогично проходит процесс оцифровки нриходящих сигналов об окончании временных интервалов и по любому другому каналу, причем с приходом сигнала об окончании последнего из преобразуемых временных .интервалов и фиксации его в соответствующем триггере In основной памяти блок 9 разрещения переключается в исходное сОСтояние и запрещает прохождение

через ключ 8 счетных импульсов на вход счетного блока 10. На этом заканчивается процесс оцифровки всех поступающих сигналов о начале и конце преобразуемых вре.менных интервалов.

Далее с по.мощьк. блока 14 вывода результатов лреобразования осуществляется процесс последовательного считыва)1ия из ячеек блока 12 памяти в блок вычитан 1я /3 кодов, соответствующих концу и началу первого временного интервала. В блоке вычигания 13 путгм иычитания этих кодов определяется окончательный результат преобразования первого временного щггервала в код и считывание его в блок 14 вывода результатов преобразования. Затем определяется код преобразования второго временного интервала, третьего и так далее до л-го временного интервала. После вычислений и преобразований в код всех временных интервалов осуществляется установка счетного блока 10 в исходное состояние и цикл работы преобразователя вновь повторяется.

Предлагаемый преобразователь временных интервалов в код за счет обеспечения для каждого из независимых каналов последовательной оцифровки как сигнала, соответствующего началу временного интервала, так и сигнала, соответствуюидего его концу, и последующего нахождения с помощью вычитателя кода их разности, который является искомым кодом преобразуемого временного интервала, позволяет расщирить ,кш1ональные возможности данного преобразователя по сравнению с известным.

Формула изобретения

1. Преобразователь временных интервалов в код, содержащий идентичные каналы нреобразования по кол; честву одновременно преобразуемых временных 1нтервало.в, генератор и.мпульсов, выход которого нодк.тючен непосредственно к первому входу каждого канала преобразования и через ключ к входу счетного блока, выходы которого через блок элементов И соединены с информационными входами блока памяти, управляющий вход которого подключен к входу блока вывода результата, блок управления, первый выход которого подключен к управляющему входу блока элементов И, второй и третий выходы блока управления соединены соответствен1ю с вторыми ,и третьим.и входами каждого канала преобразования, нервые выходы которых через блок разрещения подключены к одному из входов ключа, о т л и ч а ю щ,и и с я тем, что, с целью расщирения функциональных возможностей, в него дополнительно введен блок вычитан)1я, входы которого подключены к вы.ходам блока памяти, выходы блока вычитания поразрядно соединены с .вхолами блока вывода результата, выход генератора импульсов подключен к четвертому зходу каждого канала преобразования, вторые выходы которых соединены с соответствущими входами блока управлен.ия, третьи л четвертые выходы каждого ка,нала преобразования соединены с адресными ,входами блока памяти.

2. Преобразолатель по п. 1, о т л л ч а ющ и и с я тем, что каждый канал преобразования содержит триггер основной памяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И, причем прямой выход тр.иггера основнОЙ памяти подключен к первому входу сумматора по модулю два, первому входу первого элемента И, первому выходу канала преобразования и к прямому входу триггера -пуска, инверсный вход которого является четвертым входом канала преобразования, прямой выход триггера пуска подключен нелосредствен/но к первому входу второго элемента И и через сумматор по модулю два к управляющему входу триггера дополнительной памяти н к второму выходу канала преобразования, выход триггера дополнительной памяти со:единен с вторыми входами первого и второго элементов И, выходы которых являются соответственно третьим и четвертым выходами канала преобразования, инверсный выход триггера основной памяти соединен с третьим входом ,второго элемента И, а инверсный выход триггера пуска соединяй с третьим входом тервого элемента И, прямой н инверсный входы триггера дополнительной памяти являются соответственно вторым и третьим входам.и канала преобразования.

Источники информации, принятые

во йннмание при экспертизе изобретения:

1.Авторское свидетельство СССР № 503359, кл. Н 03 К 13/02, 1973.

2.Авторское свидетельство СССР Хо .336793. кл. Н 03 К 13/02, 1970.

3.Авторское свидетельство СССР № 343375, кл. Н 03 К 13/20, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временных интервалов в код | 1981 |

|

SU942560A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1084852A1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1054828A1 |

| Преобразователь кода во временной интервал | 1983 |

|

SU1162050A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| Устройство для регистрации команд в резервированной системе управления | 1989 |

|

SU1633284A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

iI К ;-гХ

Г-ФЧЫ 1.и

fii-KT t

т J I:г:|j.i..

L...

Л

,1

Cf

Авторы

Даты

1979-08-30—Публикация

1977-03-01—Подача