rep основной памяти, триггер дополнительной памяти, сумматор по модулю два и элемент И, причем прямой выход триггера основной памяти подключен к первому входу сумматора по модулю два и к информационному входу тригтера дополнительной памяти, синхронизирующий вход которого яв::яется вторым входом канала преобразования, а выход соединен с вторым входом сумматора по модулю два, выход которого

иодключе.и к первому входу элемента И. второй вход которого сое.Тинек с инр.ерсньгм выходом триггера основной памяти вьгходы сумматора ;ii- модулю два и элемента И являются с-оотьетстьенно первым и вторым вьиодйми каигита преобразования, синхронизирукет.ий вход триггера ::-сновной гямяти япл -;гТ гя первымвходом канатл пресбряяг-яания , а первьйи второйвходы триггера основной памяти - входами 1стройствя

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временных интервалов в код | 1977 |

|

SU683018A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальное устройство с динамическим приоритетом | 1982 |

|

SU1049908A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

1. Г1РР:ОБРАЗОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД, содержащий идентичные каналы преобразования по количеству одновременно преобразуемых временных интервалов, генератор импульсов, выход которого подключен к первому входу каждого канала преобразования и к входу счетного блока, блок управления,входы которого соединены с первыми выходами каждого канала преобразования, а первый вьгход - с вторым входом каждого канал преобразования, блок памяти, выходы которого поразрядно соединены с первой группой входов вычислителя, выходы которого поразрядно соединены с входами блока вывода результата, о т л и ч а ю щ и iW с я тем, что, с Гслью расширения функциональных возможностей устройства, в него введены дополн1 тельньм блок памяти, блок приоритета, блок адресов считывания, блок адресов записи, коммутатор, блок сравнения кодов и элементы И, , причем первые выходы каждого канала преобразования через первую группу входов дополнительного блока памяти соединены с вх.)дами блока приоритета, выходы которого подключены к первой группе ХОДОВ блока элементов И и к адресным входам блоков памяти и вывода результата, а вторые выходы каналов преобразования через вторую группу входов дополнительного блока памяти подк.тючены к второй группе входов блока элементов И,,выходы которого через элемент ИЛИ подключен к управляющему входу памяти, выходы счетного блока через третью группу входов дополнительного блока памяти соединены с инфopмaц oнны ш входами блока памяти и второй группой входов вычислителя, а выходы блока адресов С S записи поразрядно соединены с первыми группами входов блока сравнения сл кодов и коммутатора, вторые группы входов которого поразрядно соединены с: с выходами блока адресов считывания, причем выход блока сравнения кодов соединен с первым входом элемента И, второй вход которого подключен к со тактирующему входу блока приоритета 4 Ю и выходу генератора импудьсов, а третий вход - к выходу разрешения за сл писи блока приоритета, счетный вход 05 блока адресов записи соединен с первым выходом блока управления, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом коммутатора, пер вым управляющим входом дополнительного блока памяти и четвертым входом элемента И, выход которого подключен к второму управляющему входу лтополнительного блока памяти и счетному входу блока адресов считывания. 2. Преобразователь по п. 1, отличающийся тем, что каждый канал преобразования содержит триг

Изобретение относится к облает : вычислительной техники и- может быть использовано в измерительных устройствах, в устройствах автоматики, контроля и вычислительных устройствах .

Известен преобразователь нременKbtx интервалов в код от нескольких источников, применекие которого возможно только в случае, если начала временныпс интервалов совпадают. Недостатком его является узкие функциональные возможности.

Наиболее близкое к изобретению теническое решение - преобразователь временных интервалов в код, содержащий в каждом канале триггер основной памяти, триггер дополнительной памяти, сумматор по модулю два, элемент И, а в групповой части генератор импульсов, счетчик, блок управления,, блок памяти, вычислитель, блок вь вода результатов преобразоааиия.

Недостатком известното преобразователя является то, что он не позволяет производить преобразование последовательности временных имтервалов непрерывно в каждом канале. Это объясняется тем, что повто.зное преобразование времен(ого инт1эрвала в код в любом канале возможно лишь после окончания преобразования временных интервалов по всем каналам и вь;дачи результатов.

Следовательно, этот преобразователь не позволяет преобразовывать в код последовательность вр еменных интервалов непрерывно, чтс- сужает функциональные возможности известного устройства.

П,ель изобретения - расширение функциональных н оз мож}-остей гтр с обр азователя.

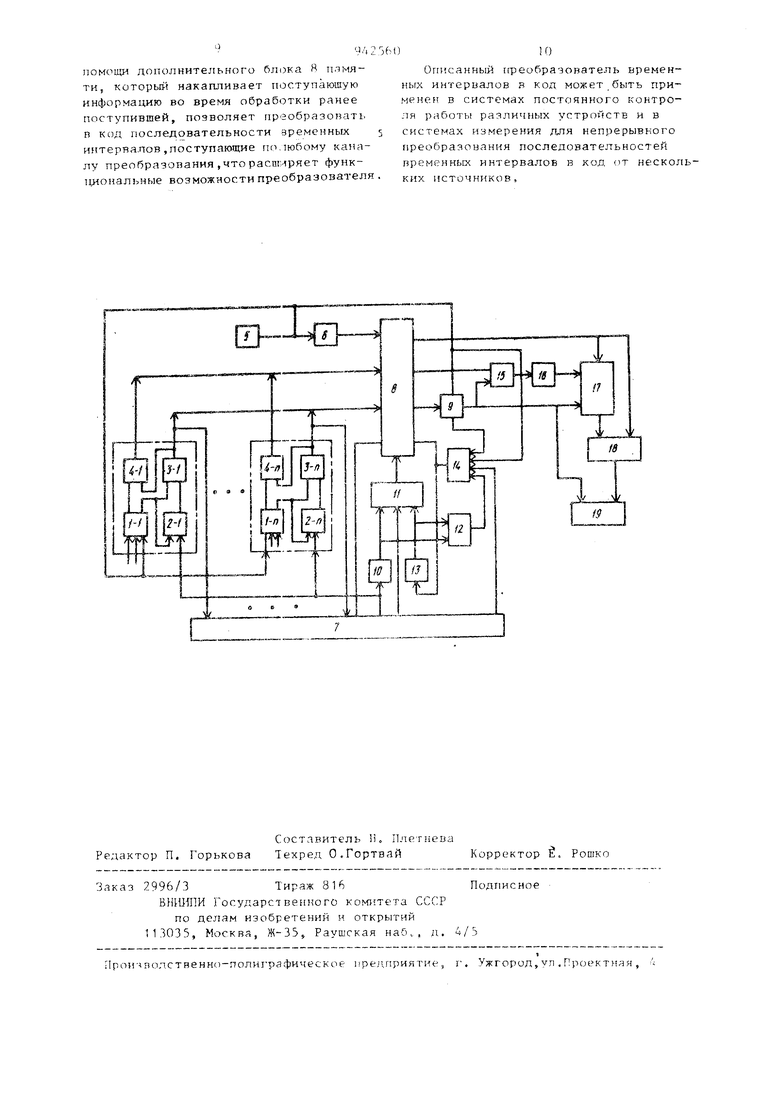

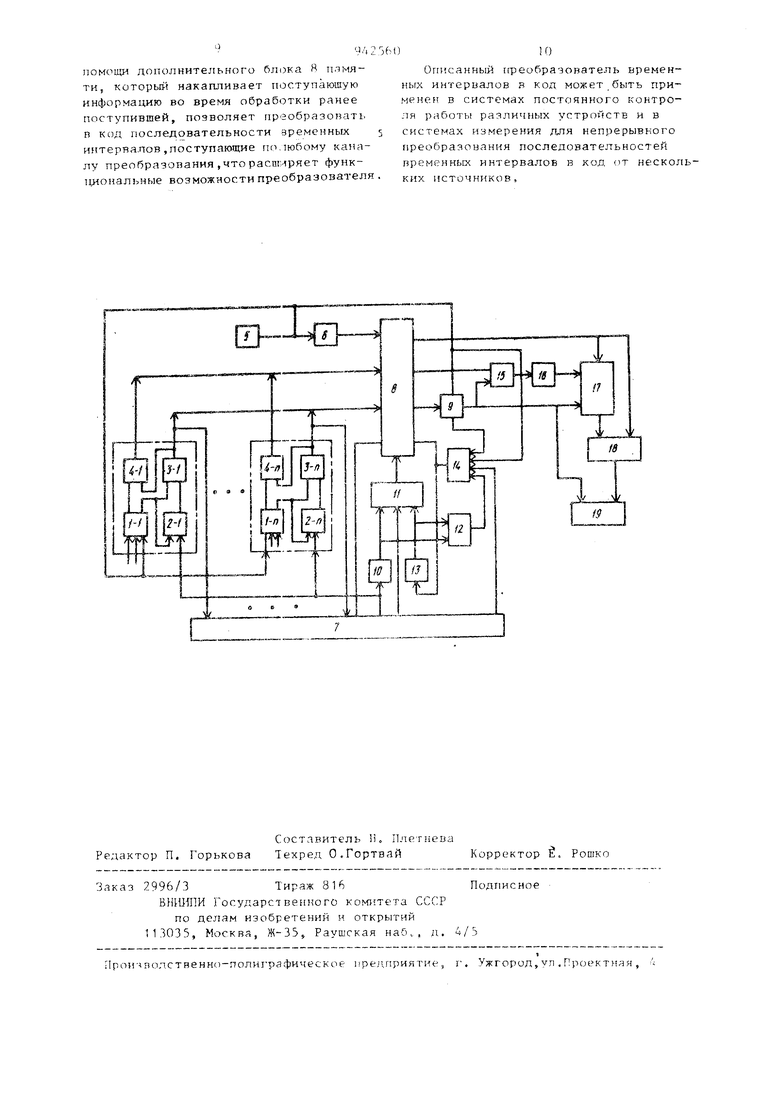

Цель достигается тем, что в преобразователь временньк интер1ии70Б в код, содержащий идентичные каналы преобразовани. по количеству одиовреMeiiio иреобразуемьсч временных интер-яалон, генератор импу;1ьсов, BbOiOj-i; которогп 1одключег-; к первому каждого канала преобг)азования и к взсоду с ч е т ii о г о б л ок a J блок у Ti р а в л е ни я нходы которого г.оединень: с первыми выходами каждого канала преобразования,, а первьй выход - с вторьм входом каждого канала преобразова1шя,. блок памяти5 вьжодь которого гюра.зряно соединены с первой группой вхсдов еычис.г ителя S выхо,пы которого поразрядно соединены с входами блока вывода результата, введены дополнительные блок памяти, боТок npHjpHTera б.гок ддресов считывания, блок адресо записи, коммутатор, блок сравнения кодов и элементы И, HHVi, первьге выходы калухого канала преобразования через первую группу входов дополнителььогс блока памяти соедкнет-Ш с нходамт блока гфиоритета, выходы которого подключены к первой rpyiine входов блока элементов И и к адрсгсным входам блоков памяти и вывода результата, а вторые выходы каналовпреобразования через вторую груг;п Блодоз дополните.пьгюго блока памяти подключены к второй группе НХОДОБ блока элементов И, выходы которогг; через элемен1 ИиИ подключен к упрев-ляюпшму входу блеска памяти, вькодьг с;четного блока через третью r-pvimv пхсдов дополнительного блока гтамяти соединены с инфopмaциonньi и входами блока памяти и рторон группой входов вычислителя, пьгходы блока адресов записи поразрядно соединены с пе выми группами входов блока сравнения кодов и коммутатора, вторые груп пы входов которых поразрядно соединены с выходами блока адресов считывания, выход блока сравнения кодов соединен с первым входом элемента И второй вход которого подключен к так тирующему входу блока приоритета и выходу генератора импульсов, а третий вход - к выходу разрешения запи си блока приоритета, счетный вход блока адресов записи соединен с первым выходом блока управления, второй третий и четвертьш выходы которого соединены соответственно с управляющим входом коммутатора, первым управляющим входом дополнительного блока памяти и четвертым входом элемента И, выход которого подключен к второму управляющему входу дополнительного блока памяти и счетному входу блока адресов считывания, причем каждый канал преобразования содержит триггер основной памяти, триг гер дополнительной памяти, сумматор по модулю два и элемент И, прямой выход триггера основной памяти подключен к первому входу сумматора по модулю два и к информационному входу триггера дополнительной памяти, сиихронизирующий вход которого является вторым входом канала преобразования, выход соединен с вторым входо сумматора по модулю два, выход которого подключен к первому входу элемента И, второй вход которого соединен с инверсным выходом триггера основной памяти, выходы сумматора по модулю два и элемента Н являются соответственно первым и вторым выходами канала преобразования, синхронизирующий вход триггера основной памя ти является первым входом канала преобразования, а первый и второй входы триггера основной памяти - вхо дами устройства. На чертеже приведена структурная схема преобразователя. Преобразователь содержит входную часть, разбитую на несколько независимых каналов (по числу одновременно преобразуемых временных интервалов) и группов ю часть. Каналы пре94 образования содержат тригтер, 1-1 1-h основной памяти, тригтеры 2-1 2-п дополн 1тельной памяти, cy мaтoры 3-1 - 3-i по модулю два, :з.пементы 4-1 - 4-п И. В групповую часть преобразователя входят генератор 5 импульсов, c4eTHbtfi блок 6, блок 7 управления, дополнительный блок 8 памяти, блок 9 приоритета, блок 10 адресов записи, ком -гутатор 11 и блок 12 сравнения кодов, блок 13 адресов считывания, элемент 14 И, блок 15 элементов Р1, элемент 16 ИЛИ, блок 17 памяти, вычислитель 18, блок 19 вывода результатов . Преобразователь временных интервалов в код работает следующим образом. В исходном состоянии сигналы на входах триггеров 1-1 - 1-h основной памяти отсутствуют, поэтому на выходах триггеров 2-1 - 2-Ч, сумматоров 3-1 - 3-h по модулю два, элементов 4-1 - 4-п И присутствует низкий уровень напряжения. Счетный блок 6 циклически считает импульсы генератора 5. Код на выходе блока 10 адресов записи совпадает с кодом на выходе блока 13 адресов считывания, поэтому низкий уровень напряжения на выходе блока 12 сравнения кодов блокирует элемент 1Д И, причем высокий уровень напряжения на выходе разрешения записи блока 9 приоритета и на четвертом выходе блока 7 управления подготавливают элемент 14 И к пропусканию сигнала считывания на управляющий вход дополнительного блока 8 памяти. При этом сигналы на других выходах блока 9 приоритета и остальных выходах блока 7 управления отсутствуют. Выходы блока 10 адресов считывания через коммутатор подключены к адресным входам дополнительного блока 8 памяти. Пусть на вход одного из триггеров 1-1 - 1-й основной памяти, например, первого канала преобразования поступил сигнал, соответствую ций началу времен}юго интервала в этом канале. По приходе импульса с генератора 5 этот сигнал фиксируется в триггере 1-1 основной памяти, вызывая появление высокого уровня напряжения на выходе сумматора 3-1 по модулю два, который поступает на соответствующ} й вход дополнительного блока 8 памяти и на один из входов

блока 7 управ-че тя. По этому сигналу блок 7 управления вырабатьгвает на своих нькодах уг рлвляюа1ие сигналь). Управляющий ситнал с второго выхода блока управления, поступая на коммутатор 11, проиэво;1ит подключение нькода блока 10 адресов записи к адресным входам допол 1ительного блока 8 падмяти. Одновременно сигнал с четвертого выхода блока 7 управления блокирует ялемент 14 И, Управляющий сигнал с третьего выхода блока 7 управления производит заттись в дополчительнь;й блок 8 памяти и;тформацин, состоящей из текущего кода со счетного блока 6 и позиционного кода адреса канала преобраяовлнич, который образуется путем записи в разряде информации, соответствующем выходу сумматора 3-1 по модулю даа, логргческой 1, Управляющий сигнал с первого выхода блока 7 управления поступает на синхронизирукидин вход ТОИР гера 2-1 дополнительной гымяти, ,

в р|;чультат(

г о в

танавливая

чего на выходе су.мм;-. по молу;1ю два появляется низ.ки уронен/, напряжения. Блок 7 управления возвра щается в ;-:сходное состояние, Угтрав,;тяюпц-1Й импульс с первого вь/хода блока 7 управления также пос упает на счетный вход блока 10 записи, ;1пменяя код адреса на его выходе на следующий. При этом на BMXoiie блока 12 сравнения кодоз появляется высокий уровень напряжения, подготавливая элемент 14 И к пропусканию сле; унэщего импульса с генератора 5 импульсов на управляющий дополнителького блока 8 памяти (если к этому моменту не поступили новые сигналы на входы триггеров 1 -1 -|-п основной памяти) J который производит считывание записанной перед этим информации. При этом часть информаид и, содержащая позиционный код адреса канала преобразовария, переписывается с выходных регистров допслнительного блока памяти в блок 9 приоритета. По окончании считьшания код адреса на выходах блока 13 адресов считывания изменяется на следующий и вновь совпадает с кодом адреса на выходах блока адресов задиси, Поэто -г/ низкий уровень напряжения на выходе блока 12 сравнения кодов блокирует элемент 14 И, При

поступлении импу.пьса с reMifp-i иа вход тактироваяи.я б.юкл Ч ;:рь:орцтета на его выходе форми1зуеГСя сигна поступающий на адресньп Плока 17 памяти, который произвоц 3aniicti в первые ячейки кода Сгетного блока 6 с выходных peiHCipop, :ополнигельного блока 8 памяти. После поступления следукндего импульса с i eneратора 5 импульсов на вход тактирования блока 9 приоритета сигнал на его выходе сбрасьшается, а на выходе разрешения записи ПОЯВЛЯРТСЯ выс:окир 1 уровень наггряжения, подготавливающий элемент к формированию следующег импульса считывания.

Таким образом произошел процесс оцифровки начала временного интервала в первом канале преобразования и запись этого значения в блок памяти. Аналогично происходит процесс oL lфровки гфиходящих сигналов о начале временного интервала по любому другому каналу.

Пусть теперь в определенный момен времени isa другой exo/i триггера осно ной ггамяти, например, nepnciro канала преобразования постуг;нт сигнал об окончании временного интервала. Очередным импульсом с генератора 5 он фиксируется Б триггере 1-1 основной памятиJ что вызывает тюявление на е г о пр я МОм нькод е низко г о, а на и кверсном - высокого уровней напряжения в результате чего на ыxoдax сумматора 3-1 и элемента Д-1 И появятся высокие уровни напряжег.ия. Бло 7 управления вьграбатывает очередную серию управляющих импульсов, в результате чего в дополнительный блок памятн будет записана информацияj Содержащая текущий код со счетного блока 6, пози1шонньш код первого канала преобразования и второй позидионны код первого канала преобразоBa4V H. который образуется при записи .по)ической в разряд информации, ссс-тветствую1дий выходу элемента 4-1 И, и который характеризует то, что в

первом канале преобразования поступил сигнал конца временного интервал а.

Когда произойдет считывание этой информации (а;фес на выходе блокг адресой счить вания будет соответствовать адресу, по котором. бьша про изяедена запись этой и;-{формац-ии,| на выходные регистры дополнительното блока 8 памяти,позиционный код адреса канала записывается в блок 9 приоритета, а второй позиционньп; адрес канала преобразования подается н первую группу входов блока 15 элемен тов И, По приходе следующего импульса с генератора 5 импульсов на вход тактирования блока 9 приоритета на его первом выходе появляется сигнал который поступает на адресные входы блоков 17, 19 памяти и вьщачи резуль тата и одновременно через блок 15 элементов И на управляющий вход блока 17 памяти, производя считывание из него оцифрованнохо значения начала временного интервала, которое подается на входы вычислитепя 18, На другие входы вычислителя 18 подается код счетнйго блока 6 с выходных регистров дополнительного блока 8 памяти (оцифрованное значение конца временного интервала), Вычислитель 18 определяет число промежуточных состояний счетного блока 6 меяшу эти ми значениями с учетом начального состояния счетного блока 6 (оцифрованное значение начала временного ин тервала) ,. которое определяет код, соответствующий данному временному интервалу. С выходов вычислителя 18 код заг1исывается в блок 19 вывода ре зультата. Аналогично происходит преобразование в код временного интервала при поступлении сигна Ш об окончании временного интервала в любом другом камале преобразования. В случае, если одновременно на входы одних триггеров основной памяти поступят сигналы, соответствуюш 1е началу временного интервала в этих каналах преобразования, а на входы других триггеров основной памяти сигналы, соответствующие колцам временных интервалов в этих каналах преобразования 5 то работа устройства отличается лишь тем, что блок приори тета будет поочередно вьу;авать позиционные коды адресов каналов преобразования, по которым пришли сигналы, после каждого импульса, поступающего на тактирующий его вход. При этом в зависимости от того, соот ветствуют эти сигналы началу или кон цу временного интервала, что определяется по второму пoзициOfIHOf4y коду адреса камала, будет производиться пибо запись оцифрованного значения 1 ачала временного интервала в блок 17 памяти, либо вычисление кода преобразования и запись его в блок 19 вывода результата. Если во время выполнения этих операций поступят новые сигналы начала или конца временных интервалов, то информация об этом будет эаписьтаться в дополнительньн ; блок 8 памяти в порядке поступления этих сигналов. Обработка накопленной информации будет производиться аналогично описанному. Таким образом, дополнительный блок 8 памяти, блоки 10, 13 адресов записи и считывания, коммутатор 11 используются для приема информации о поступивших сигналах в виде последовательных слов, содержащих текущий код со счетного блока 6 в момент поступления сигнала, позиционньй код каналов преобразования, по которым поступили сигналы и второй позициокньй код канала преобразования, по которо:-;у поступил сигнал, соответствующий концу временного интервала, с последующим их считыванием в порядке поступления, но с другой скоростью. Благодаря этому, если на входы каких-либо каналов преобразования будут поступать последовательности временных интервалов, то преобразователь последовательно, в порядке их поступления преобразует их в код и запищат в блок 19 вывода результата. По окончании поступления на входы триггеров основной памяти сигналов и после выдачи из дополнительного блока 8 памяти накопленной информации (код адреса на выходе блока 10 адресов записи совпадает с кодом адреса на выходе блока 13 адресов считывания, при этом низкий уровень напряжения на выходе блока 12 сравнения кодов блокирует элемент 14И, запрещая дальнейшее считывание из него) и вь,ачи всех позиционных кодов адресов из блока 9 приоритета (высокий уровень напряжения на его выходе разрешения записи) преобразователь временных интервалов Б код возвращается в исходное состояние. Предлагаемый преобразоват.ель временных интервалов в код, выполняя функции известного устройства, и, кроме того, за счет организации непрерывной обработки поступающей информации о поступающих сигналах при

помощи дополнительного бшжа Я плмяти, которьй накапливает тюступаюшую информацию во время обработки ранее поступившей, позволяет преобразоват. в код последовательности временных интервалов,поступающие по.шбому каналу преобразования,чтораспмряет функ1Ц1Ональные возможности преобразователя Г

Описанный феобразователь временных интервалов в код может быть применен в системах постоянного контроля работы различных устройств и в 5 системах измерения для непрерывного яреобразонания последовательностей временнЬЕх интервалов в код от нескольких источников.

| ЗЮЗНАЯ fплтвгтно^;'?х:":^;гсн;Ш:_J>&Hb?HpT;;:HA I | 0 |

|

SU343375A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь временных интервалов в код | 1977 |

|

SU683018A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-05-30—Публикация

1981-01-12—Подача