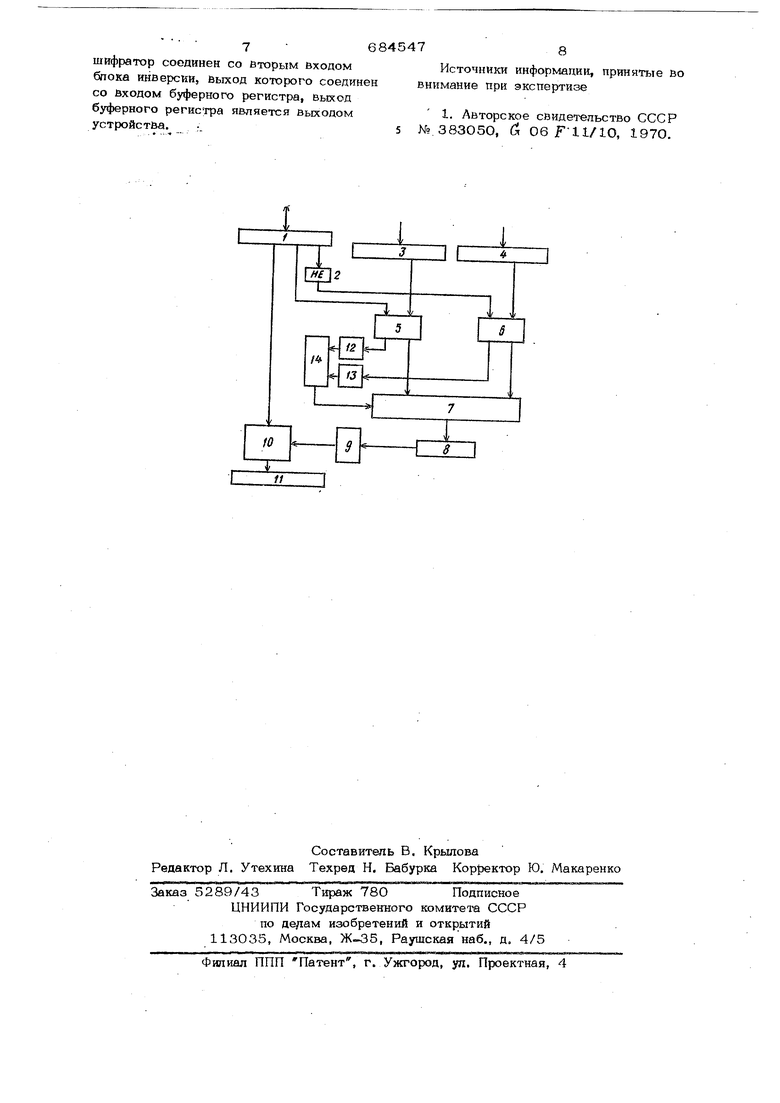

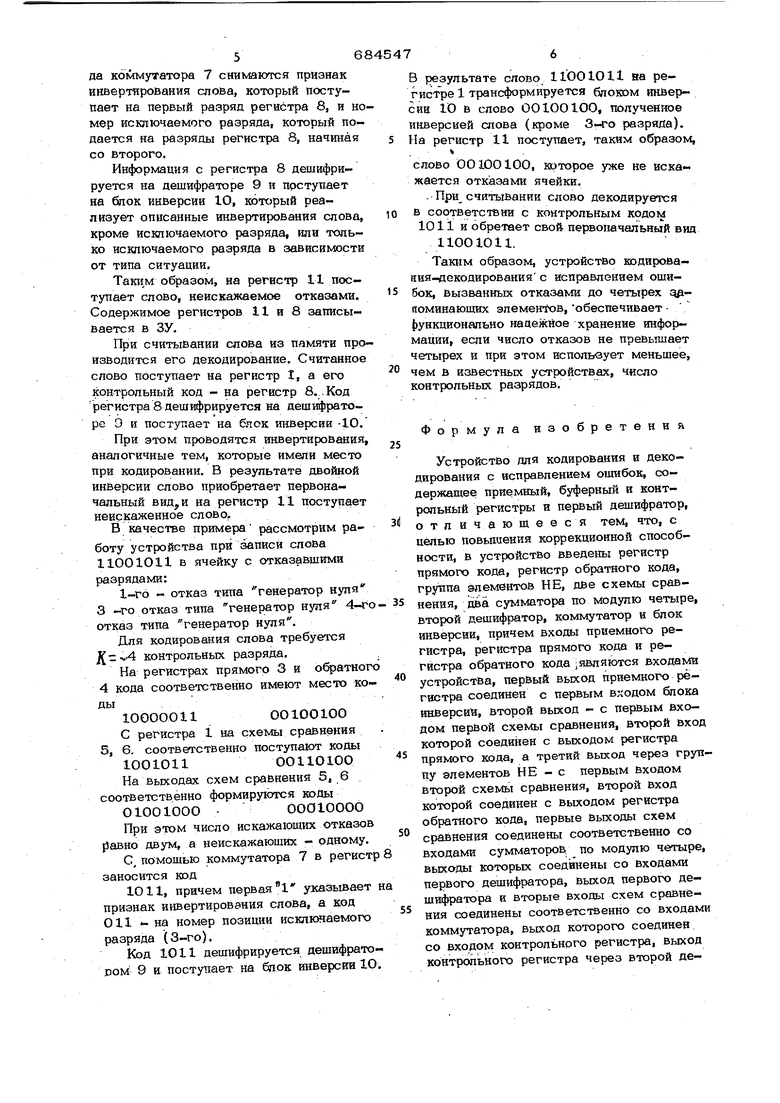

обратного кода. Первые выходы схем сравнения соединены соответстеенно со входами сумматоров по. модулю четыре, Выходы которых соединены со входами первого дешифратора. Выход первого де шифратора и Вторые Выходы схем сравнения соединешл соответственно со вход ми коммутатора, Выход которого соединен со входом контрольного регистра. Выход контрольного регистра через второй дешифратор соединен со вторым Вхо дом блоха инверсии, выход которого сое нен со Входом буферного регистра. Выход буферного регистра является Выходом устройства. Использование информации о типе и локализации отказа в изобретении позволяет снизить число контрольных разрядов /{ , йеобходимых для коррекциитрехкратных ошибок, до Я %,, где П - длина кода. Структурная схема устройства для кодирования и декодирования с исправлением ошибок, вызванных отказами до четырех запоминающих элементов, представлена на чертеже. Устройство состоит из приемного ре гистра 1, группы элементов НЕ 2, регистров прямого 3 и обратного 4 кода, схем сравнения 5,. 6, коммутатора 7, контрольного регистра 8, дешифратора 9 блока инверсии 10, буферного регистра И, сумматоров по модулю четыре 12 и 13 и Деши4 атора 14. Приемный регистр 1, а также регис три прямого 3 и обратного 4 кода соединены с ЗУ (на черт, не показано). Входы схемь сравнения 5 соединены с регистрами 1 и 3, а входы схем сравнения 6 - с регистром 4 и через группу элементов НЕ 2 регистром 1. Выходы cxeMsi сравнения 5, 6 соединены с коммутатором 8, который подсоединен к контрольному регистру 8. Регистр 8 через дешифратор 9 подключен к блоку инверсии 1О, вход которого соединён с регистром 1, а выход - с регистром 11; Схемы сравнена 5, 6 соединены соответственно через сумматоры по модулю четыре 12, 13 с деши ратором 14, который подключен к коммутатору 7. 7 При записи в ЗУ слово подвергается кодированию. При этом слово поступает на регистр 1, записывается в выбранную ячейку ЗУ и считывается на регистр 3. В ту же ячейку записывается обратный код слова, хранимого в регистре 1, и считывается на регистр 3. Схема сравнения 5 по несовпадению кодов на регистре 1 и регистре 2 выявляет позиции искажающих отказов. Аналогично схема сравнения 6 по несовпадению кода обратного, хранимому на регистре 1, и содержимого регистра 4, выявляет позиции неискажаюших отказов, Сумматоры 12 и 13 определяют число отказов каждого вида. При отказе трех запоминающих элементов возможны следующие четыре случая: Т - имеют место один искажающий отказ и дванеискажающих} jf - имеют iAecTO два искажающих отказа и один неискажающий; )(/ - имеют место три искажающ 1х отказа; -tK - имеют место три неискажающих отказа. В первом случае инвертируется разряд, подвергаемый искажению, и номер его записывается в контрольный регистр 8, начиная со второго разряда, а в первый разряд записывается О. Во втором случае инвертируется всё слово, кроме неискаженного отказом разр11да, номер последнего записывается в регистр 8, начиная со второго разря. да, а в первый разряд записывается 1. .В третьем случае инвертируется все слово, кроме одного из разрядов. Не входящего в число искажаемых, номер его записывается в регистр 8, начиная со Второго разряда, а в первый разряд записывается 1. В четвертом случае инвертируется один разряд, не входящий в число разрядов с неискажающими отказами, номер последнего записывается в контрольный регистр 8, начиная со второго разряда, а в первый разряд записывается О. Двухкратные и одиночные отказы могут быть сведены к указанным четырём ситуациям. При отсутствии отказов интегрируется первый разряд слова, а в ригистр 8 заносится код ОООО... О. Дешифратор 14 выявляет тип ситуации и вьщает управляющий сигнал- на коммутатор 7, на который также подаются сигналы со схем сранения 5, 6. С Выхода коммутатора 7 сникшются признак инвертирования слова, который посту пает на первый разряд регистра 8, и но мер исключаемого разряда, который подается на разряды регистра 8, начиная со Второго. Информация с регистра 8 дешифрируется на дешифраторе 9 и поступает на блок инверсии 10, который реализует описанные инвертирования слова, кроме исключаемого разряда, ила только исключаемого разряда в зависимости от типа ситуации. Так1ш образом, на регистр 11 поступает слово, неискажаемое отказами. Содержимое регистров II и 8 записывается в ЗУ, При считывании слова из памяти про изводится его декодирование. Считанное слово поступает на регистр t, а его контрольный код - на регистр 8.,Код регистра 8 дешифрируется на дешифраторе О и поступает на блок инйерсии -Ю. При этом проводятся инвертирования, аналогичные тем, которые имели место при кодировании. В результате двойной инверсии слово приобретает первоначальный виДуИ на регистр 11 поступает неискаженное слово, В качестве примера рассмотрим работу устройства при записи слова 11001011 в ячейку с отказавшими разрядами: - отказ типа генератор нуля 3-го отказ типа генератор нуля 4-Г отказ типа генератор нуля. Для кодирования слова требуется К - контрольных разряда. На регистрах прямого 3 и обратног 4кода соответственно имеют место ко ды 1ООООО11ОО100100 с регистра 1 на схемы сравнения 5, 6, соответственно поступают коды 1О01О11ОО11О100 На выходах схем сравнения 5, 6 соответственно формируются коДы О1О01000000100ОО При этом число искажающих отказов равно двум, а неискажаюших - одному. С, помощью коммутатора 7 в регист заносится код 1011, причем первая указывает признак инвертирования слова, а код 011 - на номер позиции исключаемого разряда (3-го). Код 1011 дешифрируется дешифрато ром 9 и иоступает на блок инверсии 10 в результате слово 1Ш01О11 ва регистре 1 трансформируется блоком tniBepсии 10 в слово ОО1001ОО, голученное инверсией слова (кроме 3-го разряда). На регистр 11 поступает, таким образом, слово ООЮ0100, шторое уже не искажается отк)азами ячейки. - При считывании слово декодируется в соответствии с контрольным кодом 1011 и обретает свой первоначальный вид 11001011. Таким образом, устройство кодирования-декодирования с исправлением ошибок. Вызванных отказами до четырех дрпоминающих элементов,обеспечивает {)ункционвльно надежное хранение информации, если число отказов не превышает етырех и ири этом испольвует меньшее, ем в известных устройствах, число онтрольных разрядов. Формула изобретений Устройство для кодирования и декодирования с исправлением ошибок, содержащее приемный, буферный и контрольный регистры и первый дешифратор, о тл и ча юще е ся тем, что, с целью повыхиения коррекционной способности, в устройство введены регистр прямого кода, регистр обратного кода, группа элементов НЕ, две схемы сравнения, даа, сумматора по модулю четыре, второй дешифратор, коммутатор и блок инверсии, причем вхошл приемного регистра, регистра прямого кода и регистра обратного кода ;являются входами устройства, первый выход приемного регистра соединен с первым входом блока инверсии, второй выход - с первым входом первой схемы сравнения, второй вход которой соединен с выходом регистра прямого кода, а третий выход через группу элементов НЕ - с первым входом второй схемы сравнения, второй вход которой соединен с выходом регистра обратного кода, первые выходы схем сравнения соединены соответственно со входами сумматоров по модулю четыре, выходы которых соединены со входами первого дешифратора, выход первого дешифратора и вторые Входы схем сравнения соединены соответственно со входами коммутатора, выход которого соединен. со входом контрольного регистра, выход контрольного регистра через второй де 76845478

шифратор соединен со вторым входомИсточники информации, принятые во

блока инверсии, выход которого соединен со Входом буферного регистра, выход буферного регистра является выходом устройства. :.

внимание при экспертизе

I. Авторское свидетельство СССР 5 №383050, И 06F-11/IO, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство | 1978 |

|

SU746745A1 |

| Устройство для кодирования | 1976 |

|

SU622086A1 |

| Устройство для коррекции ошибок в блоке памяти | 1978 |

|

SU765886A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

Авторы

Даты

1979-09-05—Публикация

1976-10-14—Подача