От7

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2384899C2 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

Изобретение относится к запоминающим устройствам и может найти применение в цифровых вычислительных машинах, выполненных на функциональных узлах с большой степенью интеграции. Цель изобретения - повышение быстродействия запоминающего устройства. Поставленная цель достигается за счет введения блока исправимости ошибок, который содержит дешифратор 13 кратности ошибок, группу 15 регистров, коммутатор 16, элемент 19 сравнения, первую группу элементов ИЛИ 17, вторую группу элементов ИЛИ 20, элемент 21 задержки, регистр 18, узел 13 памяти контрольных групп. Запоминающее устройство позволяет практически сразу определить исправимость ошибок в считанном слове, а также уменьшить в среднем на 50% время получения достоверной информации при обращении к ячейке накопителя с ошибками, вызванными отказами запоминающих элементов. 1 з.п.ф-лы, 2 ил.

фиг. 2

Изобретение относится к запоминант- щим устройствам и может найти прим(- нение в цифровых вычислительных машинах, выполненных на функциональных уз лах с большой степенью интеграции.

Цель изобретения - повьпиение быст- роцействия запоминающего устройства.

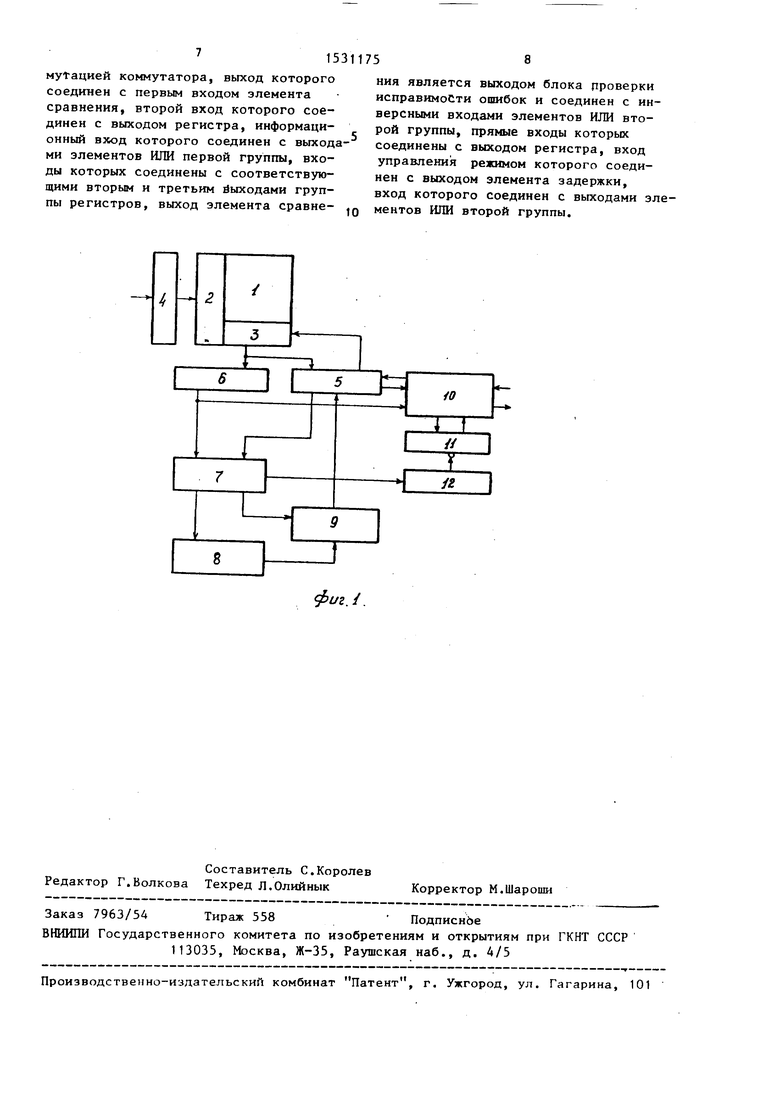

На фиг. 1 прецставлена структурная схема запоминающего устройства, на фиг. 2 - схема блока проверки испра- вимости ошибок.

Запоминающее устройство содержит блок памяти, состоящий из накопителя 1, адресного 2 и разрядного 3 блоков, регистра 4 адреса, регистры прямого 5 и инверсного 6 кода, блок 7 сравнения счетчик 8, распределитель 9 неисправных разрядов, блок 10 кодирования, буферный регистр 11, блок 12 провер-, ки исправимости ошибок (блок местного управления, синхронизирующий работу всех блоков запоминающего устройства, не показан).

Блок 12 содержит уаел 13 памяти контрольных групп, дешифратор 14 кратности ошибок, группу 15 регистров, коммутатор 16, первую группу 17 элементов ИЛИ, регистр 18, элемент 19 сравнения, вторую группу элементов ИЛИ 20, элемент 21 задержки.

Устройство работает следующим образом.

При записи адрес ячейки, в которую необходимо записать информацию, посту пающую в блок 10, подается на вход регистра 4.

В блоке 10 слово кодируется применяемым корректирующим кодом и записывается в накопитель 1 через регистр 5 по данному адресу.

При считывании адрес ячейки, на которую нужно считать информацию, поступает в регистр 4, откуда и передается в блок 2. Слово по данному адресу считывается из накопителя 1 и через блок 3 поступает в регистр 5 и блок 10, где проверяется с помощью контрольных проверок есть ли ошибка в слове. Если ошибки нет, то слово поступает на выход системы.

В случае, если ошибка иметеся, то слово инвертируется и записывается в накопитель 1 по тому же адресу- и вновь считывается, поступая теперь уже Б регистр 6. Далее слово передается с инверсного выхода регистра 6 в блок 10, где снова проверяется на наличие ошибки. Если ошибки нет, то. с-поно поступает на выход устройства. Если имеется, то содержимое регистров 5 и 6 поступают на блок 7 сравнения. На выходе этой схемы появляются единицы в тех рафядах, в которых совпадают coдepж iмoe регистров 5 и 6, т.е. в тех разрядах, в которых происходят отказы. Эти единицы поступают на счетчик 8, а их расположение передается в распределитель

10,где каждый раз проверяется на наличие ошибки. Подобные проверки осуществляются до тех пор, пока блок 10 кодирования не выдает сигнал об отсутствии ошибки.

Одновременно с работой счетчика 8 по перебору комбинаций информация об отказавших разрядах поступает с блока 7 в блок 12 проверки исправимости ошибки, который определяет будет ли найденная схемой перебора комбинация в позициях отказавших разрядов единственной, удовлетворяющей алгоритму декодирования (т.е. истинной, достоверной информацией после декодирования) или нет. Это может быть реализовано, например, таким образом. Позиционный ряд считанных разрядов поступает в узел 13 памяти контрольных групп, с помощью которого определяется, какими контрольными группами проверяются отказавшие разряды. Данная информация фиксируется группой регистров .15, в которой будет задействовано столько регистров, какова кратность ошибки, указанная в дешифраторе 14, а именно в первый из регистров группы 15 записываются те контрольные группы, которые проверяют первый из отказавших разрядов в слоев, во второй регистр - те контрольные группы, которые проверяют второй отказавший разряд слова и т.п. При этом в разряд каждого из регистров группы 13 записываются 1, если соответствующая контрольная группа проверяет это отказавший разряд. В противном случае в соответствующий разряд записывается О. По окончании записи содержимое первых двух регистров группы 15 через группу поразрядных элементов ИЛИ 17 поступает на регистр 18. Каждое последующее слово (третье, четвертое и т.д

515

с регистров группы 15 через коммутатор 16 считывается на элемент 19 сравнения. При этом коммутатор 16 поочередно подает на вход - лемента 19 содержимое (j-2 регистров группы 15, где j - это кратность отказа, опрв - деленная дешифратором 14 группы (т.е. количество задействованных в данном случае регистров группы 15). На элемент 19 сравнения считывается логическая дизъюнкция одноименных разрядов первого и второго слова (т.е. содержимое рабочего регистра 18) и происходит сравнение с содержимым последующего (первоначально третьего) регистра группы 15. Если очередное слово не равно содержимому рабочего регистра 18, то оно считьгоается из регистров группы 15 через коммутатор 16, группу элементов ИЛИ 20, элемент 21 задержки и записывается в рабочий регистр 18, после чего оно сравнивается с содержимым четвертого регистр.а и т.д. Эта последовательность действий повторяется до тех пор, пока не будет либо сосчитан последний регистр группы 15, либо пока не появится сигнал Неисправимая ошибка.

В первом случае ошибка путем перебора будет исправимой, т.е. первое слово, которое будет образовано счетчиком 8 и которое не выдает сигнал Неисправимая ошибка декодирования, будет единственным и искомым.

В случае, если элемент 19 сравнения выдает сигнал Неисправимая ошибка, то это значит, что подобной схемой перебора ошибка однозначно исправлена быть не может.

Таким образом, предлагаемое запоминающее устройство позволяет практически сразу определить исправимость ощибок в считанном слове, уменьшить в среднем на 50% время получения достоверной информации при обращении к ячейке накопителя с ошибками, вызванными отказами запоминающих элементов.

Формула изобретения

дом блока кодирогьтния, вторые информационные вход и выход которого являются соответственно информационными входом и выходом устройства, а третьи информационные вход и выход соединены соответственно с первыми информационными выходом и входом регистра прямого кода, вторые информационные вход и выход которого соединены соответственно с информационными выходом и входом блока памяти, адресные входы которого являются адресными входами устройства, вход регистра инвер-еного кода соединен с информационным выходом блока памяти, а выход соединен с четвертым информационным входом блока кодирования и первым входом блока сравнения, второй вход которого соединен с третьим информационным выходом регистра прямого кода, первый выход блока сравнения соединен с входом счетчика, выход которого соединен с входом количества неисправных разрядов распределителя неисправных разрядов, вход позиции неисправного разряда которого соединен с вторым вьосодом блока сравнения, а выход распределителя неисправных разрядов соединен с

третьим информационным входом регистра прямого кода, отличающее- с я тем, что, с целью повьпиения быстродействия устройства, оно содержит блок проверки исправимости ошибок, выход которого соединен с входом управления буферного регистра, а вход соединен с третьим выходом блока сравнения.

нения, две группы элементов ИЛИ,

элемент задержки, регистр, узел памяти контрольных групп, вход которого

соединен с входом дешифратора кратности ошибок и является входом блока п проверки исправимости ошибок, выход узла памяти контрольных групп соединен с первым входом управления коммутацией коммутатора и с первым информационным входом группы регистров, второй информационный вход которой соединен с первым информационным выходом дешифратора кратности ошибок, второй информационный пыход которого соединен с вторым входом управления коммутацией коммутатора, выход которого соединен с первым входом элемента сравнения, второй вход которого соединен с выходом регистра, информаци- онный вход которого соединен с выходами элементов ИЛИ первой группы, входы которых соединены с соответствующими вторым и третьим выходами группы регистров, выход элемента сравне- ,Q

фиг. /.

ния является выходом блока проверки исправимоСти ошибок и соединен с инверсными входами элементов ИЛИ второй группы, прямые входы которых соединены с выходом регистра, вход управления режимом которого соединен с выходом элемента задержки, вход которого соединен с выходами элементов ИЛИ второй группы.

| 0 |

|

SU386319A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-23—Публикация

1988-01-07—Подача