(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Устройство для кодирования и декодирования с исправлением ошибок | 1976 |

|

SU684547A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

I

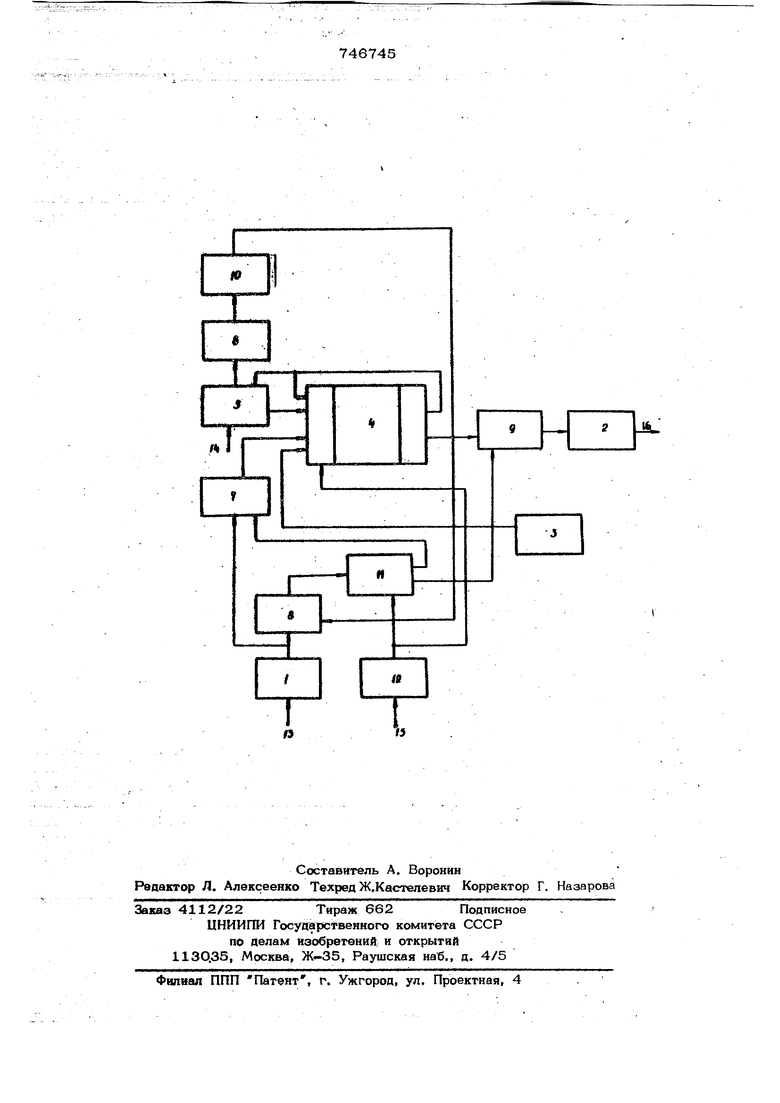

Изобретение относится к вычислительной технике- и может быть использовано при разработке устройств памяти на сдвиговых регистрах с большой степенью интеграции.

Известно запоминающее устройство (ЗУ) на сдвиговых регистрах, в которых реализуется динамическое хранение информации. Каждый сдвиговый регистр хранит одноименные разряды всех слов, информационное слово записывается со входа ЗУ параллельно на входы всех сдвиговых регистров, затем происходит сдвиг информации и в освободившиеся первые разряды записывается последующее слово, выходы сдвиговых регистров подключаются к их входам и при последующих сдвигах информация вновь передвигается в пределах сдвигового регистра от входа к выходу 1

Недостатком указанного устройства является искажение информации в случае наличия отказавших элементов, причем, ввиду сдвигового характера накопителя.

каждый отказавший элемент влияет на все информационные разряды, которые сдвигаются через него.

Наиболее близким к предлагаемому является ЗУ на сдвиговых регистрах, содержащее накопитель, генератор фаз, блок адресных цепей, входной и выходной регистры 2.

Недостатком этого устройства явлйет- ся отказ накопителя при выходе из строя,

ш запоминающих элементов.

Цель изобретения - повышение надежности ЗУ за счет устранения отказов основного блока памяти.

Поставленная цель достигается тем,

15 что в ЗУ содержащее основной блок памяти, первый вход которого соединен с выходом адресного блока, управляющий генератор, выход которого соединен со вторым входом основного блока памяти,

746745

4 исправмостей сдйиг(жых регистров зависит от способа кодирования ситуаций. На11ршйё{5, кшйройание может производиться следукицим образом: ОО - нет Искажени:); О1 - искажается О; 1О -искажается 1. Искажаться бпновременно 1 и О не могут при предположении, что имеются отказы (генераторы 1 и О), так как ха- рактер искажения всей информации, про- двнгак щей сй через сдвиговый регистр. Определяется видом отказа ближайшего к вь1ходу запоминаюшего элемента. Таким образом, режим тестового контроля заканчивается заполнением первого дополнительного блсжа 1О. При записи информационного слова с шины 13 через входной регистр 1, адрес которого подается с шины 15 на адресный блок 12, в бло- ке 8 кодирования происходит кодироваййё на о 5н6Ёйнй ДёйнЫХ о значении раз- рядов информЕайШМого слова и состояния сдвиговых регистров, которые считываются из блока 10памяти при каждом обращений к HStwiy при записи. Принцип кодирования распределения инверсий может быть показан на следующем примере. Пусть на второй дополнительный блок 11 памяти поступает п -разрядное информационное слово, представляющее конкретную комбинацию О и 1. С блока 10 поступают кода состояния сдвиговых регистров. МогуГЙдйвЙтКеа следующие ситуации. Если искажается О { залипание в О), то разряды, содержащие О, нужно инвертировать. И наоборот, если искажается 1, то необходЙЙГоннёёртйроваТь разряды, содержащие 1. ЕсЯй направление скажения (О или 1) совпадает с цифровым значёйиём ра§рйД1а;то § этом случае нельзя инвертировать, и данный разряд записыв&ёТся толЙКо в прямом коде. Распределение инверсий можно, например, кодиро- . вать по аналогии с кодом Хэмминга (при инвертировании каждой группы Хэмминга в. соответствующий райряд записывается 1). В блок 11 записывается полученный код йнвёртйрования по соответствующим аДрёсам, КбторЫё задаются с адресного блока 12. В блоке 7 кодирования информация, поступившая с входного регистра I,кодируется И соответствий с кодами инвертирования, поступающими с блока II,и зйййсыЖётся в соответствующие разряды блока 4. При считывании информации по адресу, который задается с шины 15, адресный блок 12 организует выборку нужного слова из блока 4 и кода инвертирования, соответс- вующего оаняо му слову, из блока 11. Информация аеко дируется в блоке 8 и ерез выходной регистр 2 слово считывается на выхоое 16 Таким образом, предложенное устройство позволяет существенно повысить HajiejKность ЭЦВМ и компоновать накопитель не только из годных, но и частично бракованных матриц, что резко снижает, себестоимость памяти.

Формула изобретения

Запоминающее устройство, содержащее основной блок памяти, первый вход которого соединен с выходом адресного блока, управляющий генератор, выход которого соединен со вторым входом основного блока памяти, входной и выходной регистры, отличающееся тем, что, с целью повышения надежности устройства за счет устранения отказов основного блока памяти, в него введены последовательно соединенные блок тестового контроля, первый блок кодирования и первый дополнительный блок памяти, дешифратор, второй блок кодирования,

второй дополнительный блок памяти и

третий блок кодирования, один из входов которого соединен с выходом входного регистра и одним из входов второго блока koдиpoвaния, другой вход второго блока кодирования подключен к первому выходу второго дополнительного блока памяти, первый вход которого соединен с выходом третьего блока кодирования, другой вход третьего блока кодирования соединен с выходом первого дополнитель,ного блока памяти, выход адресного блока I подключен ко второму входу второго допопнитедьного блока памяти, второй выход : которого соединен с одним из входов дешифратора, другой вход дешифратора соединен с первым выходом основного блока памяти, второй выход которого соединен с другим входом блока тестового контроля, выход дешифратора соединен со входом выходного регистра, выход второго блока кодирования соединен с третьим входом основного блока памяти, четвертый вход которого соединен с другим выходом блока тестового контроля.

Источники информации, принятые во внимание, при экспертизе

№ 410465, кл. Q 11 С 19/00, опублик. 10.04.72 (прототип).

Авторы

Даты

1980-07-05—Публикация

1978-04-17—Подача