Изобретение относится к автоматике и вычислительной технике и может быть использовано для быстрого умножения двоичных чисел с контролем по четности.

Целью изобретения является повышение достоверности результата вычислений устройства.

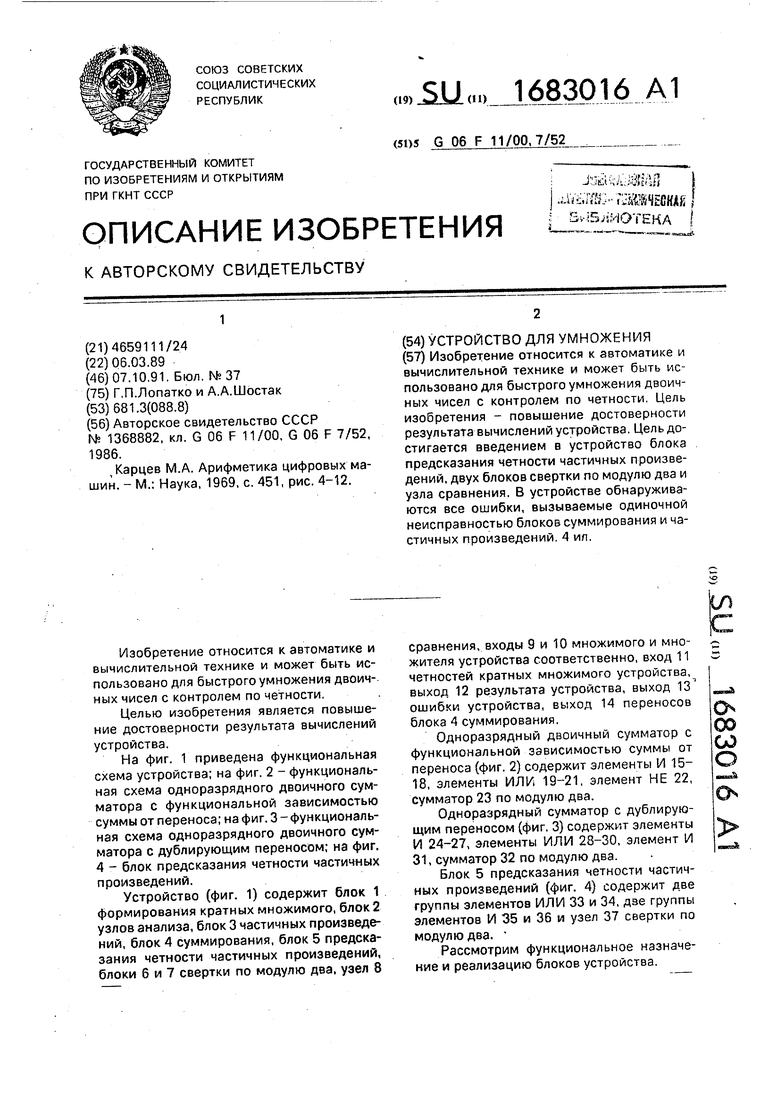

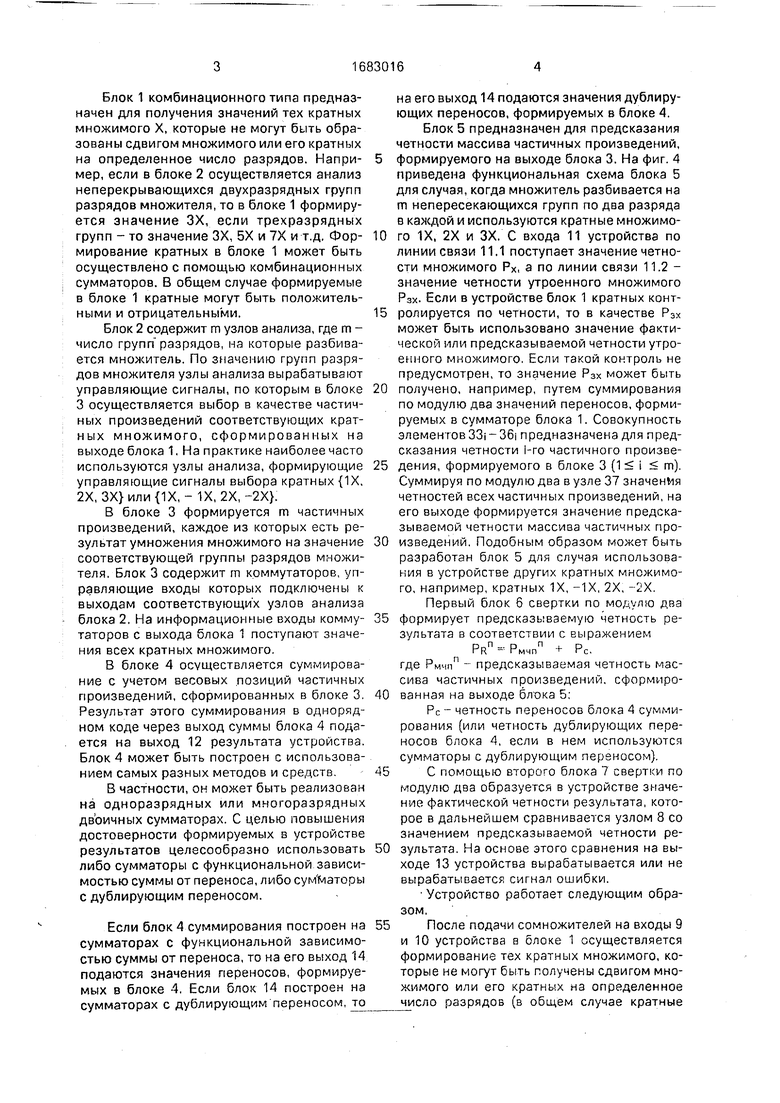

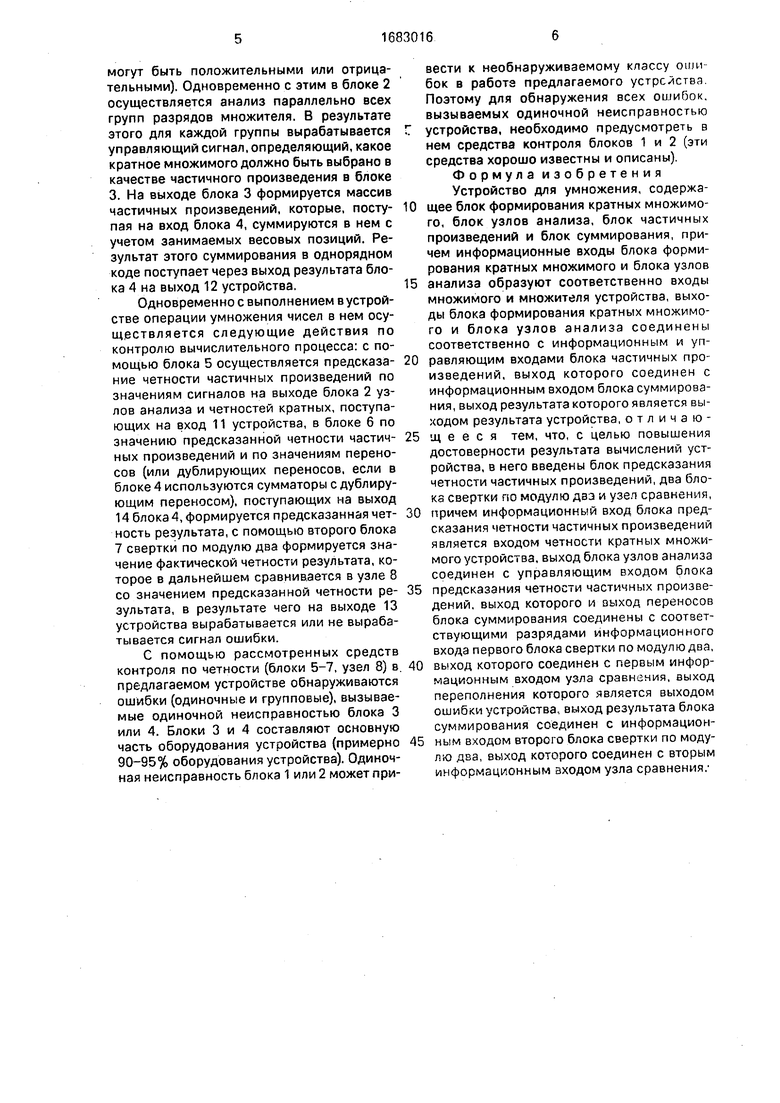

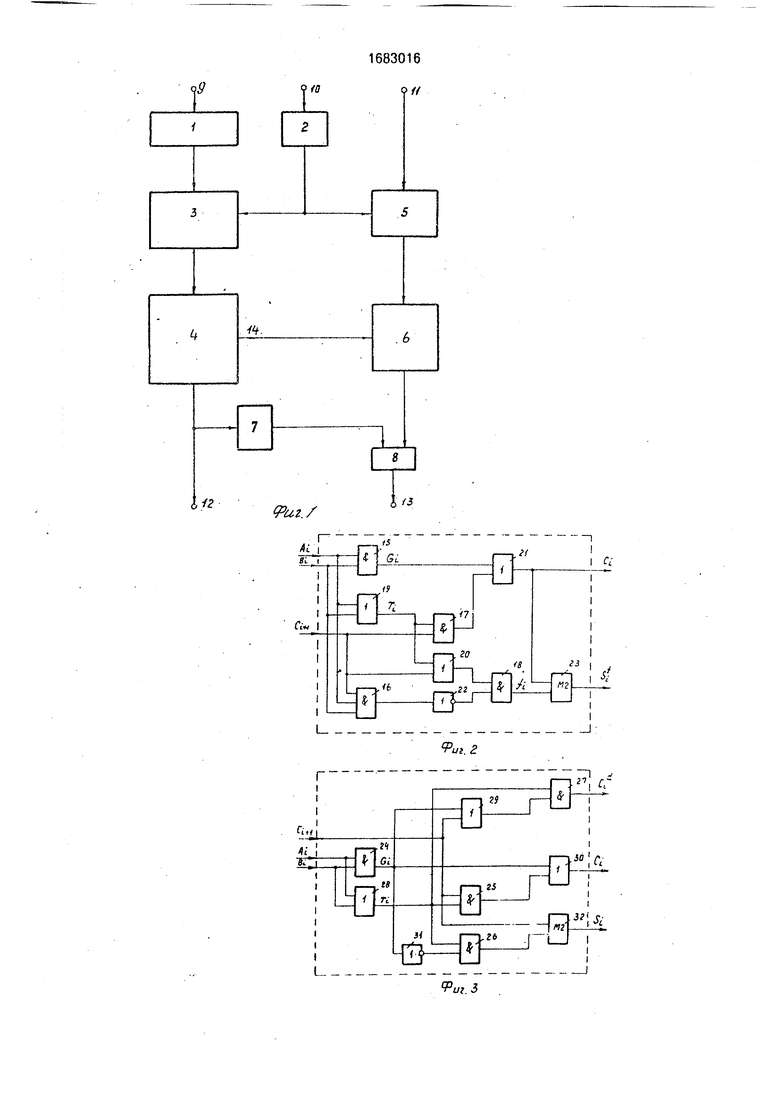

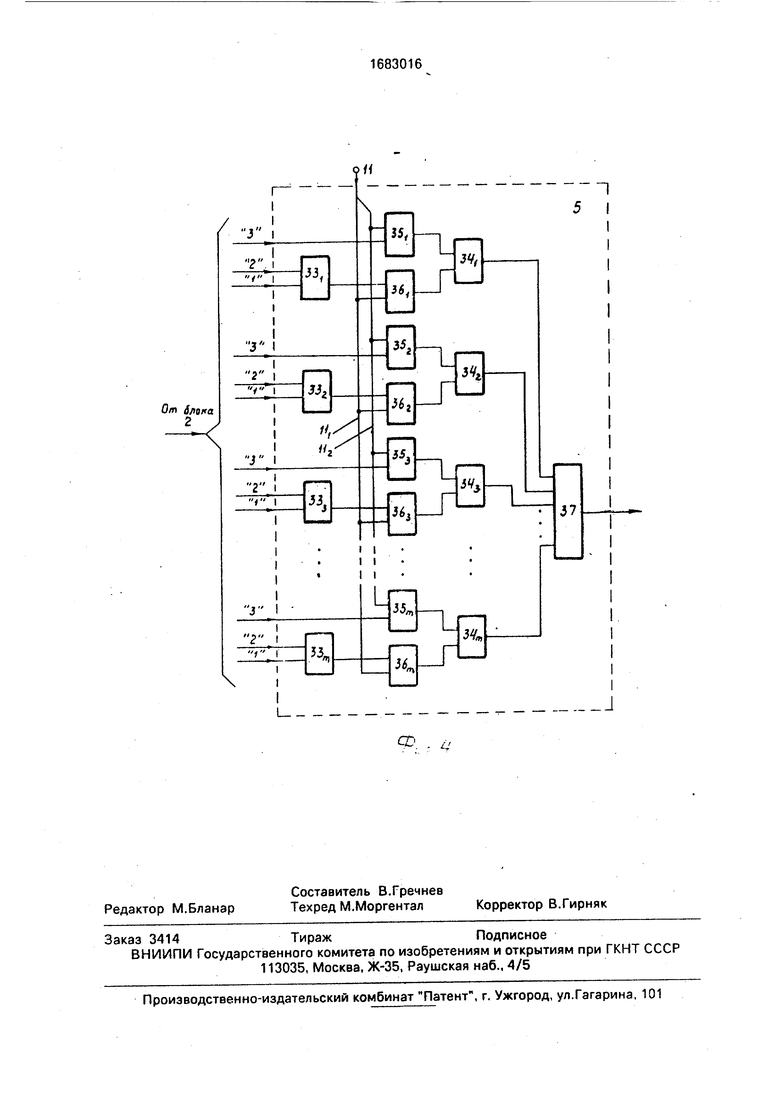

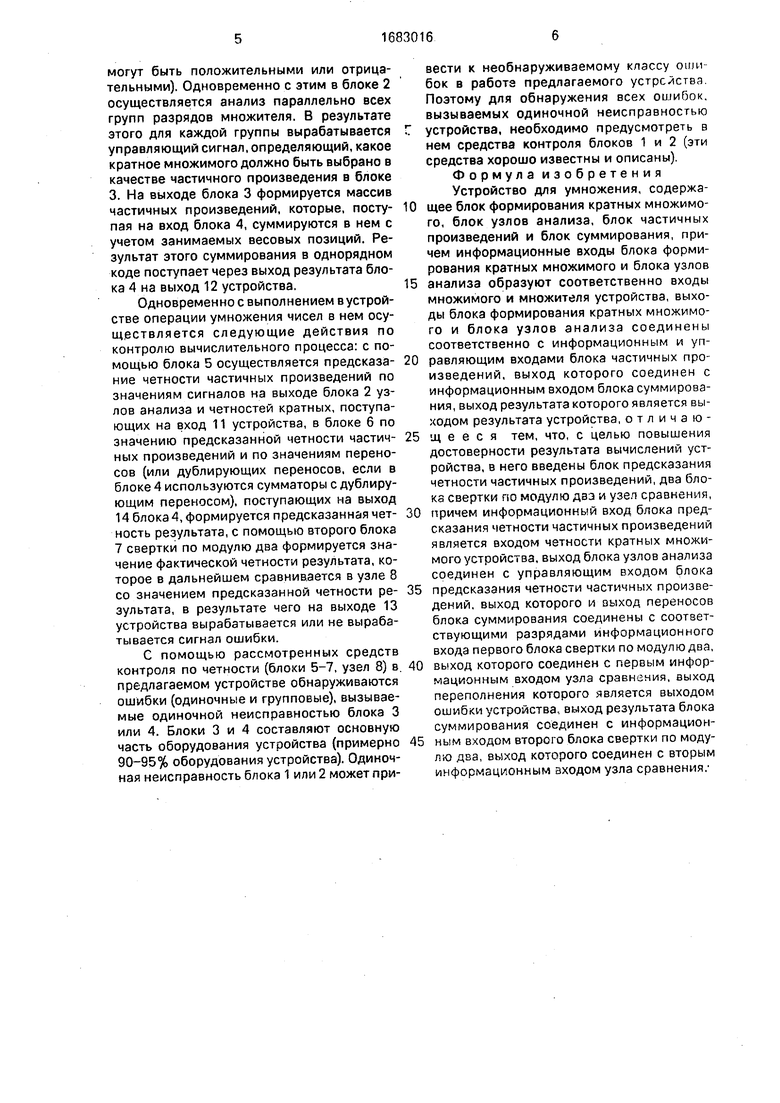

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема одноразрядного двоичного сумматора с функциональной зависимостью суммы от переноса; на фиг. 3 - функциональная схема одноразрядного двоичного сумматора с дублирующим переносом; на фиг. 4 - блок предсказания четности частичных произведений.

Устройство (фиг. 1) содержит блок 1 формирования кратных множимого, блок 2 узлов анализа, блок 3 частичных произведений, блок 4 суммирования, блок 5 предсказания четности частичных произведений, блоки 6 и 7 свертки по модулю два, узел 8

сравнения, входы 9 и 10 множимого и множителя устройства соответственно, вход 11 четностей кратных множимого устройства, выход 12 результата устройства, выход 13 ошибки устройства, выход 14 переносов блока 4 суммирования,

Одноразрядный двоичный сумматор с функциональной зависимостью суммы от переноса (фиг. 2) содержит элементы И 15- 18, элементы ИЛИ, 19-21, элемент НЕ 22, сумматор 23 по модулю два.

Одноразрядный сумматор с дублирующим переносом (фиг. 3) содержит элементы И 24-27, элементы ИЛИ 28-30, элемент И 31, сумматор 32 по модулю два.

Блок 5 предсказания четности частичных произведений (фиг. 4) содержит две группы элементов ИЛИ 33 и 34, две группы элементов И 35 и 36 и узел 37 свертки по модулю два.

Рассмотрим функциональное назначение и реализацию блоков устройства.

О 00 00

о

Блок 1 комбинационного типа предназначен для получения значений тех кратных множимого X, которые не могут быть образованы сдвигом множимого или его кратных на определенное число разрядов. Например, если в блоке 2 осуществляется анализ неперекрывающихся двухразрядных групп разрядов множителя, то в блоке 1 формируется значение ЗХ, если трехразрядных групп - то значение ЗХ, 5Х и 7Х и т.д. Формирование кратных в блоке 1 может быть осуществлено с помощью комбинационных сумматоров. В общем случае формируемые в блоке 1 кратные могут быть положительными и отрицательными.

Блок 2 содержит m узлов анализа, где m - число групп разрядов, на которые разбивается множитель. По значению групп разрядов множителя узлы анализа вырабатывают управляющие сигналы, по которым в блоке 3 осуществляется выбор в качестве частичных произведений соответствующих кратных множимого, сформированных на выходе блока 1, На практике наиболее часто используются узлы анализа, формирующие управляющие сигналы выбора кратных {1Х, 2Х, ЗХ} или {1Х, - 1Х, 2Х, -2Х}.

В блоке 3 формируется m частичных произведений, каждое из которых есть результат умножения множимого на значение соответствующей группы разрядов множителя. Блок 3 содержит m коммутаторов, управляющие входы которых подключены к выходам соответствующих узлов анализа блока 2. На информационные входы коммутаторов с выхода блока 1 поступают значения всех кратных множимого.

В блоке 4 осуществляется суммирование с учетом весовых позиций частичных произведений, сформированных в блоке 3. Результат этого суммирования в однорядном коде через выход суммы блока 4 подается на выход 12 результата устройства. Блок 4 может быть построен с использованием самых разных методов и средств.

В частности, он может быть реализован на одноразрядных или многоразрядных двоичных сумматорах. С целью повышения достоверности формируемых в устройстве результатов целесообразно использовать либо сумматоры с функциональной зависимостью суммы от переноса, либо сум маторы с дублирующим переносом.

Если блок 4 суммирования построен на сумматорах с функциональной зависимостью суммы от переноса, то на его выход 14 подаются значения переносов, формируемых в блоке 4, Если блок 14 построен на сумматорах с дублирующим переносом, тр

на его выход 14 подаются значения дублирующих переносов, формируемых в блоке 4.

Блок 5 предназначен для предсказания четности массива частичных произведений,

формируемого на выходе блока 3. На фиг. 4 приведена функциональная схема блока 5 для случая, когда множитель разбивается на m непересекающихся групп по два разряда в каждой и используются кратные множимо0 го 1Х, 2Х и ЗХ. С входа 11 устройства по линии связи 11.1 поступает значение четности множимого РХ, а по линии связи 11.2 - значение четности утроенного множимого Рзх. Если в устройстве блок 1 кратных конт5 ролируется по четности, то в качестве Рзх может быть использовано значение фактической или предсказываемой четности утроенного множимого. Если такой контроль не предусмотрен, то значение Рзх может быть

0 получено, например, путем суммирования по модулю два значений переносов, формируемых в сумматоре блока 1. Совокупность элементов 33|-36| предназначена для предсказания четности i-ro частичного произве5 дения, формируемого в блоке 3 (1 i m). Суммируя по модулю два в узле 37 значения четностей всех частичных произведений, на его выходе формируется значение предсказываемой четности массива частичных про0 изведений. Подобным образом может быть разработан блок 5 для случая использования в устройстве других кратных множимого, например, кратных 1Х, -1Х, 2Х, -2Х. Первый блок 6 свертки по модулю два

5 формирует предсказываемую четность результата в соответствии с выражением

Ркп - Рмчпп + Рс,

где Рмчпп - предсказываемая четность массива частичных произведений, сформиро0 ванная на выходе блока 5:

Рс - четность переносов блока 4 суммирования (или четность дублирующих переносов блока 4, если в нем используются сумматоры с дублирующим переносом).

5С помощью второго блока 7 свертки по

модулю два образуется в устройстве значение фактической четности результата, которое в дальнейшем сравнивается узлом 8 со значением предсказываемой четности ре0 зультата. На основе этого сравнения на выходе 13 устройства вырабатывается или не вырабатывается сигнал ошибки.

Устройство работает следующим образом,

5 После подачи сомножителей на входы 9 и 10 устройства в блоке 1 осуществляется формирование тех кратных множимого, которые не могут быть получены сдвигом множимого или его кратных на определенное число разрядов (в общем случае кратные

могут быть положительными или отрицательными). Одновременно с этим в блоке 2 осуществляется анализ параллельно всех групп разрядов множителя. В результате этого для каждой группы вырабатывается управляющий сигнал, определяющий, какое кратное множимого должно быть выбрано в качестве частичного произведения в блоке 3. На выходе блока 3 формируется массив частичных произведений, которые, посту- пая на вход блока 4, суммируются в нем с учетом занимаемых весовых позиций. Результат этого суммирования в однорядном коде поступает через выход результата блока 4 на выход 12 устройства,

Одновременно с выполнением в устройстве операции умножения чисел в нем осуществляется следующие действия по контролю вычислительного процесса: с помощью блока 5 осуществляется предсказа- ние четности частичных произведений по значениям сигналов на выходе блока 2 узлов анализа и четностей кратных, поступающих на вход 11 устройства, в блоке 6 по значению предсказанной четности частич- ных произведений и по значениям переносов (или дублирующих переносов, если в блоке 4 используются сумматоры с дублирующим переносом), поступающих на выход 14 блока 4, формируется предсказанная чет- ность результата, с помощью второго блока 7 свертки по модулю два формируется значение фактической четности результата, которое в дальнейшем сравнивается в узле 8 со значением предсказанной четности ре- зультата, в результате чего на выходе 13 устройства вырабатывается или не вырабатывается сигнал ошибки.

С помощью рассмотренных средств контроля по четности (блоки 5-7, узел 8) в предлагаемом устройстве обнаруживаются ошибки (одиночные и групповые), вызываемые одиночной неисправностью блока 3 или 4. Блоки 3 и 4 составляют основную часть оборудования устройства (примерно 90-95% оборудования устройства). Одиночная неисправность блока 1 или 2 может привести к необнаруживаемому классу ошибок в работа предлагаемого устройства. Поэтому для обнаружения всех ошибок, вызываемых одиночной неисправностью устройства, необходимо предусмотреть в нем средства контроля блоков 1 и 2 (эти средства хорошо известны и описаны). Формула изобретения Устройство для умножения, содержащее блок формирования кратных множимого, блок узлов анализа, блок частичных произведений и блок суммирования, причем информационные входы блока формирования кратных множимого и блока узлов анализа образуют соответственно входы множимого и множителя устройства, выходы блока формирования кратных множимого и блока узлов анализа соединены соответственно с информационным и управляющим входами блока частичных произведений, выход которого соединен с информационным входом блока суммирования, выход результата которого является выходом результата устройства, отличающееся тем, что, с целью повышения достоверности результата вычислений устройства, в него введены блок предсказания четности частичных произведений, два блока свертки по модулю двз и узел сравнения, причем информационный вход блока предсказания четности частичных произведений является входом четности кратных множимого устройства, выход блока узлов анализа соединен с управляющим входом блока предсказания четности частичных произведений, выход которого и выход переносов блока суммирования соединены с соответствующими разрядами информационного входа первого блока свертки по модулю два, выход которого соединен с первым информационным входом узла сравнения, выход переполнения которого является выходом ошибки устройства, выход результата блока суммирования соединен с информационным входом второго блока свертки по модулю два, выход которого соединен с вторым информационным входом узла сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения с контролем | 1989 |

|

SU1675879A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Устройство для умножения | 1985 |

|

SU1291975A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для быстрого умножения двоичных чисел с контролем по четности. Цель изобретения - повышение достоверности результата вычислений устройства. Цель достигается введением в устройство блока предсказания четности частичных произведений, двух блоков свертки по модулю два и узла сравнения. В устройстве обнаруживаются все ошибки, вызываемые одиночной неисправностью блоков суммирования и частичных произведений. 4 ия.

1г

Риг./

Ai |

l

Г

/з

21

г.

j

рн

J

C

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , Карцев М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969, с | |||

| ИГРУШКА С ПЛАВАЮЩЕЙ ФИГУРОЙ | 1922 |

|

SU451A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-10-07—Публикация

1989-03-06—Подача