I

Изобретение относится к запоминающим устройствам.

Известно многофункциональное оперативное запоминающее устройство (ОЗУ), оперирующее с информацией, представленной в двоичном коде 1.

Это ОЗУ не может оперировать с информацией, представленной К-ичным, например десятичным, фазо-импульсным кодом.

Наиболее близко к предлагаемому ОЗУ для хранения чисел в системе счисления с основанием, равным К, например десятичных чисел, содержащее в каждом разряде К-ичный, например десятичный, счетчик, элементы И, накопитель из числовых линеек на интегрирующих магнитных сердечниках, адресные, разрядные, управляющие и выходные шины 2.

Однако зто устройство выполняет только функции записи, хранения и Сштывания информации, а его реализация сопровождается значительными аппаратурными затратами.

Цель изобретения - расщирение функционалных возможностей ОЗУ за счет выполнения функций суммирующего счетчика, счетчика с

предустановкой, многодекаш{ого делителя и. десятичного регистра.

Поставленная цель достигается тем, что в устройство введены дополнительный элемент И, элемент НЕ, элементы И-ИЕ и элементы ИЛИ, причем тактирующие входы десятичного счетчика первого разряда первой числовой линейки и десятичных счетчиков одноименных разрядов остальных числовых линеек подключены к выходам соответствующих лпементов И, тактирующие входы остальных десятичных счетчиков соединены с выходом дополнительного элемента И; счетные входы лесят 1чных счетчиков, кроме десятичного счетчика первого разряда первой числовой линейки, подключены к выходам соответствующих элементов И -НЕ, первые входы которых соединены с выходом десятичного счетчика предыдущего разря.ча, причем для первого разряда каждой числовой линейки предыдущим считается последний разряд предыдущей числовой линейки; счетный вход десятичного счетчика первого разряда первой числовой линейки соединен с выходом элемента ПЕ; установочные входы десятичных счетчиков одпоименных разрядов соединены соответственно с разрядными шинами; разрешающие входы десятичных счетчиков каждой числовой линейки подключены к адресным шинам, выходы десятшшых счетчиков соединены со входами соответствующих элементов ИЛИ, выходы которых подключены к выходам устройства; первый вход дополнительного элемента И соединен с выходом одного из элементов И; второй вход дополнительного элемента И, вход элемента НЕ входы элементов И, вторые и третьи входы элементов И-НЕ подключены к соответствующим управляющим шинам; разрешающие входы десятичных счетчиков соединены с адресными шинами.

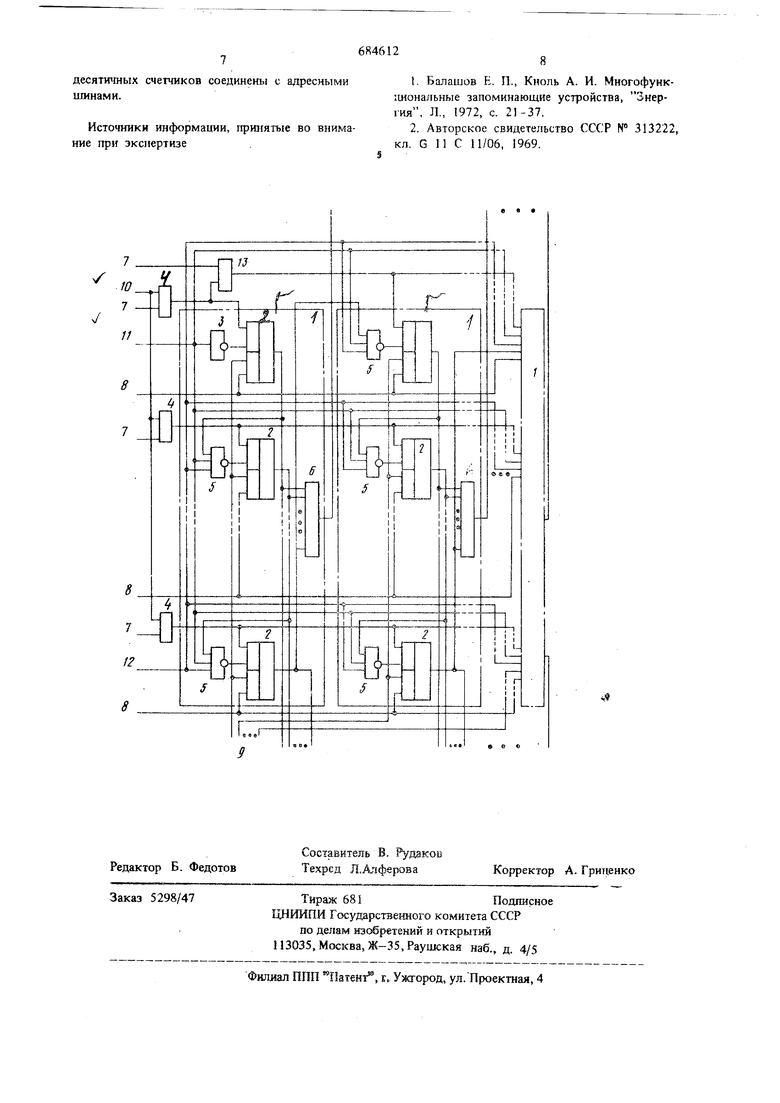

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит m п-разрядных числовых линеек 1 (т - емкость ОЗУ), каждый разряд которых состоит из десятичных счетчиков, например фазо-импульсных декад 2 типа 1 НЕ-551, элемент НЕ 3, п элементов И 4, Tin-l элементов И-НЕ 5, m элементов ИЛИ 6 управляющие шины 7, разрядные шины 8, адресные щнны 9, управляющие шины 10-12, дополнительный элемент И 13. Шины 10-12 служат соответственно для подачи тактовых импульсов, счетных импульсов и импульсов нулевой фазо-импульсной константы. Тактирующие входы декадь 2 первого разряда первой числовой линейки 1 (левая на чертеже) и декад 2 одноименных разрядов остальных числовых линеек 1 подключены к выходам соответствующих элементов И 4. Тактирующие входы остальных декад 2 соединены с выходом элемента И 13. Счетные входы декад 2, кроме декады 2 первого разряда первой числовой линейки 1, подключены к выходам элементов И-НЕ 5, первые входы которых соединены с выходо декады 2 предыдущего разряда, причем для первого разряда каждой числовой линейки предыдущим считается последний разряд предыдущей числовой линейки.

Счетный вход декады первого разряда первой числовой линейки 1 соединен с выходом элемента, НЕ 3. Установочные входы декад 2 одноименных разрядов соедин1;кы соответственно с разрядными щинами 8. Разрешающие входы декад 2 каждой числовой линейки 1 подключены к адресным шинам 9. Выходы декад соединены со входами элементов ИЛИ 6, входы которых подключены к выходам устройства. Второй вход элемента И 13 соединен с одной из шин 7, остальные шины 7 подключены к одним из входов элементов И 4, щзугие входы которых соединены с шиной 10. Вход элемента НЕ 3 и вторые входы элементов

И-НЕ 5 подключены к шине 11, а третьи входы элементов И-НЕ 5 соединены с шиной 12.

Работу описываемого устройства рассмотрим для случая прямого кодирования числовой информации.

В режиме работы предлагаемого устройства как оперативного запоминающего устройства в течение одного опорного периода возможна запись только одного многоразрядного числа. При этом по соответствующей адресной шине 9 на разрешающие входы декад 2 выбранной числовой линейки 1 в течение периода следования импульсов опорной последовательности подается управляющий потендаал, а на установочные входы этих же декад по разрядным шинам 8 поступают импульсы записи, переключающие декады числовой линейки в нулевое состояние.

В результате этого фазы выходных импульсов декад 2 в последующих опорных периодах совпадают с фазоимпульсными константами, при которых проиэощла установка декад в нуль. Другое число записывается в другую числовую линейку аналогично вышеописанному в отдельном опорном периоде. При записи и хранеНИН информации в ОЗУ на всех шинах 7 присутствуют сигналы, открывающие элемент И 13 н элементы И 4. В этом случае по шине 10 тактовые импульсы поступают на тактирующие входы всех декад устройства. Считывание информащ1и с ОЗУ производится для всех чисел. При этом в первом опорном периоде считывающей сигнал присутствует на щине 7 элемента И 4, соединенного выходом с тактирующим входом декады 2 первого разряда первой числовой линейки 1, и на шине 7 элемента И 13. Во втором опорном периоде считывающий сигнал подается только на шину 7 элемента И 4, выход которого подключен к тактирующим входам декад вторых разрядов всех чисел. Аналогичным образом считывается информация с последующих разрядов числовых линеек. При этом в каждом опорном периоде на выходах ОЗУ оказываются сигналы, отображающие Щ1фровые значения только одноименных разрядов всех чисел.

При работе предложенного устройства в режимах суммирующего счетчика, счетчика с предустановкой и десятичного фазо-импульсного регистра злементы И 4 и И 13 посредством сигналов по шинам 7 устанавливаются в открытое состояние, и тактовые импульсы поступают на тактирующие входы всех декад 2. Декада 2 первого разряда первой числовой линейки 1 является первым разрядом этих схем, а их разрядность определяется количеством декад 2 в устройстве. При работе устройства в режиме суммирую щего счетчика в течение опорного периода по шине 11 может поступить только один счетный импульс. Ввиду того, что в фазо-импульсной декаде типа 1 ИЕ-551 тактовые и счетнь:е импульсы имеют отрицательную полярность от носительно уровня напряжения питания, кажды счетный импульс, инвертируясь элементом НЕ 3, не пропускает на декаду 2 тактовый импульс, совпадающий во времени со счетным импульсом. В этом случае сигнал на выход декада.1 2 появляется с задержкой на один Период тактовых импульсов, что соответствует изменению состояния декады на единицу в сторону больших чисел. Аналогичным образом происходит прибавление единицы переноса в следующем разряде, где запрещающий сигнал поступает на счет ный вход декады в момент совпадения на входах элемента И-НЕ 5, соединенного выходом с этим счетным входом, счетного импуль са, сигнала переноса с предыдущего разряда и сигнала нулевой фазо-импульсной константы. Состояние счетчика определяется в. течени отдельного опорного периода фазовыми значениями сигналов на выходах устройства. При выполнении устройством функции счет чика с предустановкой численное значение каж дого его разряда устанавливается в отдельном опорном периоде с помощью установочного сигнала и разрешающего потенциала, посуупаю щих по выбранным разрядной шине 8 и адресной шине 9. Дальнейшая работа счетчика с предустановкой аналогична работе счетчика с прямым счетом. При работе устройства в режиме десятичного фаэо-импульсного регистра памяти чисneiffloe знание каждого его разряда устанавливается так же, как и в счетчике с предустановкой, а информация с регистра может бы считана в течение одного опорного периода. При работе устройства в режиме многодекадного делителя сигнал присутствует только на управляющей шине 7 элемента И 4, подключенного к тактирующему входу декады 2 первого разряда первой числовой линейки 1. На счетный вход этой декады через элемент НЕ 3 по шине 11 в каждом опорном периоде поступает один счетный импульс. В соответствующие моменты времени на выходах декад, начиная со второго, появляются импул сы, следующие с частотой f/10, f/10, , f/10, где f - частота следования входных им пульсов. Реализация описанного устройства сопряжена с меньшими аппаратурными затратами, чем peaj H3amw прототипа. Этим обусловлена н бопее высокая его надежность. Кроме того, прототип нельзя реализовать методами интегральной технологии, так как оно содержит реактивные элементы. Таким образом, описашюе устройство более экономично, обладает многофункциональностью и может быть реализовано в потенциальной системе элементов. Формула изобретения Оперативное запоминающее устройство, содержащее числовые линейки, каждый разряд которых состоит из десятичных счетчиков, элементы И, адресные, разрядные, управляющие и выходные шины, отличающееся тем, что, с целью его упрощения и расширения, функциональных возможностей за счет выполнения функций сумм1фующего счетчика, счетчика с предустановкой, многодекадного делителя и десятичного регистра, в него введст ы дополнительный элемент И, элемент НЕ, элементы И-НЕ и элементы ИЛИ, причем тактирующие входы десятичного счетчика первого разряда первой числовой линейки и десятичных счетчиков одноименных разрядов остальных числовых линеек подключены к выходам соответствующих элементов И, тактирующие входы остальных десяти шых счетчиков соединены с выходом дополнительного элемента И, счетные входы десятичных счетчиков, кроме десятичного счетчика первого разряда первой числовой линейки, подключены к выходам соответствующих элементов И-НЕ, первьге входы которых соединены с выходом десятичного счетчика предыдущего разряда, причем для первого разряда каждой числовой линеГжи предыдущим считается последний разряд предыдущей числовой линейки, счетный вход десятичного счетчика первого разряда первой числовой линейки соединен с выходом элемента НЕ, установочные входы десятичных счегщков одноименных разрядов соединены соответственно с разрядными шинами, разрешающие входы десятичных счетчиков каждой числовой линейки подключены к адресным шинам, .ходы десятичных счетчиков соедШ1ены со входами соответствующее элементов ИЛИ, В1.ходы которых подключены к выходам устройства, асрвый вход дополнительного элемента И соединен с выходом одного из элементов И, в горой вход дополнительного элемента И, вход элемента НЕ, вхошя элементов И, вторые и третьи входы элементов И-НЕ подключены к соответствующим управляющим щинам, разрешающие входы

десятшшых счегчиков соединены с адресными ишнами.

Источники информации, пршсятые во внимание при экснертизе

1.Балашов Е. П., Кноль А. И. Многофункциональные запоминающие устройства, Энергия, Л., 1972, с. 21-37.

2.Авторское свидетельство СССР № 313222, кл. G 11 С 11/06. 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Устройство для измерения глубины скважины | 1981 |

|

SU1008433A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| ФОРМИРОВАТЕЛЬ ПЕРИОДИЧЕСКИХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2003 |

|

RU2271602C2 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

Авторы

Даты

1979-09-05—Публикация

1977-02-25—Подача