1

Изобретение относится к технике связи и может использоваться для определения коэффициента ошибок в дискретных каналах и каналах передачи данных.

Известен датчик тестовой псевдослучайной последовательности, содержащий генератор тактовых импульсов и регистр сдвига с сумматором по модулю два в цепи обратной связи 1.

Однако в известном датчике невозможно получить выходной сигнал с заданной реализацией потока случайных краевых искажений, что ограничивает функциональные возможности датчика.

Целью изобретения является формирование выходного сигнала с заданными случайными краевыми искажения.ми.

Для этого в датчик тестовой псевдослучайной последовательности, содержащий генератор тактовых импульсов и регистр сдвига с сумматором по модулю два в цепи обратной связи, введен блок переменной задержки, при этом выход генератора тактовых импульсов подключен к одному из входов блока переменной задержки, к двум другим входам которого подключены выходы

соответствующих разрядов регистра сдвига, а выход блока переменной задержки подключен к тактовому входу регистра сдвига. Б,лок переменной задержки выполнен в виде последовательно соединенных задающего генератора, счетчика и триггера, к другому входу которого подключен один из входов ключевого боТока, выходы которого подключены к установочным входам счетчика, причем входы ключевого лока являются входами, а выход триггера - выходом блока переменной задержки.

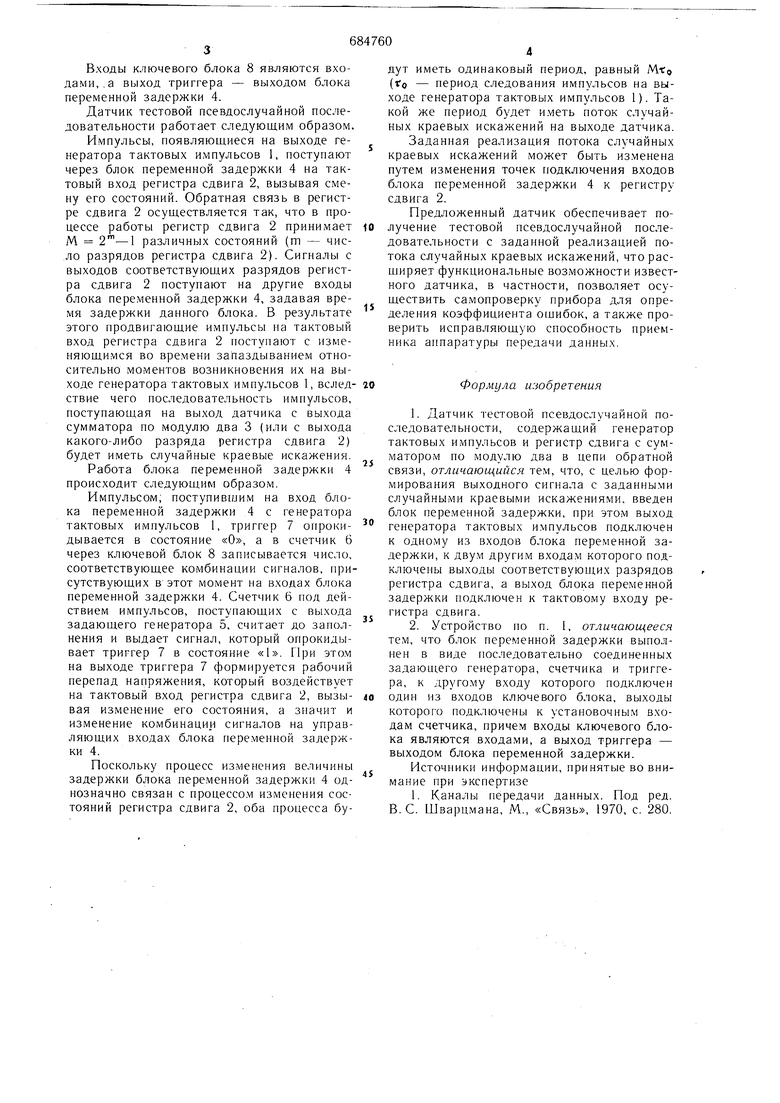

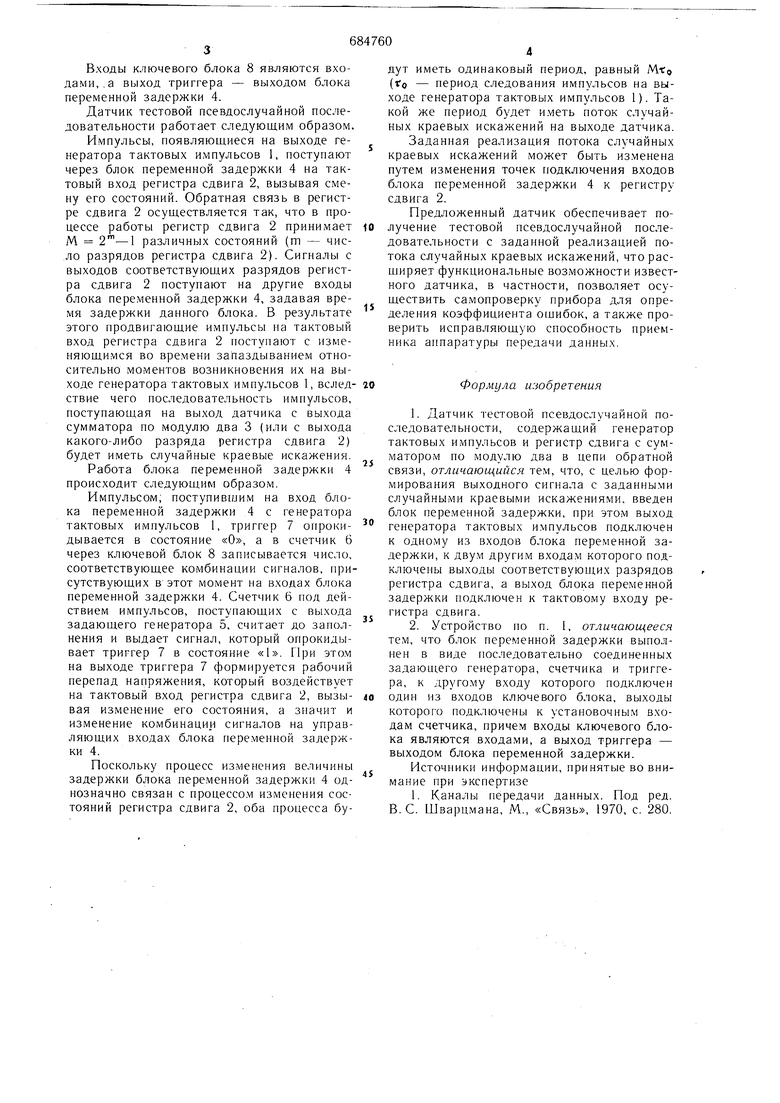

На чертеже приведена структурная электрическая схема предложенного датчика.

Датчик тестовой псевдослучайной последовательности содержит генератар тактовых импульсов 1, регистр сдвига 2 с сум.матором по модулю два 3 в цепи обратной связи и блок переменной задержки 4.

Блок переменной задержки 4 выполнен в виде последовательно соединенных задающего генератора 5, счетчика 6 и триггера 7, к другому входу которого подключен один из входов ключевого блока 8, выходы которого подключены к установочным входам счетчика 6. Входы ключевого блока 8 являются входами,.а выход триггера - выходом блока переменной задержки 4. Датчик тестовой псевдослучайной последовательности работает следующим образом. Импульсы, появляющиеся на выходе генератора тактовых импульсов 1, поступают через блок переменной задержки 4 на тактовый вход регистра сдвига 2, вызывая смену его состояний. Обратная связь в регистре сдвига 2 осуществляется так, что в процессе работы регистр сдвига 2 принимает М различных состояний (т - число разрядов регистра сдвига 2). Сигналы с выходов соответствующих разрядов регистра сдвига 2 поступают на другие входы блока переменной задержки 4, задавая время задержки данного блока. В результате этого продвигающие импульсы на тактовый вход регистра сдвига 2 поступают с изменяющимся во времени запаздыванием относительно моментов возникновения их на выходе генератора тактовых импульсов 1, вследствие чего последовательность импульсов, поступающая на выход датчика с выхода сумматора по модулю два 3 (или с выхода какого-либо разряда регистра сдвига 2) будет иметь случайные краевые искажения. Работа блока переменной задержки 4 происходит следующим образом. Импульсом, поступившим на вход блока переменной задержки 4 с генератора тактовых импульсов 1, триггер 7 онрокидывается в состояние «О, а в счетчик 6 через ключевой блок 8 записывается число, соответствующее комбинации сигналов, присутствующих в этот момент на входах блока переменной задержки 4. Счетчик 6 под действием импульсов, поступающих с выхода задающего генератора 5, считает до заполнения и выдает сигнал, который опрокидывает триггер 7 в состояние «1. При этом на выходе триггера 7 формируется рабочий перепад напряжения, который воздействует на тактовый вход регистра сдвига 2, вызывая изменение его состояния, а значит и изменение комбинации сигналов на управляющих входах блока иере.мениой задержки 4. Поскольку процесс изменения величины задержки блока переменной задержки 4 однозначно связан с процессом изменения состояний регистра сдвига 2, оба процесса будут иметь одинаковый период, равный Mto (to - период следования импульсов на выходе генератора тактовых импульсов 1). Такой же период будет и.меть поток случайных краевых искажений на выходе датчика. Заданная реализация потока случайных краевых искажений может быть из.менена путем изменения точек подключения входов блока пере.менной задержки 4 к регистру сдвига 2. Предложенный датчик обеспечивает получение тестовой псевдослучайной последовательности с заданной реализацией потока случайных краевых искажений, что расширяет функциональные возможности известного датчика, в частности, позволяет осуществить самопроверку прибора для определения коэффициента ошибок, а также проверить исправляющую способность приемника аппаратуры передачи данных. Формула изобретения 1.Датчик тестовой псевдослучайной последовательности, содержащий генератор тактовых импульсов и регистр сдвига с сумматором по модулю два в цепи обратной связи, отличающийся тем, что, с целью формирования выходного сигнала с заданны.ми случайными краевыми искажениями, введен блок переменной задержки, при этом выход генератора тактовых импульсов подключен к одному из входов блока переменной задержки, к двум другим входам которого подключеиы выходы соответствующих разрядов регистра сдвига, а выход блока переменной задержки подключен к тактовому входу регистра сдвига. 2.Устройство по п. 1, отличающееся тем, что блок переменной задержки выполнен в виде последовательно соединенных задающего генератора, счетчика и триггера, к другому входу которого подключен один из входов ключевого блока, выходы которого подключены к установочным входам счетчика, причем входы ключевого блока являются входами, а выход триггера - выходом блока переменной задержки. Источники информации, принятые во внимание при экспертизе 1. Каналы передачи данных. Под ред. B.C. Шварцмана, М., «Связь, 1970, с. 280.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство контроля группы цифровых блоков | 1990 |

|

SU1798786A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2163027C2 |

| Генератор псевдослучайных кодов | 1980 |

|

SU951301A1 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| АУДИОМЕТР | 2022 |

|

RU2791159C1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

Авторы

Даты

1979-09-05—Публикация

1977-12-16—Подача