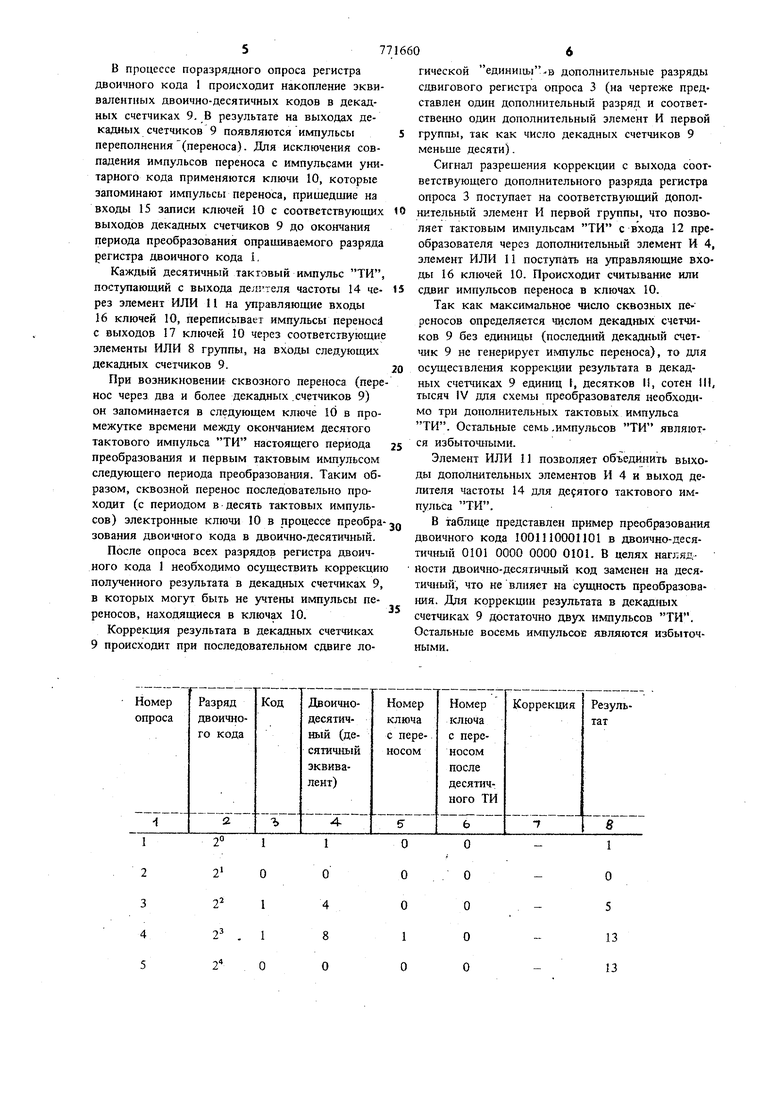

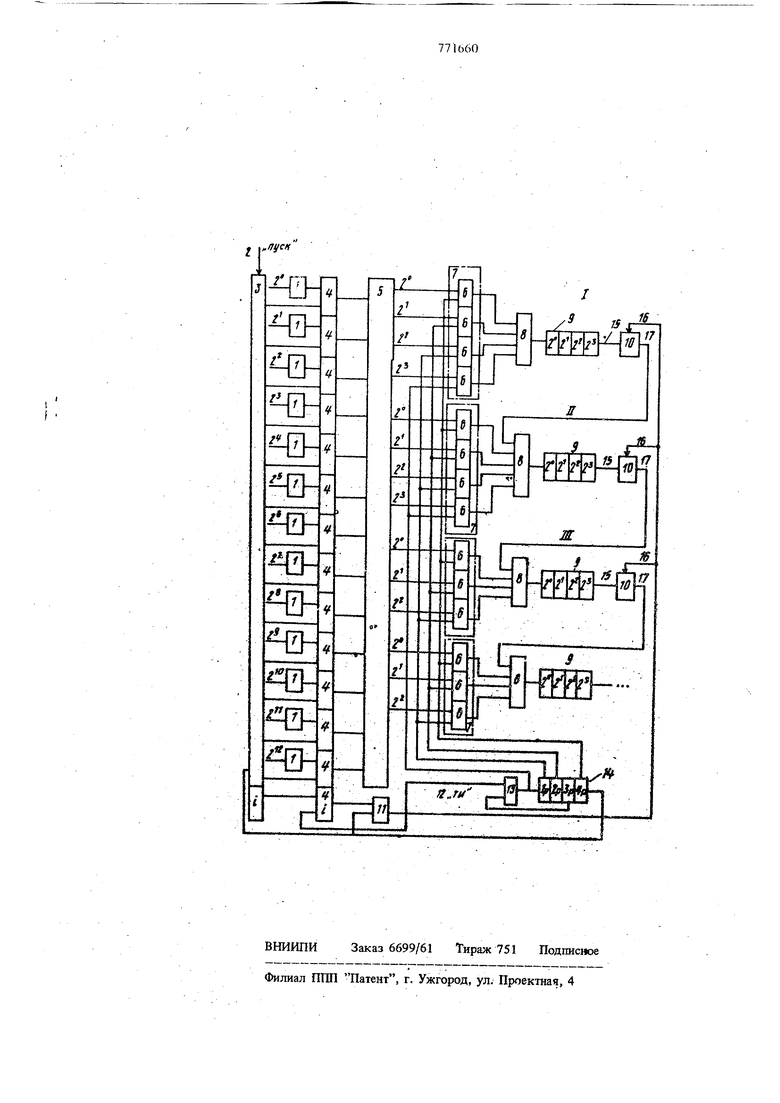

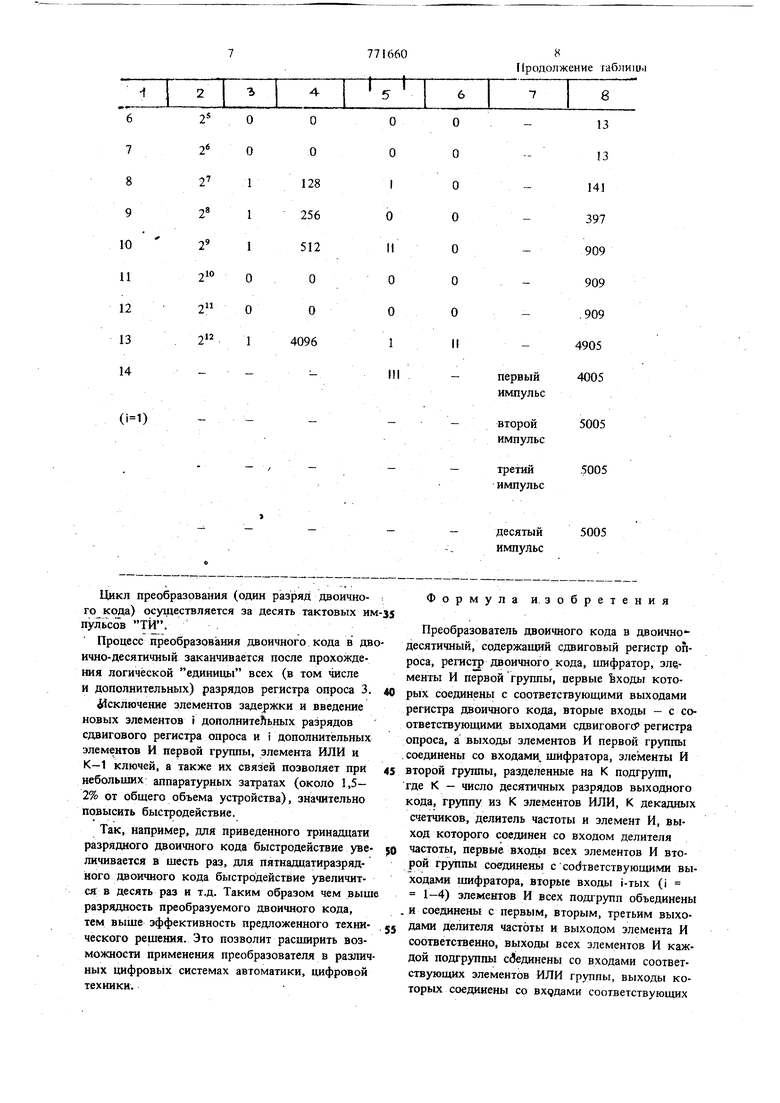

Изобретение относится к области автоматики ицифровой вычислительной техники и может быть использовано при построении двоично-десятичны с преобразователей. Известен преобразователь двоичного кода в десятичный 1, содержащий сдвиговый регистр опроса, регистр двоичного кода, элементы ИЛИ перевода весовых значений разрядов двоичного кода, элементы ИЛИ разрешения формирования десятичных разрядов, ключи, дополнительные регистры сдвига, делитель частоты, декадные счетчики, элементы задержки. Недостаток этого преобразователя состоит в сложности устройства и низком быстродействии Наиболее близким по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятичный код 2, содержащий сдвиговый регистр опроса, регистр двоичного кода, шифратор, элементы И первой группы, первые входы которых соединены с соответствующими выходами регистра двоичного кода, вторые входы - с соответствующими выходами сдвигового регистра опроса, а выходы элементов И первой группы соединены со входами шифратора, элементы И второй группы, разделенные на К подгрупп, где К - число десятичных разрядов выходного кода, группу из К элементов ИЛИ, К декадных счетчиков, делитель частоты и элемент И, выход которого соединен со входом делителя частоты, первые входы всех элементов И второй группы соединены с соответствующими выходами шифратора, вторые входы i-Tbix (i 1-4) элементов И всех подгрупп объединены и соединены с первым, вторым, третьим выходами делителя частоты и выходом элемента И соответственно, .входы всех элементов И каждой подгруппы соединены со входами соответствующих элементов ИЛИ в группе элементов ИЛИ, выходы которых соединены со входами, соответствующих декадных счетчиков, первый вход элемента И соединен с четвертым входом делителя частоты, а второй вход - с тактовым входом преобразователя, йыход переполнения делителя частоты соединен со входом сдвигового регистра опроса. Кроме того, преобразователь содержит группу элементов задержки. 377 Недостаток этого преобразователя состоит в низком быстродействии, связанном с необходимостью задержки работы декадных счетчиков старших десятичных на время формирования переноса декадных счетчиков младших разрядов. Целью изобретения является повышение быстродействия преобразователя двоичного кода в двоично-десятичный. Для достижения поставленной цели в преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр опроса, регистр двоичного кода, шифратор,: элементы И первой группы, первые входы которых соединены с соответствующими выходами регистра двоичного кода, вторые входы - с соответствующими выходами сдвигового регистра опроса, а выходы элементов И первой группы соединены с входами шифратора, элементы И второй группы, разделенные на К подгрупп, где К - число десятичных разрядов .выходного кода, группу из К элементов ИЛИ, К декадных счетчиков, делитель частоты и элемент И, выход которого соединен со входом делителя частоты, первые входы всех элементов И второй группы соединены с соответствующими выходами шифратора, вторые входы i-тых (i 1-4) элементов И всех подгрупп объединены и соединены с первым, вторым, третьим выходами делителя частоты и выходом элемента И соответственно, выходы всех элементов И каждой подгруппы соединены со входами соответствующих элементов ИЛИ в группе элементов ИЛИ, выходы которых соерянены со входами соответствующих декадных;счетчиков, первый вход элемента И соединен с четвертым выходом де. лителя частоты, а второй вход с тактовым входом преобразователя, выход переполнения делителя Частоты соединен со входом сдвигового регистра опроса, введены дополнительные разряды сдвигового регистра опроса, дополнительHi e э.г1ементы И в первой группе, элемент ИЛИ и (К-1) ключей, первый входы которых соединены с выходом элемента ИЛИ, второй вход j-ro ключа tj 1 --(К-1) соединен с выходом j-ro декадного счетчика, а выход j-ro ключа соединен со входом (j + )-го элемента ИЛИ группы, выходы дополнительных разрядов сдвигового регистра опроса соединены с первыми входами соответствующих дополнительных элементов И первой группы, вторые входы которы соединены с тактовым входом преобразователя, а выходы дополнительных элементов И первой группы соединены со входами элемента ИЛИ, вь1Ход переполие1шя делителя частоты соединен со входом элемента ИЛИ. На чертеже представлена блок-схема преобразователя двоичного кода в двоично-десятичный. Преобразователь содержит регистр двоичного кода 1, вход для сигнала Пуск 2, сдвиговый регистр опроса 3, элементы И первой Ipyniibi 4, шифратор 5, элементы И второй группь: 6, подгруппы 7 элементов И второй группы, элементы ИЛИ 8 группы, декадные счетчики 9, ключи 10, элемент ИЛИ 11, тактовый вход преобразователя 12, элемент И 13, делитель частоты 14, входы записи 15 ключей 10, управляющие .входы 16 ключей 10, выходы 1 ключей 10. В преобразователь исходный двоичный код заносится в регистр двоичного кода 1. Преобразователь двоичного кода в двоичнодесятичный начинается с приходом импульсного сигнала Пуск на вход 2 преобразователя, по которому в сдвиговый регистр опроса 3 записывается логическая единида. Далее эта.единида сдвигается каждыми десятыми тактовыми им- , пульсами ТИ, приходящими с выхода делите-. ля частоты 14 на вход сдвига сдвигового регистра опроса 3. Сдвиговый регистр опроса 3 последовательно, с периодом в десять тактовых импульсов ТИ, опрашивает каждый разряд регистра двоичного кода 1 через соответствующие элементы И первой группы 4, выходы которых соединень со входами шифратора 5, построенного из элементов ИЛИ таким образом, что на его выходах появляется эквивалентный опрашиваемому разряду двоичного кода двоично-десятичньш код. Двоично-десятичный код с выходов пшфратора 5 поступает потетрадно (2°, 2, 2, 2) на первые входы элементов И 6 второй группы, выходы которых в соответствии с десятичным весом тетрад О, 1, 2, 3... объединены элементами ИЛИ 8 группы. На вторые входы элементов И 6, за период в десять тактовых импульсов ТИ, соответственно с выхода элемента И 13, первого, второго, и четвертого разрядов делителя частоты 14 поступают серии импульсов 8-4-2-1. Таким образом, элементы И 6 второй группы совместно с элементом И 13 и делителем частоты 14 позволяют осуществить преобразование потенциального двоично-десятичного кода на выходах щифратора 5 в унитарный (числоимпульсный) код, который с выходов элементов И 6 поступает через соответствующие элементы ИЛИ 8 на входы декадных счетчиков 9 единиц I, десятков II, сотен III, тысяч IV и т.д. Так, двоично-десятичный код 0000 0101 0001 0010 за цикл преобразования преобразуется через элементы И 6 группы в серии импульсов 0000 0401 0001 0020, которые объединяются элементами ИЛИ 8 второй группы для соответствующих тетрад и с выхода последних поступают на вход декадных счетчиков 9 соответственно единиц I два импульса, десятков II один импульс, сотен III пять импульсов, тысяч IV ноль импульсов и т.д. . В процессе поразрядного спроса регистра двоичного кода 1 происходит накопление эквивалентных двоично-десятичных кодов в декадных счетчиках 9. В результате на выходах декада«ых счетчиков 9 появляются импульсы переполнения (переноса). Для исключения совпадения импульсов переноса с импульсами унитарного кода применяются ключи 10, которые запоминают импульсы переноса, пришедшие на входы 15 записи ключей 10 с соответствующих выходов декадных счетчиков 9 до окончания периода преобразования опрашиваемого разряда регистра двоичного кода i. Каждый десятичный тактовый импульс ТИ, поступающий с выхода дел теля частоты 14 через элемент ИЛИ 11 на управляющие входы 16 ключей 10, переписывает импульсы переноси с выходов 17 ключей 10 через соответствующие элементы ИЛИ 8 группы, на входы следующих декадных счетчиков 9. При возникновение сквозного переноса (пере нос через два и более декадных .счетчиков 9) он запоминается в следующем ключе Ш в промежутке времени между окончанием десятого тактового импульса ТИ настоящего периода преобразования и первым тактовым и fflyльcoм следующего периода преобразования. Таким образом, сквозной перенос последовательно проходит (с периодом в десять тактовых импульсов) электронные ключи 10 в процессе преобра зования двоишого кода в двоично-десятичный. После опроса всех разрядов регистра двоичного кода 1 необходимо осуществить коррекцию полученного результата в декадных счетчиках 9, в которых могут быть не учтены импульсы пе реносов, находящиеся в ключах 10. Коррекция результата в декадных счетчиках 9 происходит при последовательном сдвиге логической единицы в дополнительные разряды сдвигового регистра опроса 3 (на чертеже представлен один дополнительный разряд и соответственно один дополнительный элемент И первой группы, так как число декадных счетчиков 9 меньще десяти). Сигнал разрешения коррекции с выхода соответствующего дополнительного разряда регистра опроса 3 поступает на соответств)ющий дополнительный элемент И первой группы, что позволяет тактовым импульсам ТИ с входа 12 преобразователя через дополнительный элемент И 4, элемент ИЛИ 11 поступать на зшравляющие входы 16 ключей 10. Происходит считывание или сдвиг импульсов переноса в ключах 10. Так как максимальное число сквозных переносов определяется числом декадных счетчиков 9 без единицы (последний декадный счетшк 9 не генерирует импульс переноса), то для осуществления коррекщш результата в декадных счетчиках 9 едишщ I, десятков И, сотен 111, тысяч IV для схемы преобразователя необходимо три дополнительных тактовых импульса ТИ. Остальные семь .импульсов ТИ являются избыточными. Элемент ИЛИ 11 позволяет объединить выходы дополнительных элементов И 4 к выход делителя частоты 14 для девятого тактового импульса ТИ. В таблице представлен пример преобразования двоичного кода 1001110001101 в двоично-десятичный 0101 0000 0000 0101. В целях наглядности двоично-десятичный код заменен на десятичньш, что не влияет на сущность преобразования. Для коррекщп результата в декадт1х счетчиках 9 достаточно двух импульсов ТИ. Остальные восемь импульсов являются избыточными. Цикл преобразования (один разряд двоичного кода) осуществляется за десять тактовых им пульсов Т№.. Процесс преобразования двоичного кода в дво ично-десятичный заканчивается после прохождения логической единицы всех (в том числе и дополнительных) разрядов регистра опроса 3. ЛДсключение элементов задержки и введение новых элементов i дополнительных разрядов сдвигового регистра опроса и дополнительных элементов И первой группы, элемента ИЛИ и К-1 ключей, а также их связей позволяет при небольших аппаратурных затратах (около 1,5- 2% от общего объема устройства), значительно повысить быстродействие. Так, например, для приведенного тринадцати разрядного двоичного кода быстродействие увеличивается в шесть раз, для пятнадцатиразрядного двоичного кода быстродействие увеличится в десять раз и т.д. Таким образом чем выш разрядность преобразуемого двоичного кода, тем выше эффективность предложенного технического решения. Это позволит расширить возможности применения преобразователя в различ ных цифровых системах автоматики, цифровой техники. Формула и. зобретения Преобразователь двоичного кода в двоичнодесятичный, содержащий сдвиговый регистр опроса, регистр двоичного кода, шифратор, элементы И первой группы, первые Ьходы которых соединены с соответствующими выходами регистра двоичного кода, вторые входы - с соответствующими выходами сдвиговогсР регистра опроса, а выходы элементов И первой группы соединены со входами, шифратора, элементы И второй группы, разделенные на К подгрупп, где К - число десятичных разрядов выходного кода, группу из К элементов ИЛИ, К декадных счетчиков, делитель частоты и элемент И, выход которого соединен со входом делителя частоты, первые входь всех элементов И второй группы соединены с содтветствующими выходами шифратора, вторые входы i-тых (i 1-4) элементов И всех подгрупп объединены и соединены с первым, вторым, третьим выходами делителя частоты и выходом элемента И соответственно, выходы всех элементов И каждой подгруппы соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами соответствующих

декадных счетчиков, первый вход элемента И соединен с четвертым выходом делителя частоты, а второй вход с тактовым входом преобразователя, выход переполнения делителя частоты соединен со входом сдвигового регистpa опроса, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительные разряды сдвигового регистра опроса, дополнительные элементы И в первой группе, элемент ИЛИ и (К-1) ключей, первые входы которых соединены с выходом элемента ИЛИ, второй вход j-ro ключа j 1-(К-1) соединен с выходом j-ro декадного счетчика, а выход j-ro ключа, соединен со входом (J + 1)-го элемента ИЛИ группы, выходы дополнительных разрядов сдвигового регистра опроса соединены с первыми входами соответствующих дополнительных элементов И первой группы, вторые входы которых соединены с тактовым входом преобразователя, а выходы дополнительных элементов И первой группы соединены со входами элемента ИЛИ, выход переполнения делителя частоты соединен со входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство 1 СССР N 432486, кл. G 06 F 5/00, 1974.

2.Авторское свидетельство СССР по заявке N 2339428/18-24, кл. G 06 F 5/02, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ | 1971 |

|

SU432486A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в десятичный | 1976 |

|

SU691842A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

Авторы

Даты

1980-10-15—Публикация

1978-10-09—Подача