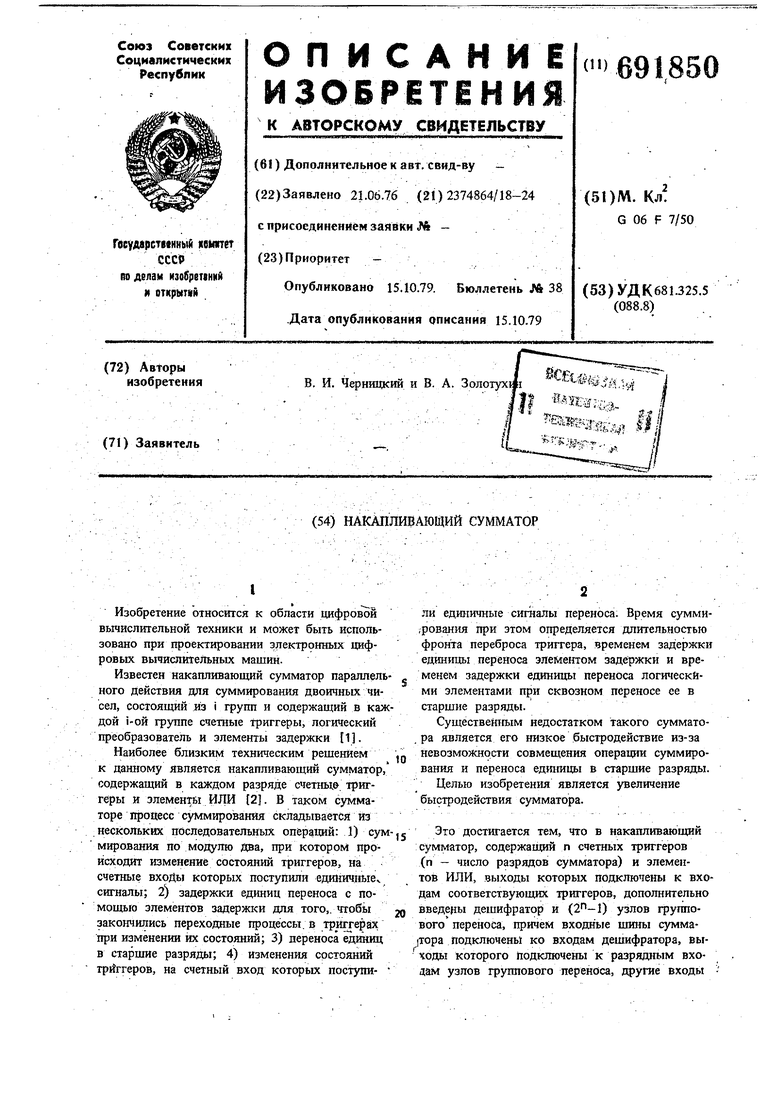

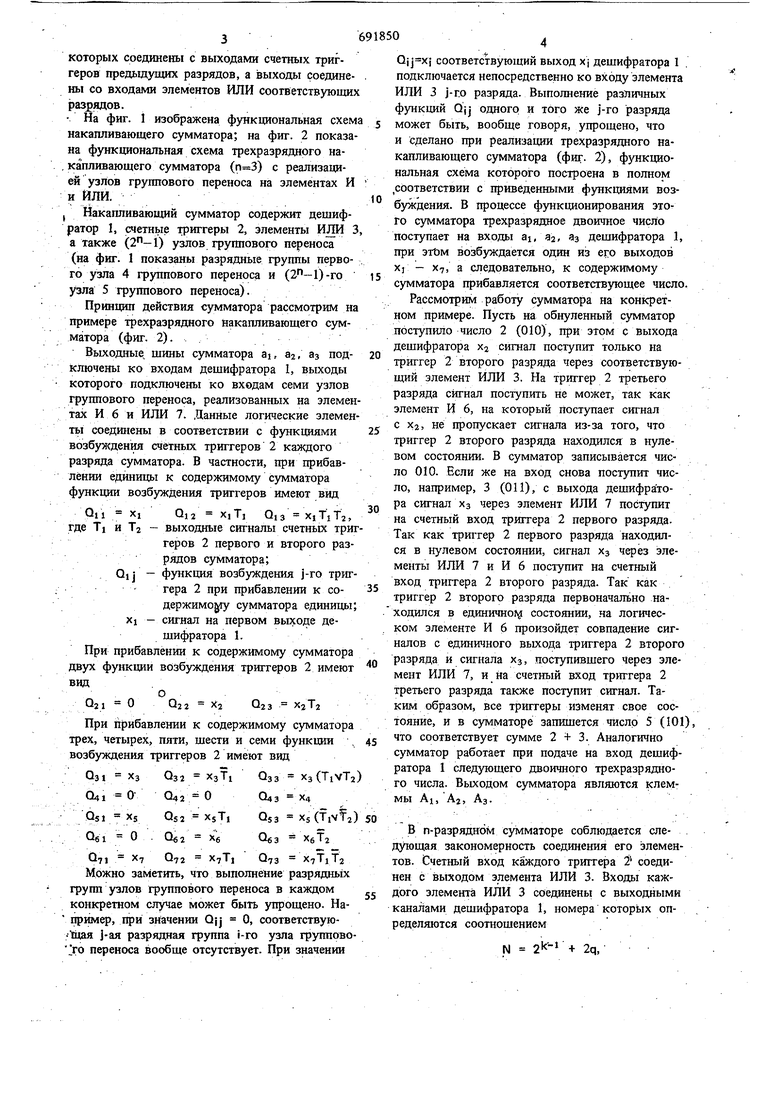

/ . 1 , - - Изобретение относится к области цифровой вычислительной техники и может быть использовано при проектировании электронных цифровых вычислительных машин. Известен накапливающий сумматор параллель ного действия для суммирования двоичных чисел, состоящий из i групп и содержащий в каж дои i-ой группе счетные триггеры, логический преобразователь и элементы задержки 1. Наиболее близким техническим решением к данному является накапливающий сумматор, содержащий в каждом разряде счетны. триггеры и элементы ИЛИ 2. В таком сумматоре процесс суммирования складывается из нескольких последовательных операций: 1) сум мировання по модулю два, при котором происходит изменение состояний триггеров, на счетные вхоДы которых поступили единичные сигналы; 2) задержки единиц переноса с помощью элементов задержки для того,, чтобь закончились переходные процессы, в триггерах при изменении их состояний; 3) переноса единиц в старщие разряды; 4) изменения состояний триггеров, на счетный вход которых поступили единичные стпалы переноса. Время сумми.рования при этом определяется длительностью фронта переброса триггера, временем задержки единицы переноса элементом задержки и временем задержки единицы переноса логическими элементами при сквозном переносе ее в старшие разряды. Существен1п 1М недостатком такого сумматора является его низкое быстродействие из-за невозможности совмещения операции суммирования и переноса едгашцы в старшие разряды. Целью изобретения является зтвеличение быстродействия сумматора. Это достигается тем, что в накапливаюш 1й сумматор, содержащий п счетных триггеров (п - число разрядов сумматора) и элементов ИЛИ, выходы которых подключены к входам соответствующих триггеров, дополнительно введены дешифратор и () узлов группового переноса, причем входные шины сумма|Тора подключены ко входам дешифратора, выходы которого подключены к разрядным входам узлов группового переноса, другие входы которых соединены с выходами счетных триггеров предыдущих разрядов, а выходы соединены со входами элементов ИЛИ соответствующих разрядов. На фиг. 1 изображена функциональная схем накапливающего сумматора; на фиг. 2 показана функциональная схема трехразрядного на, капливающего сумматора () с реализацией узлов группового переноса на элементах И и Или. , Накапливающий сумматор содержит дещифратор 1, счетнь1е триггеры 2, элементы ИЛИ 3 а также () узлов группового переноса (на фиг. 1 показаны разрядные группы первого узла 4 группового переноса и ()-го узла 5 группового переноса). Принцип действия сумматора рассмотрим на примере трехразрядного Накапливающего сумматора (фиг. 2). . , Выходные щины сумматора ai, 62, Эз подключены ко входам дещифратора 1, выходы которого подключены ко входам семи узлов группового переноса, реализованных на элемен тах И 6 и ИЛИ 7. Данные логические элемен ть1 соединены в соответствии с функциями возбуждения счетных триггеров 2 каждого разряда сумматора. В частности, при прибавлении единицы к содержимому сумматора функции возбуждения триггеров имеют вид QII X, Qi2 х,Т, ,TiT2, где Tj и Тг - выходные сигналы счетных триг геров 2 первого и второго разрядов сумматора; QIJ - функция возбуждения j-ro трет гера 2 при прибавлении к содержимо сумматора единицы xj - сигнал на первом выходе дещифратора 1. При прибавлении к содержимому сумматора двух функции возбуждения триггеров 2 имеют вид. ,о QZI 0022 Х2QZS Х2Т2 При прибавлении к содержимому сумматора трех, четырех, пяти, щести и семи функции возбуждения триггеров 2 имеют вид Озз X3(TiVT2 ХзОз2 XjTi о- Q42 о 0,3 Х4 Qsa X5(f, XsQ52 XsT, Обз ХбТ2 оОб2 Хб Х7 Q72 Х,, QVS X7TiT2 Можно заметить, что выполнение разряднь1Х групп узлов группового переноса в каждом конкретном случае может быть упрощено. Например, при значении QIJ О, соответствуюШая j-ая разрядная группа i-ro узла группово го переноса вообще отсутствует. При значении соответствующий выход xj дещифратора 1 подключается непосредственно ко входу элемента ИЛИ 3 j-ro разряда. Выполнение различных функций Qjj одного и того же j-ro разряда может быть, вообще говоря, упрощено, что и сделано при реализации трехразрядного накапливающего сумматора (фиг. 2), функциональная схема которого построена в полном ,сЬответствии с приведенными функциями возбуждения. В процессе функционирования этого сумматора трехразрядное двоичное число поступает на входы . 3 дещифратора 1, при этЬм возбуждается один из его выходов X - Х7, а следовательно, к содержимому сумматора прибавляется соответствзтощее число. Рассмотрим работу сумматора на конкретном примере. Пусть на обнуленный cjTviMaTOp поступило число 2 (010), при этом с выхода дешифратора Х2 сигнал поступит только на триггер 2 второго разряда через соответствующий элемент ИЛИ 3. На триггер 2 третьего разряда сигнал поступить не может, так как элемент И 6, на который Поступает сигнал с Х2, не пропускает сигнала из-за того, что триггер 2 второго разряда находился в нулевом состоянии. В сумматор записывается число 010. Если же на вход снова поступит число, например, 3 (011), с выхода дещифратора сигнал Хз через элемент ИЛИ 7 поступит на счетный вход триггера 2 первого разряда. Так как триггер 2 первого разряда находился в нулевом состоянии, сигнал Хз через элементы ИЛИ 7 и И 6 поступит на счетный вход триггера 2 второго разряда. Так как триггер 2 второго разряда первоначально находился в единичнол состоянии, на логическом элементе И 6 произойдет совпадение сигналов с единичного выхода триггера 2 второго разряда и сигнала хз, поступившего через элемент ИЛИ 7, и на счетный вход триггера 2 третьего разряда также поступит сигнал. Таким образом, все триггеры изменят свое состояние, и в сумматоре запишется число 5 (101), что соответствует сумме . Аналогично сумматор работает при подаче на вход дещифратора 1 следующего двоичного трехразрядпого числа. Выходом сумматора являются клеммы АХ, А2, АЗ. В п-разрядн6м сумматоре соблюдается следующая закономерность соединения его элементов. Счетный вход каждого триггера У соединен с выходом элемента ИЛИ 3. Входы каждого элемента ИЛИ 3 соединены с выходными каналами дешифратора 1, номера которых определяются соотношением N 2k- + 2q, где k - номер разряда сумматора, к которому отностся элемент ИЛИ 3; q О, 1, 2... Так со .входом элемента ИЛИ 3 первого /разряда соединяются выходы дешифратора 1 с номерами 1, 1 + , 1 + 2x2,..., то есть все нечетные выходы дешифратора. При N 2, 6, 10, 14,.i.. Кроме того, входы каждого элемента ИЛИ 3 (исключая элемент ЩШ 3 первого разряда) соединены с выходами 2 узлов группового переноса, где Р - номер разряда сумматора. Входы каждого узла rpjoinoBOro переноса соединены с выходами триггеров 2 предыдущих разрядов и выходами дешифратора I. Учитывая, что в дешифраторе сигнал задерживается на одном логическом элементе (элементы включены параллельно), а узел группового переноса содержит не более двух последовательно включенных логических элементов, общее время одного цикла суммирования скла дывается из времени задержки сигнала на четьфех последовательно включенных логических элементах и времени переходы триггера в про тивоположное состояние. Таким образом, быстродействие данного сумматора значительно выше быстродействия известных накапливающих сумматоров, и врем суммирования не зависит от числа разрядов сумматора, что дает возможность тя применения данного сзмматора в современных вычислительных устройствах. Формула изобретения Накапливающий сумматор, содержащий п счетных триггеров (п - число разрядов сумматора), п элементов ИЛИ, выходы которых подключены к входам соответствующих триггеров, отличающийся тем, что, с целью )гвеличения быстродействия, сумматор дополнительно содержит дешифратор и () узлов группового переноса, причем входные шины сумматора подключены ко входам дешифратора, выходы которого подключень к разрядным входам узлов группового переноса, другие входы которых соединены с выходами счетных триггеров предьщущих разрядов, а выходы соединены со входами элементов ИЛИ соответствующих разрядов. Источники информащш, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 482739, кл. G 06 F 7/385, 1973. 2.Анисимов Б. В. и др. Основы теории и проектирования ЭЦВМ. М., Высшая школа, 1970, с. 291-292 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Реверсивное счетное устройство с контролем | 1984 |

|

SU1238232A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

(риг. /

Фиг.2

Авторы

Даты

1979-10-15—Публикация

1976-06-21—Подача