рого соединен с вторым входом седьмого элемента И и с выходом второго элемента ИЛИ, выходы седьмого и восьмого элементов И соединены соответственно с R.H S-входами второго триггера, а выход седьмого элемента И 1-го разряда соединен с третьим входом третьего элемента ИЛИ (i+1)-ro разряда группы разрядов сумматора четвертый вход третьего элемента ИЛИ младшего разряда группы разрядов сумматора соединен с выходом узла группового переноса предыдущей группы разрядов сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| Арифметическое устройство | 1983 |

|

SU1239710A1 |

ДВОИЧНЫЙ НАКАПЛИВАЩИЙ СУММАТОР, содержащий в каждом разряде первый и второй триггеры, четыре элемента И, три элемента ИЛИ, причем каждая группа из К разрядов содержит узел группового переноса и элемент ИЛИ, в каждом разряде сумматора S-вход первого триггера соединен с выходом первого элемента И, первый вход которого соединен с входом данного разряда сумматора, а второй вход - с шиной управления приемом кода сумматора, единичный выход первого триггера соединен с первым входом второго элемента И и с первым входом первого элемента ИЛИ, второй вход второго элемента И соединен с шиной управления первым сложением по модулю два сумматора, а выход подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, нулевой выход второго триггера соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом переноса данного разряда сумматора и первым входом третьего элемента И, выходы первого и третьего элементов ИЛИ подключены к входам четвертого элемента И, выход которого соединен с входом переноса следующего разряда сумматора, второй вход третьего элемента И подключен- к третьей шине управления вторым сложением по модулю два сумматора, выход узла группового переноса соединен с четвертым входом третьего элемента ИЛИ старшего разряда группы разрядов сумматора и к первому входу элемента ИЛИ следуицей группы разрядов сумматора,второй вход которого соединен с выходом четвертого элемента И старшего разряда предыдущей группы разрядов cyt taTopa, а выход соединен с входом переноса узла группового переноса, отличаю(Л щийся тем, что, с целью повышения его быстродействия, он содержит в каждом разряде третий триггер, пятый, шестой, седьмой и восьмой эле§ менты И, причем единичный выход второго триггера соединен d первым входом пятого элемента И, второй вход которого подключен к четвертой шиEND не управления пересылкой кода сумматора, а выход подключен к S-вхбду тре Эд :АЭ тьего триггера, нулевой выход второго триггера соединен с первым входом шестого элемента И, второй вход которого подключен к шине управления пересылкой кода сумматора, а выход соединен с R-входом третьего триггера, единичный выход третьего триггера соединен с первым входом седьмого элемента И и с вторым входом первого элемента ИЛИ, выход которого соединен с входом соответствующего разряда узла группового переноса, нулевой выход третьего триггера соединен с вторым входом восьмого элемента И, второй BXO/I кото

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ, . Известен накапливающий сумматор, содержащий счетный триггер, триггер второго слагаемого, схему сквозного переноса на элементах ИЛИ-И, схему группового переноса, элементы И, ИЛИ и шины управления работой сумматора, причем в каждом двоичном .разряде нулевой вькод счетного триггера подключен к первому входу первого элемента ИЛИ, второй вход этого элемента связан с шиной переноса, поступающего из младшего разряда, выход этого же элемента ИЛИ подключен к первому входу цервого элемента И, а второй его вход связан с нулевым вькодом триггера приемного регистра этого же разряда lj . Недостатком известного сумматора является низкое быстродействие и ограниченные функциональные возможности, заключающиеся в невозможности многократного сложения кода второго слагаемого. Известен также двоичный накапливающий сумматор, содержащий в каждом разряде первый и второй триггеры, четыре элемента И, три элемента ИЛИ кроме того каждая группа из К разрядов содержит узел группового переноса и элемент ИЛИ, в каждом разряде S-вход первого триггера соединен с выходом первого элемента И, первый вход которого соединен с входом данного разряда сумматора, а второй вход - с шиной управления приемом кода сумматора, единичный выход первого триггера соединен с первым входом второго элемента И и с первым входом первого элемента ИЛИ, второй вход второго элемента И соединен с шиной управления первым сложением по модулю два сумматора, а выход подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, нулевой выход второго триггера соединен с первым входом третьего элемента ИЛИ, второй.вход которого соединен с входом переноса данного разряда сумматора, и первым входом третьего элемента И, выходы первого и третьего элементов ИЛИ подключены к входам четвертого элемента И, выход которого соединен с входом перено са следующего разряда и с первым входом третьего элемента И следующего разряда сумматора, второй вход третьего элемента И подключен к шине управления сумматора вторым сложением по модулю два,выход узла группового переноса соединен с третьим входом третьего элемента ИЛИ старшего разряда группы разрядов сумматора и к первому входу элемента ИЛИ следуклцей группы разрядов сумматора, второй вход которого соединен с выходом четвертого элемента И старшего разряда предьщущей группы разрядов сумматора, а выход соединен с входом переноса узла группового переноса, второй триггер содержит счетный вход, подключенный к выходу второго элемента ИЛИ 2 . Недостатком известного сумматора является невысокое быстродействие. Цель изобретения - повышение быстродействия двоичного накапливающего сумматора. Поставленная цель достигается тем, что двоичный накапливающий сумматор, содержащий в каждом разряде первый и второй триггеры, четьфе

элемента -И, три элемента Ш1И, кроме того, каждая группа из К разрядов содержит узел группового переноса и элемент ИЛИ, в каждом разряде сумматора S-вход первого триггера соединен с выходом первого элемента И, первый вход которого соединен с входом данном разряда сумматора, второй вход - с шиной управления приемом кода сумматора, единичный выход первого триггера соединен с первым входом второго элемента И и с первым входом первого элемента ИЛИ, второй вход второго элемента И соединен с шиной управления первым сложением по модулю два сумматора, а выход подключен к первому входу второго, элемента РШИ, второй вход которого соединен с -йыходом третьего элемента И, нулевой зыход второго триггера соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом переноса данного разряда сумматора и первым входом третьего элемента И, выходы первого и третьего элементов ИЖ, подключены к входам четвертого элемента И, выход которого соединен с входом переноса следующего разряда сумматора второй вход третьего элемента И подключен к третьей шине управления вторым сложением по модулю два сумматора, выход узла группового переноса соединен с четвертым входом третьего элемента ИЛИ старшего разряда группы разрядов сумматора и к первому входу элемента ИЛИ следующей группы разрядов сумматора, второй вход которого соединен с выходом четвертого элемента И старшего разряда предыдущей группы разрядов сумматора, а выход соединен с входом переноса узла группового переноса, он содержит в каждом разряде третий триггер, пятый, шестой, седьмой и восьмой элементы И, причем единичный выход второго триггера соединен с первым входом пятого элемента И, второй вход которого подключен к четвертой шине управления пересылкой кода сумматора, а выход подключен к S-входу третьего триггера, нулевой выход второго Tpv.rrepa j соединен с первым входом шестого элемента И, второй вход которого подключен к шине управления пересылкой кода сумматора, а выход соединен с R-входом третьего триггера, единич-ный выход третьего триггера соединен с первым входом седьмого элемента И и с вторым входом первого элемента ИЛИ, выход которого соедин с входом соответствующего разряда узла группового переноса, нулевой выход третьего триггера соединен с вторым входом восьмого элемента И, второй вход которого соединен с вторым входом седьмого элемента И и с выходом второго элемента ИЛИ, выходы седьмого и восьмого элементов И соединены соответственно с R- и S-входами второго триггера, а выход седьмого элемента И i -го разряда соединен с третьим входом третьего элемента ИЛИ (+1)-го разряда группы разрядов сумматора, четвертый вход третьего элемента ИЛИ младшего разряда группы разрядов сумматора соединен с выходом узла группового переноса предыдущей группы разрядов сумматора.

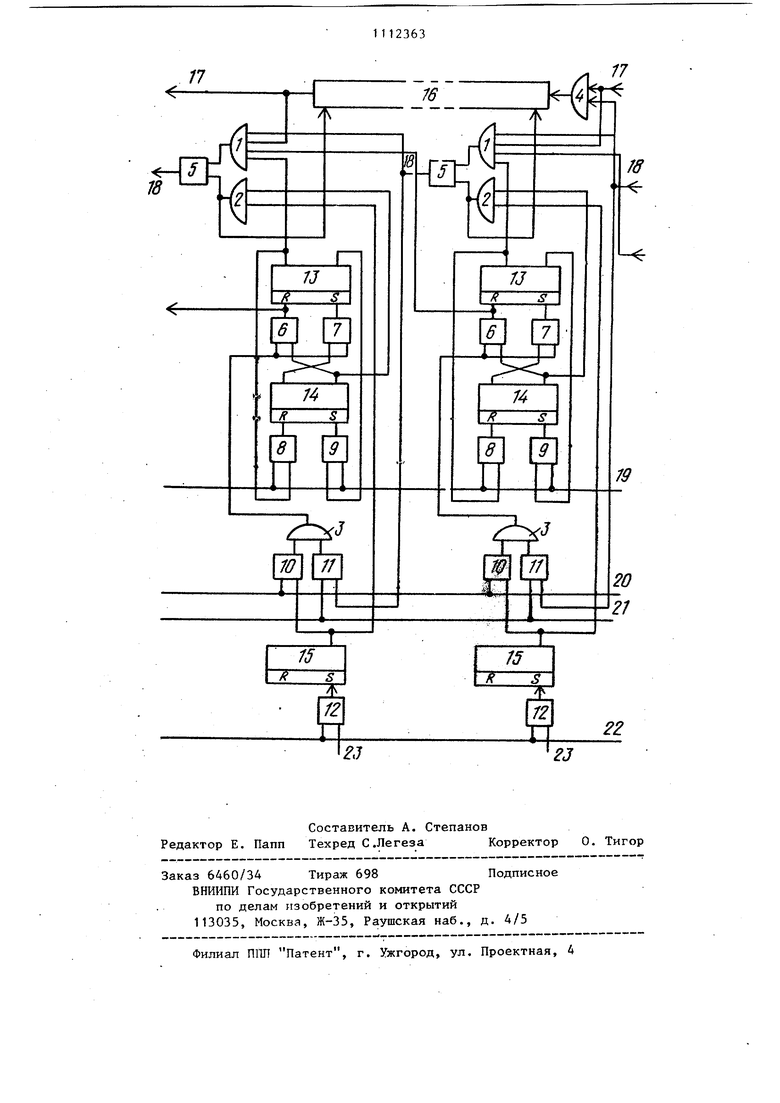

На чертеже представлена функциональная схема двух разрядов двоичного накапливающего сумматора.

Сумматор содержит элементы ИЛИ 1-4, элементы И 5-12, триггеры 13-15 и узел 16 группового переноса, который в данном случае представляет собой элемент И с (Кн-1) входом, где К - разрядность группы разрядов сумматора.

Каждый узел группового переноса сумматора содержит вход 17 переноса, а младший разряд групп- вход 18 переноса i Сумматор содержит также шину

19управления пересыпкой кода, шину

20управления первым сложением по Модулю два, шину 21 управления вторы сложением по модулю два, шину 22 управления приемом кода, а также инфор мационные входы 23.

Работает двоичный накапливающий сумматор следующим образом.

Предположим, что код первого слагаемого хранится в триггерах основно ступени (триггеры 13), а код второго слагаемого поступает в триггеры 15 по шинам 23.

По первому временному такту (i) выполняются элементарные операции (ЭО) приема кода второго слагаемого в приемный регистр (триггеры 15) и пересылки кода из основной ступени (триггеры 13) во вспомогательную ступень (триггеры 14). Для выполнения этих ЭО на шины 19 и 22 одновременно подаются исполнительные импульсы. 5 По второму временному такту (tg) вьтолняется ЭО первого сложения по модулю два кодов, хранящихся в осно ной и вспомогательной ступенях и в приемном регистре. Для выполнения згой ЭО на шину 20 подается исполни тельный импульс, Если в -м разряд триггера 15 хранится код единицы, то исполнительный импульс по цепи элементов И 10- ИЛИ 3 поступит на вторые входы элементов И 6 и 7. В зависимости от кода, хранящегося в триггере 14, исполнительный импул поступит на нулевой или единичный вход триггера 13. Если в триггере 14 хранится код нуля, то исполнител Hbrfi импульс поступит через элемент И 7 на единичный вход триггера 13 и.установит его в единичное состояние. Если в триггерах 13 и 14 до по тупления второго исполнительного импульса хранился код единицы, то вт рой исполнительный импульс через эл мент И 6 поступит на нулевой вход триггера 13 и установит его в нулев состояние. Кроме того, этот импульс с выхода элемента И 6 i -го разряда поступит на вход элемента ИЛИ 1 (l+D-ro разряда и будет распростра няться в сторону старших разрядов, если во вспомогательной ступени или в триггере приемного регистра этого разряда будет храниться код единицы. Другими словами еще до переключения основной ступени (тригге ров 13) из единичного состояния в нулевое сформируется поразрядный перенос в i -м разряде и начнет распространяться в сторону старших разрядов сумматора. По третьему временному такту (t вьтолняется ЭО второй пересыпки кода из триггера 13 в триггер 14. В течение выполнения этой ЭО про3должает распространяться потенциал сквозного переноса. По четвертому такту (t.) выполняется 30 второго сложения по модулю два. Для выполнения этой операции на шину 21 подается исполнительный импульс. В тех разрядах, куда поступил потенциал сквозного переноса из младшего разряда (шина 18), исполнительный импульс по цепи элементов И 11 - ИЛИ 3 поступит на вторые входы элементов И 6 и 7 и проинвертирует код триггера 13. Четвертый временный такт завершает выполнение операции сложения двух двоичных кодов. По сравнению с устройством-прототипом предлагаемый сумматор облаладает более высоким быстродействием. Это достигается за счет более раннего начала формирования сигнала переноса по сравнению с формированием переноса в известном сумматоре. В известных сумматорах перенос начинает I формироваться. только после переключения счетного триггера сумматора. В предлагаемом устройстве перенос начинает .формироваться до переключения триггера основной ступени, а так как нулевой вход триггера -го азряда соединен с входами схемы формирования переноса (i+1)-ro разряда, то из суммарного времени формирования переноса вычитается время, равное Ьтр +2 З (t время переключения триггера, т.е. временная задержка сигнала элементами И и ИЛИ). Повьш1ение быстродействия составляет 5-15%. Другим преимуществом предлагаемого сумматора является снижение временных требований к узлу группового переноса, и, следовательно, возможность его упрощения (уменьшения числа вхоов) при сохранении быстродействия.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-07—Публикация

1983-01-07—Подача