(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ РАЗНОСТНЫХ КРАЕВЫХ ЗАДАЧ

ренциаль.ных уровиений, и снижает его напежность.

Наиболее блипким к данному является устройство, содсфжашее блок управления, блок ивода-вывола, первый и второй блоки памяти, выполненные на сдвиговых регистрах, первый и второй сумматоры, первый и второй блоки умножения, группы элементов И, группы элементов И-ИЛИ, причем выходы первых разрядов сдвиговых регистров первого блока Памяти подключены через элементы И первой группы к первой группе входов первого блока умножения, выходы ( N + 1 )х разрядов сдвиговых регистров Второго блока памяти подключены к первым входам элементов И-ИЛИ первой группы, выходы которых соединены с первой группой входов первого блока умножения, группа выходов блока ввода-вывода соединена с первыми входами элементов И-ИЛИ второй группы, выходы которых подключены ко входам первых разрядов сдвиговых регистров первого блока памяти, выходы первого и второго блоков умножения через элементы И второй и третьей групп подключены к первым входам йервого и второго сумматоров соответственно, управляющие входы элементов И всех групп и элементов И-ИЛИ всех групп подключены к выходам блока управления 2.

Рассмотренное устройство имеет ниа кое быстродействие, так как реализует последовательный принцип вычислений. Кроме того, оно имеет ограниченные функциональные возможности, обусловленные тем, что выход сумматора Связан со ВХ.ОДОМ записи информации и первые (левые) разряды второго блока памяти, выходы первых разрядов второго блока памяти связаны с устройством ввода-вывода, вход записи инфч pмaции в первые разряды первого блока памяти связан с устройством ввода-вывода. Поэтому данное устройство не позволяет решать разностные краевые задачи.

Целью изобретения является повышение быстродействия устройства и расширение класса решаемых задач.

Указанная цель достигается тем, что в устройство введены первый и второй блоки деления, причем выходы пбрвого блока деления подключены ко вторым входам элементов И-ИЛИ второй группы выходы второго блока деления соединены с первыми входами элементов И-ИЛИ третьей группы, выходы которых подсоединены ко входам первых разрядов сдви1овых регистров второго блока Пбшятй, выходы первого сумматора подсоединены к первым входам элементов И-ИЛИ четвертой группы и через элементы И четвертой группы с пбрвыми группами входов первого и второго блоков деления, выходы элементов И-ИЛИ четвертой группы сое-; динены с соответствующими входами ( N + J )-х разрядов сдвиговых регистров второго блока памяти, выходы второго сумматора через элементы И пятой группы соединены со второй группой входов Второго блока деления, вторая группа входов первого блока деления через элементы И шестой группы соединены с группой выходов блока ввод э-вь7Вода, выходы ( N 1 )-х разрядов сдвиговьгх регистров второго блока памяти через элементы И седьмой группы подключены ко вторым входам элементов И-ИЛИ третьей группы, к группе входов блока ввода-вывода, и через элементы И восьмой группы ко второй группе входов второго сумматора, группа выходов блока вводавывода соединена со вторыми входами элементов И-ИЛИ первой группы, первыми входами элементов И-ИЛИ пятой группы, и через элементы И девятой группы к первой группе входов второго блока умножения, выходы первых разрядов сдвиговых регистров второго блока памяти соединены со вторыми входами элементов И-ИЛИ четвертой и пятой групп, и через элементы. И десятой группы подключены ко второй группе входов второго блока умножения, выходы элементов И-ИЛИ пятой группы соединены со второй группой входов первого сумматора, управляющие входы блоков памяти, блоков деления, блоков умножения и сумматоров подключены к выходам блока управления.

Такое выполнение устройства обес5печивает его высокое быстродействие за счет совмещения вычислительных операций и процедуры ввода-вывода.

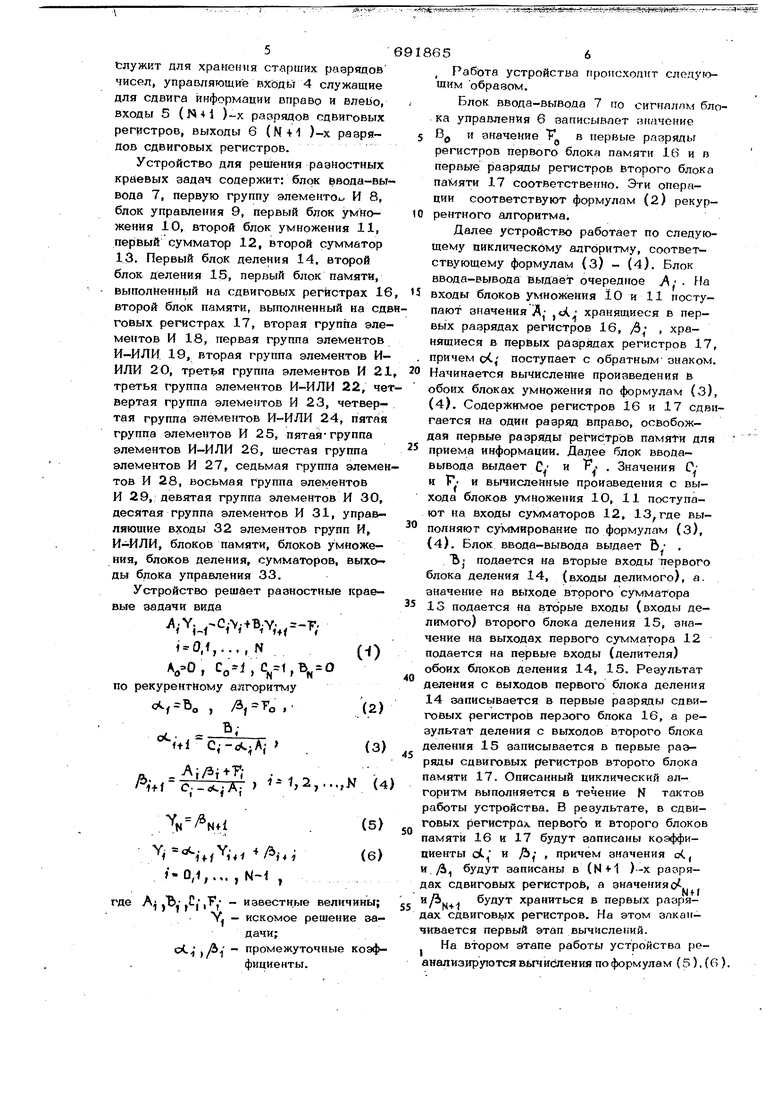

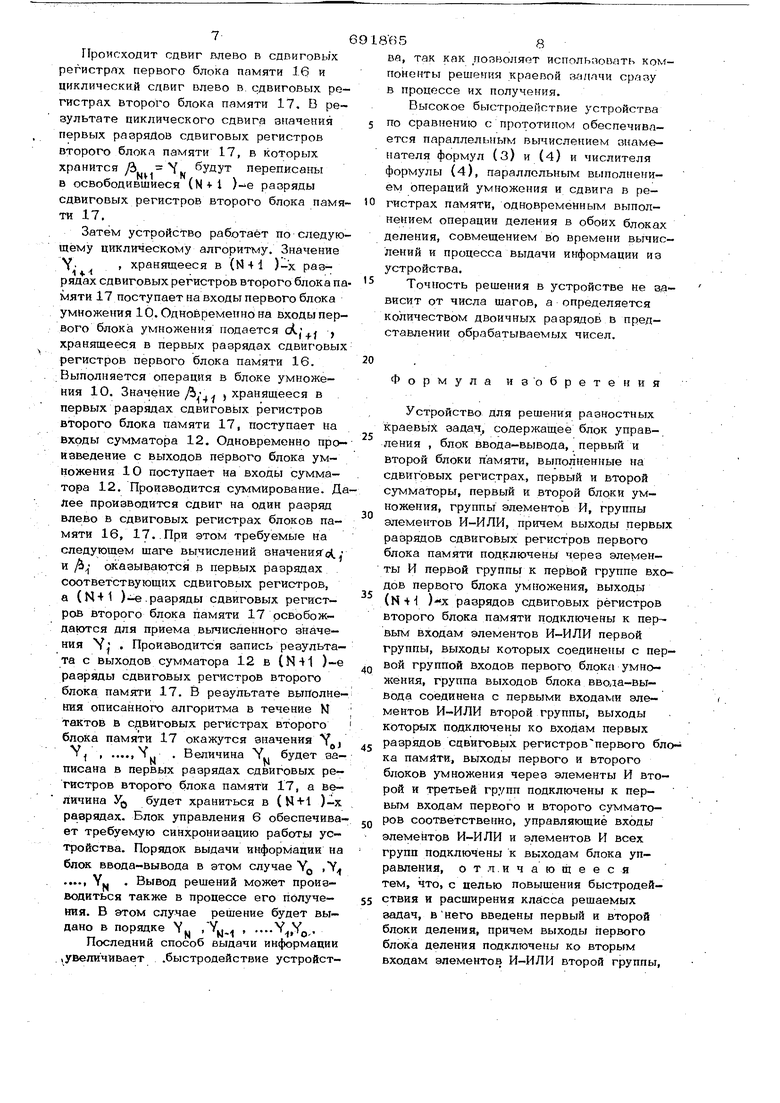

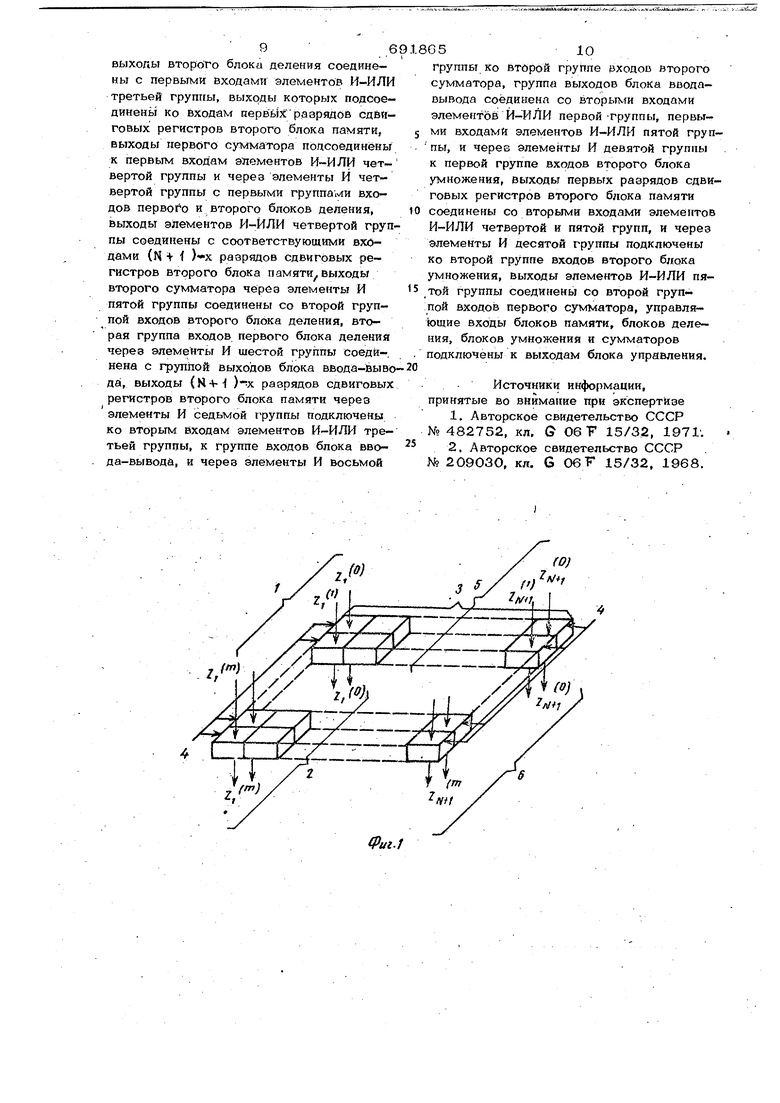

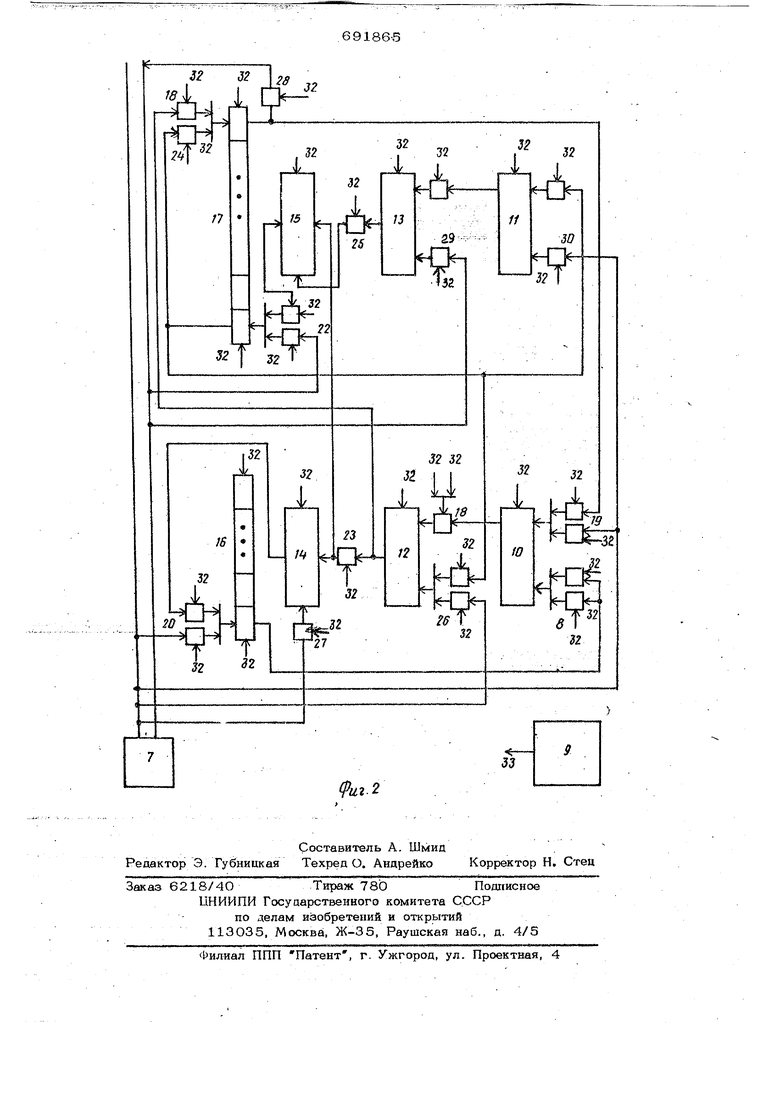

На фиг. 1 показана конструкция блоков памяти,. выполненных на сдвиговых

0 регистрах; на фиг. 2 - схема устройства для решения разностных краевых задач.

Блок памяти выполненный на сдвиговых регистрах имеет входы 1 в первые

5 разряды сдвиговых регистров , выходы 2 информации из первых регистров сдвиговых регистров, сдвиговые реверсивные регистры, один из которых 3 Служит для хранения старших разрядов чисел, управляющие входы 4 служащие для сдвига информации вправо и впеЯо, входы 5 (N + 1 )-х разрядов сдвиговых регистров, выходы 6 {N + 1 )-х разрядов сдвиговых регистров. Устройство для решения разностных краевых задач содержит: блок ввода-вывода 7, первую группу элементо1 И 8, блок управления 9, первый блок умножения 10, второй блок умножения 11, первый сумматор 12, второй сумматор 13. Первый блок деления 14, второй блок деления 15, первый блок памяти. выполненный на сдвиговых регистрах 16 второй блок памяти, выполненный на сдв говых регистрах 17, вторая группа элементов И 18, первая группа элементов И-ИЛИ 19, вторая группа элементов ИИЛИ 20, третья группа элементов И 21 третья группа элементов И-ИЛИ 22, че вертая группа элементов И 23, четвертая группа элементов И-ИЛИ 24, пятая группа элементов И 25, пятая-группа элементов И-ИЛИ 26, шестая группа элементов И 27, седьмая группа элемен тов И 28, восьмая группа элементов И 29, девятая группа элементов И 30, десятая группа элементов И 31, управляющие входы 32 элементов групп И, И-ИЛИ, блоков памяти, блоков умножения, блоков деления, сумматоров, выходы блока управления 33. Устройство решает разностные краевые задачи вида A-Yi-r i%- V,-. 0,f,...,N VO ,,B 0 по рекурентНому алгоритму , . оС; , -fi C,-oC-A; Af/3j+-F; л. -M,2,...,N (4 С..оф5 . i J-0,1,.,. ,М , где А Л-.. - известные величины; . V. - искомое решение . Да, оС,- /Ьу - промежуточные коэффициекты. , Работа устройства происходит следугощим образом. Блок ввода-вывода 7 по cигнaлo блока управления б записывает значение Вд и аначение Т в первые разряды регистров первого блока памяти 16 и в первые разряды регистров второго блока памяти 17 соответственно. Эти операции соответствуют формулам (2) рекуррентного алгоритма. Далее устройство работает по следующему пиклическому алгоритму, соответствующему формулам (З) - (4). Блок ввода-вывода выдает очередное А . На входы блоков умножения 10 и 11 поступают значения Д- Я хранящиеся в первых разрядах регистров 16, /5; , хранящиеся в первых разрядах регистров 17, причем с.; поступает с обратным знаком. Начинается вычисление произведения в обоих блоках умножения по формулам (З), (4). Содержимое регистров 16 и 17 сдвигается на один разрад вправо, освобождая первые разряды регистров пaмяtи для приема информации. Далее блок вводавывода выдает Gv и F- . Значения С; и Г- и вычисленные произведения с выхода блоков умножения 10, 11 поступают На входы сумматоров 12, 13, где выполняюг суммирование по формулам (З), (4). Блок ввода-вывода выдает Ь . bj подается на вторые входы первого блока деления 14, (входы делимого), а. значение на выходе второго сумматора 13 подается на вторые входы (входы делимого) второго блока деления 15, значение на выходах первого сумматора 12 подается на первые входы (делителя) обоих блоков Деления 14, 15. Результат деления с выходов первого блока деления 14 записывается в первые разрвды сдвиговых регистров первого блока 16, а результат деления с выходов второго блока деления 15 записывается в первые разряды сдвиговых регистров второго блока памяти 17. Описанный циклический алгоритм выполняется в течение N тактов работы устройства. В результате, в сдвиговых регистрах первого и второго блоков памяти 16 и 17 будут записаны коэффициенты d и /Ь , причем значения сХ., и./в, будут записаны в (N+-1 )-х разряах сдвиговых регистров, а значенияо храниться в первь.х разряах сдвиговых регистров. На этом злканивается первый этап вычислений. . . , а втором этапе работы устройства реанализируются вьгчиьления по формулам (5), (6 ). Происходит сдвиг влево в сдвиговых регистрах первого блока памяти 16 и циклический сдвиг влево в сдвиговых регистрах второго блока памяти 17. В результате циклического сдвига значения первых разрядов сдвиговых регистров второго блока памяти 17, в которых хранится /Ъ fi У-ИУТ переписаны в освободившиеся (N-vl )-е разряды сдвиговых регистров второго блока памяти 17, Затем устройство работает по следующему циклическому алгоритму. Значение Y,, хранящееся в (N 41 )-х разрядах сдвиговых регистров второго блока па мяти 17 поступает на входы первого блока умножения 10. Одновременно на входы первого блока умножения подается оС, , хранящееся в первых разрядах сдвиговых регистров первого блока памяти 16. Выполняется операция в блоке умножения 10. Значение/ ,. хранящееся в первых разрядах сдвиговых регистров второго блока памяти 17, поступает на входы сумматора 12. Одновременно произведение с выходов первого блока умножения 10 поступает на входы сумматора 12. Производится суммирование. Да лее производится сдвиг на один разряд Влево в сдвиговых регистрах блоков памяти 16, 17..При этом требуемые на следующем щаге вычислений значения о(. и /i оказываются в первых разрядах соответствующих сдвиговых регистров, а (N41 ).:-е .разряды сдвиговых регистров второго блока памяти 17 освобождаются для приема вычисленного значения . Производится запись результа- та с выходов сумматора 12 в (N41 )-е разряды сдвиговых регистров второго блока памяти 17. В результате выполнения описанного алгоритма в течение N тактов в сдвиговых регистрах второго блока памяти 17 окажутся значения V Y . Величина Y.J будет записана в первых разрядах сдвиговых регистров второго блока памяти 17, а ве- л:ичина У, будет храниться в (М-И )-х разрядах. Блок управления 6 обеспечива ет требуемую синхронизацию работы устройства. Порядок выдачи информации на блок ввода-вывода в этом случае YQ ,Y ..... YU . Вывод решений может производиться также в процессе его получения. В этом случае решение будет выдано в порядке | XiH ) Последний способ выдачи информации «увеличивает .быстродействие устройства, так как позволяет использовать компоненты решения краевой вапачи сразу в процессе их получения. Высокое быстродействие устройства по сравнению с прототипом обеспечивается параллельным вычислением знаменателя формул (З) и (4) и числителя формулы (4), параллельным выполнением операций умножения и сдвига в регистрах памяти, одновременным выполнением операции деления в обоих блоках деления, совмещением во времени вычислений и процесса выдачи информации из устройства. Точность решения в устройстве не зависит от числа шагов, а определяется количеством двоичных разрядов в представлении обрабатываемых чисел. Формула изобретен и Устройство для решения разностных краевых задач, содержащее блок управления , блок ввода-вывода, первый и второй блоки памяти, выполненные на сдвиговых регистрах, первый и второй сумматоры, первый и второй блоки умножения, группы элементов И, группы элементов И-ИЛИ, причем выходы первых разрядов сдвиговых регистров первого блока памяти подключены через элементы И первой группы к первой группе входов первого блока умножения, выходы (N-vl )Х разрядов сдвиговых регистров второго блока памяти цодключены к пер-вым входам элементов И-ИЛИ первой группы, выходы которых соединены с первой группой входов первого блока умножения, группа выходов блока ввода-вывода соединена с первыми входакси элементов И-ИЛИ второй группы, выходы которых подключены ко входам первых разрядов сдвиговых регистровпервого блока памйти, выходы первого и второго блоков умножения через элементы И второй и третьей групп подключены к первым входам первого и второго суммато- ров соответственно, управляющие входы элементов И-ИЛИ и элементов И всех групп подключены к выходам блока управления, отл.ичающееся тем, что, с целью повышения быстродей- ствия и расширения класса решаемых задач, внего введены первый и второй блоки деления, причем выходы первого блока деления подключены ко вторым входам элементов И-ИЛИ второй группы. выходы второго блока деления соединены с первыми входами элементов И-ИЛИ третьей группы, выходы которых подсоединены ко входам первых разрящов сдвиговых регистров второго блока памяти, выходы первого сумматора подсоединены к первым входам элементов И-ИЛИ четвертой группы и через элементы И четвертой группы с первыми группа. входов первого и второго блоков деления, выходы элементов И-ИЛИ четвертой груп пы соединены с соответствующими входами (N f )-х раврядов сдвиговых регистров второго блока памяти выходы второго сумматора через элементы И пятой группы соединены со второй группой входов второго блока деления, вторая группа входов первого блока деления через элеме 1ты И шестой группы соеди-. йена с группой выходов блока ввода-йыво да, выходы (N-bl )-х разрядов сдвиговых регистров второго блока памяти через элементы И седьмой группы подключены ко вторым входам элементов третьей группы, к группе входов блока ввода-выводй, и через элементы И восьмой группы Ко втброй группе входов второго сумматора, группа выходов блока вводавывода соединена со вторыми входами элементов Й-ИЛИ первой-группы, первыми входами элементов И-ИЛИ пятой группы, и черев элементы И девятой группы к первой группе входов второго блока умножения, выходы первых разрядов сдвиговых регистров второго блока памяти соединены со вторыми входами элементов И-ИЛИ четвертой и пятой групп, и через элементы И десятой группы подключены ко второй группе входов второго блока умножения, выходы элементов И-ИЛИ пятой группы соединены Со второй группой входов первого сумматора, управляющие входы блоков памяти, блоков деления, блоков умножения к сумматоров подключены к выходам блока управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №482752, кл, G 06 F 15/32, 197Г. 2. Авторское свидетельство СССР № 209030. кл. G ОбТ 15/32, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения разностных краевых задач | 1977 |

|

SU732881A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОЙ ПРОГРАММЫ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СИСТЕМЫ | 2007 |

|

RU2358320C2 |

| Вычислительная система для решения дифференциальных уравнений | 1978 |

|

SU771674A1 |

| Устройство для определения функции | 1973 |

|

SU521570A1 |

| Устройство для вычисления степенных функций | 1977 |

|

SU682895A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНЫХ ПРОГРАММ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СРЕДСТВ СИСТЕМЫ | 2009 |

|

RU2429542C2 |

4

fPut.1

Авторы

Даты

1979-10-15—Публикация

1977-06-01—Подача