1

Изобретение относится к области цифровой вычислительной техники и может найти применение для аппаратного вычисления функций в специализированных вычислителях,

Известно устройство 1, выполняющее онерацию возведения в степень путем последовательного вычисления двух элементарных функций.

Схема этого устройства сложна, функциональные возможности его ограниченные.

Наиболее близким по технической сущности к предложенному является устройство 2 для определения функции , содержащее щесть сдвиговых регистров, регистр, выход которого соединен со входами первого и второго сдвиговых регистров, блок управления, выходы которого подключены ко входам сдвиговых регистров и входу блока памяти, сумматоры, блоки анализа сходимости и знака. Вход последнего подключен к выходу первого разряда третьего сдвигового регистра, а выход - к первым входам первого, второго и третьего сумматоров. Второй и третий входы первого сумматора соединены с выходами (соответственно) блока памяти и третьего сдвигового регистра, а выход - со входом третьего сдвигового регистра. Второй и третий входы второго сумматора соединены с выходами второго и четвертого сдвиговых регистров, а его выход - со входом четвертого сдвигового регистра. Второй и третий входы третьего сумматора соединены с выходами соответственно пятого и первого сдвиговых регистров, а его выход - с первым входом четвертого сумматора, второй вход которого и выход подключены (соответственно) к выходу и входу щестого сдвигового регистра. Выход четвертого сдвигового регистра соединен со входом пятого сдвигового регистра.

Известное устройство имеет ограниченный класс решемых задач.

Цель изобретения - расширение класса рещаемых задач за счет возможности определения функции .

Для реализации цели устройство содержит пятый, щестой и седьмой сумматоры, седьмой и восьмой сдвиговые регистры, первый и второй блоки сдвига. Выход блока анализа знака соединен с первым входом шестого сумматора, выход регистра - со входом седьмого сдвигового регистра, выход которого подключен к первОлМу входу пятого сумматора, второй вход которого соединен с выходом первого блока сдвига, а выход - со вторым входом шестого сумматора, третий вход которого соединен с выходом второго блока сдвига, а выход - с

первым входом седьмого сумматора. Второй вход последнего связан с выходом восьмо о сдвигового регистра, вход которого соединен с выходом седьмого сумматора. Выходы шестого и четвертого сдвиговых регисгров соединены (соответственно) со входами первого и второго блоков сдвига. Ьыходы блока управления соединены с управляющими входами седьмого и восьмого сдвиговых регистров и со вторыми входами первого и второго блоков сдвига.

Такое схемное решение обеспечивает вычисление в одной структуре одновременно произведения двух аргумептов, произведения одного аргумента на квадрат второго и произведения одного аргумента на третью степень второго.

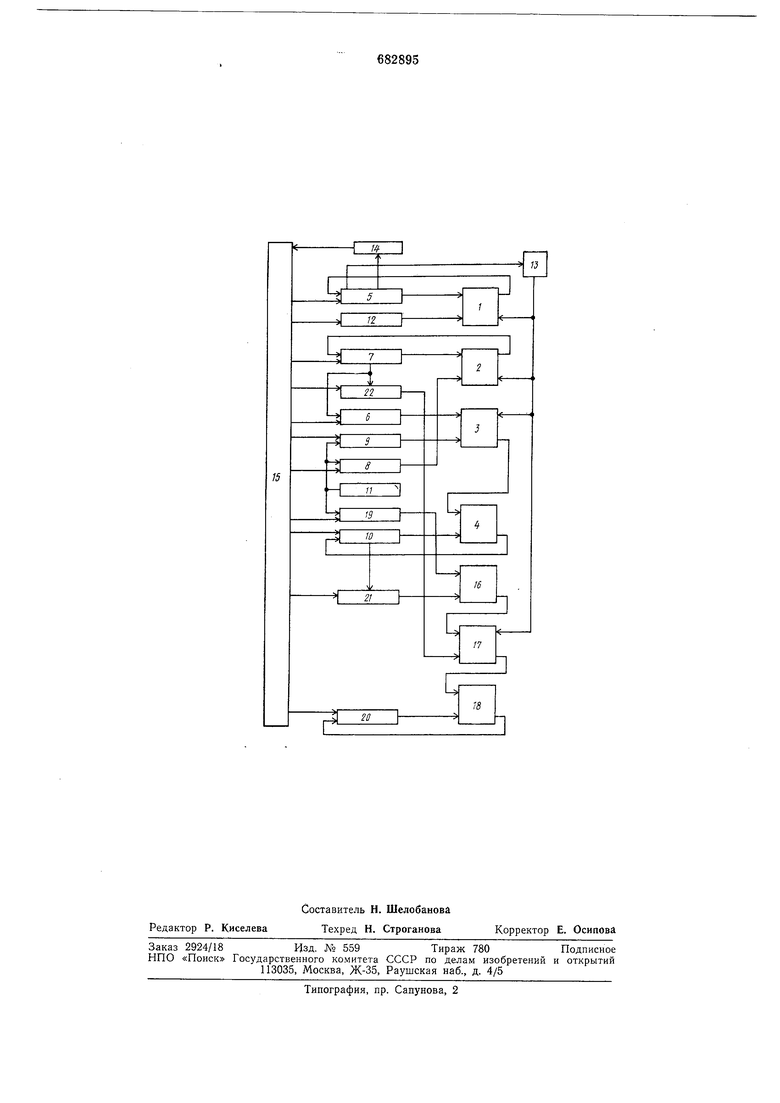

На чертеже изображена блок-схема описываемого устройства. Устройство содержит сумматоры 1-4, сдвиговые регистры о-10, регистр 11, блок 12 памяти, блок i3 анализа знака, блок 14 анализа сходимости, блок 15 управления, сумматоры 16-18, сдвиговые регистры 19-20, блоки 21-22 сдвига.

В качестве сумматоров 1-4 и 16-18 могут быть применены одноразрядные сумматоры-вычптатели комбинационного типа. Блок 12 памяти представляет одностороннее запоминающее устройство с поразрядной выборкой значения константы вида 2-U+1J каждым тактовым импульсом. Ьлок 13 анализа знака содержит триггер и логические элементы. Блок 14 анализа сходимости представляет собой цифровую схему сравнения для сравнения содержания сдвигового регистра о с логическим нулем. Блок 15 управления содерл ит генератор тактовых импульсов, распределитель, логические элементы. Блоки 21-22 сдвига могут содержать сдвиговые регистры и сумматор.

Входами устройства являются для аргумента X - входы разрядов регистра И, для аргумента у - входы разрядов сдвигового регистра 5. Выходами устройства являются для функции х,у -выход сдвигового регистра 7, для функции ху - выход сдвигового регистра 10 и для функции ху- - выход сдвигового регистра 20.

В описываемом устройстве реализуется разностно-итерационный алгоритм, который позволяет заменить операции возведения в квадрат и куб с последующими умножениями одновременно выполняемыми операциями псевдоделепия и псевдоумножения с сохранением постоянной величины одного из операндов. Этот алгоритм может быть представлен в виде системы рекуррентных соотношений, например, для двоичной системы счисления с фиксированной запятой: - у.

Wj.. 1 у ,-i Wj - I)

I +1 при ш. ssO q, - Sign ),-

I -1 при

0.

гл}„

U. Q

,.i Uj-{- qjX-2-(Jи„

xy

z, Q

Zj+i - Zj + qjUj2 J + л: X X2-20-+1);

,

1/y+i ,, qjZj. 3.2-(/4-) + + 6,.3-2-2(+1) 4- ..д;2-зач1)1/ я-у

где j 0, 1, 2,... n (n -число разрядов).

Рекуррентные соотношения вычисляются одновременно (параллельно) в итерационном процессе. Каладое рекуррентное соотношение в описываемом устройстве вычисляется последовательно за п-{-т тактов, где / 2 {Iog2rt} число дополнительных защитных разрядов для компенсации погрешности усечения чисел при сдвиге.

Вычисление указанных функций в описываемом устройстве выполняется следующим образом.

Первоначально в регистр 11 (и в сдвиговые регистры 8, 9 и 19) заносится значение первого аргумента х, в сдвиговый регистр 5 - значение второго аргумента у. сдвиговые регистры 6, 7 и 10 и 20 устанавливаются в нулевое состояние.

В любой /-Й итерации с выхода блока 15 управления выдаются последовательности (серии) тактовых импульсов, которые сдвигают соответствующие значения в сдвиговых регистрах 6, 8, 9, 19 и блоках 21-22 сдвига и продвигают содержания сдвиговых регистров 6-10, 19-20 и блоков 21-22 на соответствующие входы сумматоров 1-4, 16-18, а также поразрядно выдают константу 2(-+ с выхода блока 12 памяти на второй вход сумматора 1. С выходов сдвигового регистра 6 и блока 22 выдаются значения Uj2 и t/j 3 ) соответственно. С выходов сдвиговых регистров 8, 9 и 19 выдаются значения , ) и соответственно. С выхода блока 22 сдвига выдается значения 2j 3 2-04-1). р. зультаты каждой итерации с выходов сумматора 1, 2, 4 и 18 записываются младшими разрядами вперед в освобождающиеся при сдвиге старшие разряды сдвиговых регистров 5, 7, 10 и 20 и продвигаются к началу этих сдвиговых регистров. По знаку содержания сдвигового регистра 5 в конце каждой итерации определяется очередная (для следующей итерации) цифра оператора qj, которая при положительном содержании сдвигового регистра 5 (.) определяет вычитание в сумматоре 1 и сложение в сумматорах 2, 3 и 17. При отрицательном содержании сдвигового регистра 5 (gj - 1) режим работы сумматоров 1-3

и 17 заменяется на обратный, сумматоры 4, 16 и 18 всегда работают только в режиме сложения.

Процесс вычисления заканчивается при равенстве нулю содержания сдвигового регистра 5. При этом с выхода блока 14 анализа сходимости выдается сигнал, останавливающий работу блока 15 управления на следующей итерации. Для большинства значений аргументов х li у процесс вычисления заканчивается на итерации с номером меньше значения / л.

В конце вычисления в сдвиговом регистре 7 содержится значение произведения двух аргументов (), в сдвиговом регистре 10 - значение произведения первого аргумента на квадрат второго (), в сдвиговом регистре 20 - значение произведения первого аргумента на куб второго (), а в сдвиговых регистрах 5, 6, 8, 9 и 19- нулевые значения.

Предложенное устройство позволяет значительно расширить класс решаемых задач по сравнению с устройством-прототипом, при одновременном упрощении устройства и повышени иего быстродействия.

Формула изобретения

Устройство для вычисления степенных функций, содержащее шесть сдвиговых регистров, регистр, выход которого соединен со входами первого и второго сдвиговых регистров, блок управления, выходы которого подключепы ко входам сдвиговых регистров и входу блока памяти, сумматоры, блоки анализа сходимости и знака, вход последнего подключен к выходу первого разряда третьего сдвигового регистра, а выход - к первым входам первого, второго и третьего сумматоров, второй и третий входы первого сумматора соединены с выходами соответственно блока памяти и третьего сдвигового регистра, а выход - со входом третьего сдвигового регистра, второй п третий входы второго сумматора соединены с выходами второго п четвертог-i сдвиговых регистров, а его выход - со входом четвертого сдвигового регистра, второ. и третий входы третьего сумматора соединены с выходами соответственно пятого i; первого сдвиговых регистров, а его выходс первым входом четвертого сумматора, второй вход которого и выход подключень соответственно к выходу п входу шестого сдвигового регистра, выход четвертого сдвигового регистра соединен со входом пятого сдвигового регистра, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности определения функции , устройство содержит пятый, шестой н седьмой сумматоры, седьмой и восьмой сдвиговые регистры, первый и второй блоки сдвига, причем выход блока анализа знака соединен с первым входом шестого сумматора, выход регистра соединен со входом седьмого сдвигового регистра, выход которого соединен с первым входом пятого сумматора, второй вход которого соедппен с выходом первого блока сдвига, а выход - со вторым входом шестого сумматора, третий вход которого соединен с выходом второго блока сдвига, а выход - с первым входом седьмого сумматора, второй вход которого связан с выходом восьмого сдвигового регистра, в.чод которого соедииен с выходом седьмого сумматора, выходы шестого и четвертого сдвиговых регистров соединены соответственно с входами первого и второго блоков сдвига, выходы блока управления соединены с управляющими входами седьмого п восьмого сдвиговых регистров и со вторыми входами первого и второго блоков сдвига.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР .NO 234753, кл. G 06F 7/38, 1969.

2.Авторское свидетельство СССР АО 521570, кл. G 06F 15/34, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для определения функции | 1973 |

|

SU521570A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

Авторы

Даты

1979-08-30—Публикация

1977-05-26—Подача