(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИИ Z Xy

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Устройство для вычисления степенных функций | 1977 |

|

SU682895A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU607223A1 |

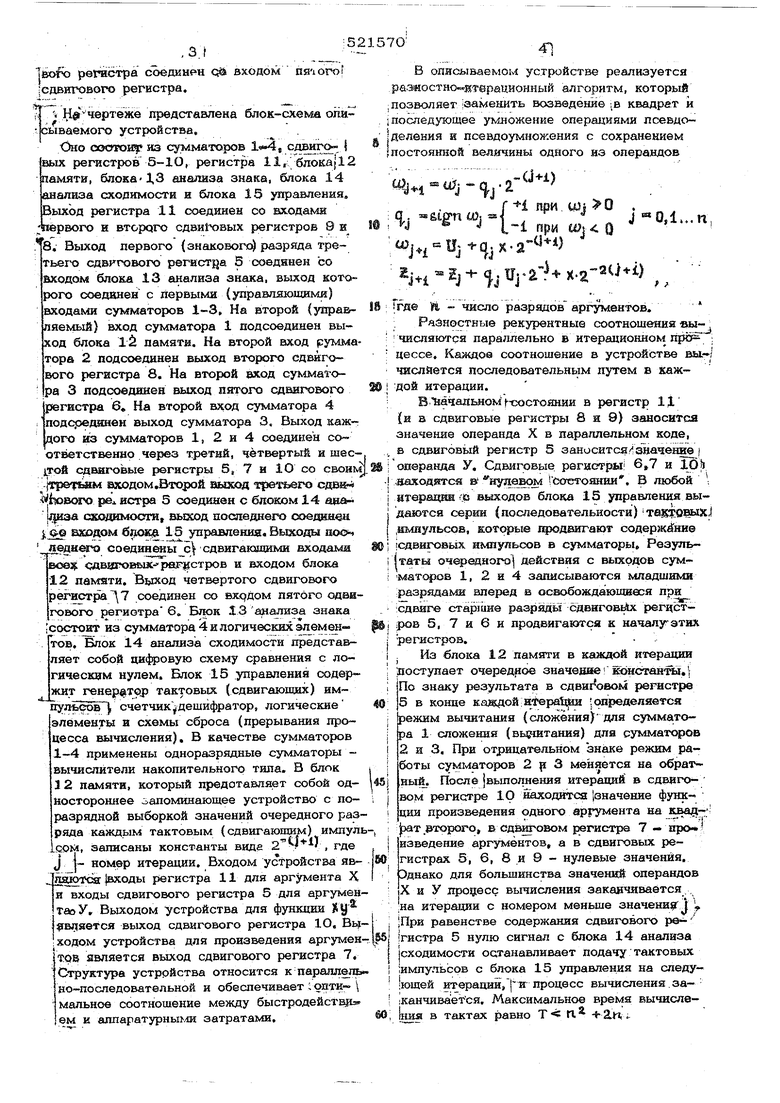

Изобретение относится к цифровой вычислительной технике и может найти приме.нение для аппаратного вычисления функции ;в специализированных цифровых вычислитель- . ных машинах и устройствах. Известнь арифметические устройства, вь числяющие степенные функции, содержащие счетчики, конические элементы и регистры. Наиболее близким техническим решением к изобретению является арифметическое устрой :ство специализированных цифровых вычислительных машин, которое выполняет операцию |определения функции произведения одного аргумента на квадрат другого косвенно, путем последовательного вычисления двух элемен- тарных функций. Известное устройство содер жит шесть сдвиговых регистров, регистр, вы ход которого соедйнен со входами первого и второго сдвиговых регистров, блок управления, выходы которого подключены ко входам сдвиговых регистров и входу блока памяти, сумматоры, блоки анализа сходимости и знака. Известное арифметическое устройjCTBO характеризуется сложностью и большим временем вычисления. i Целью изобретения является упрощение устройства, а также повышение его быстро- действия, В описываемом устройстве это достигается тем, что в нем вход блока анализа сходимости соединен с выходом третьего сдвигового регистра, а выход - со блока управления, вход блока анализа .знака подключен к выходу первого разряда третьего сдвигового регистра, а выход- к лервым входам первого, второго и третьего сумматоров, второй к третий входы .первого сумматора соединейы с выходом блока памяти и выходом третьего сдвигового регистра, а выход - со входом третьего сдвигового регистра, второй и третий входы второго ,сумматора соединены с выходами второго и четвертого сдвиговых регистров, а его выход - со входом четвертого сдвигового ре|гистра, второй и третий входы третьего сумматора соединекл с выходами пятого и сдвиговых регистров, а его выход - с Ьервым входом четвертого сумматора, вто- рой вход которого подключен к выходу шестого сдвигового регистра, а выход - ко входу этого регистра, выход четвертого сдвигоTjEjofo рв№стра соедкнрн ой входом nsioro |едвигового регистра. V Hgt чертеже представлена блок-схеьш oiiaюаемого устройства. Оно ооотои из сумматоров , сдвиговых регистров 5-10, регистра 11, блока; 12 памяти, блока-3,3 анализа знака, блока 14 анализа сходимости и блока 15 управления. Выход регистра 11 соединен со входами -первого и второго сд8и1овых регистров 8 и 8, Выход первого {знакового) разряда третьегч) сдвигового регистра 5 ооедкнен со входом блока 13 анализа знака, выход которого соединен с первыми (управляющими) входами сумматоров 1-3, На второй (упра&ляемый) вход сумматора 1 подсоединен выход блока паматй. На второй вход румма торе 2 подсоединен выход второго сдвигового регистра 8. На второй вход сумматора 3 подсоединев выход пятого сдвигового регистра 6« На второй вход сумматора 4 подсре/шнен выход сумматора 3. Выход каждого из сумматоров 1, 2 и 4 соединен соответственно через третий, четвертый н шееijoft сдвиговые регистры 5, V и 10 со своим |третьйм входом .Второй выкод третьего сдвнц 1 Ьэвсюо ре нстра 5 соединен с блоком 14 ава сзшдимоотя, выход последнего ооедии а j; ВХОДОМ бйок 15 управпения. Выходы коо, соединены с}сдвигакадими входамя все М вщч вык рег стров и входом блока 12 памяти. Вьпсод четвертого сдвигового регистра 7 соединен со входом пятого сщвигового регистра 6. Блок 13 шализа знака состоит из сумматора 4 и логических элемштов. Блок 14 анализа сходимости представляет собой ци4ровую схему сравнения с логическим нулем. Блок 15 управления содер жит генеретор тактовых (сдвигающих) им пульсов } счетчик дешифратор, логические элементы и схемы сброса (прерывания процесса вычисления), В качестве сумматоров 1-4 применены одноразрядные сумматоры вычислители накопительного типа, В блок 12 памяти, который предотавляет собой одностороннее запоминающее устройство с поразрядной выборкой значений очередного раз ряда каждым тактовым (сдвигающим) импул ) COM, записаны константы виде J |- номер итерации. Входом устройства явragOTfcaar }входы регистра 11 для аргумента X и входы сдвигового регистра 5 для аргумен твоУ. Выходом устройства для функции )69 гв1|яеТся выход сдвигового регистра 1О, Вы ходом устройства для произведения аргумен TOS является выход сдвигового регистра 7, Структура устройства относится к параллель но-последовательной и обеспечивает ; опти мальное соотношение между быстродейств ь ем и алпаратурны /ш затратами. :S 0 В описываемом устройстве реализуется ра.шостн& нтбраи,ионный алгоритм, который позволяет заменить возведение IB квадрет и последующее умножение операциями лсевдо- деления т псевдоумножения с сохранением постоянной величины одного из операндов ) « при u)j О |,. &LgnWi ,l.,.n, При Ш| -г-а.к.э-) г Hj-H ljIIjr - -X.a) ыiTAe Н число разрядов аргументов. . Разностные рекурентные соотношения вы--. : числяются параллельно в итерационном ripS ; цессе. Каждое соотношение а устройстве вы-/ числйется последовательным путем 8 каждой итерации. В йачаяьиом состоянии в регистр 11 (ив сдвиговые регистры 8 а 9) заносится значение операнда X в параллельном коде, в сдвиговый регистр 5 заниситсяИзЪачеше | оиеранда У, Сдвиговые регистры и idjj находятся В нулежш ссгстоянии. В любой итераднн :,& выходов блока 15 управления выдаются серии (последовательности) такгошлх.1 ,ш.шульсов, которые продвигают содержание |сдвиговых импульсов в сумматоры, Резуль|таты оч едного действия с выходов сумматс юв 1, 2 и 4 записываются младшими разрядами вперед в освобождающиеся при :сдвиге старшие разряды сдвиговьАх регистров 5, 7 и 6 и продвигаются к началу этих регистров. - Из блока 12 памяти в каждой итерации ;поступает очередное значение Шнстанты, По знаку результата в сдвиговом регистре 5 в конце каждой Hifepal .определяется режим вычитания (сложения) для сумма.тора 1 сложения (вь штания) для cyMMarqpOB 2 и 3. При отрицательном знаке режим работы сумматоров 2 р 3 меняется на обрат ный. После |выполнения итераций а сдвиго- вом регистре 1О шходится |значение функ ции произведения одного аргумента на т.второго, в регистре 7 изведение аргументов, а в сдвиговых регистрах 5, 6, 8 и 9 - нулевые значения. Однако для большинства значений операндов X и У процесс вычисления заканчивается на итерации с номером меньше значение J |При равенстве содержания сдвигового 1гистра 5 нулю сигнал с блока 14 анализа |сходимости останавливает подачу тактовых ;импульсов с блока 15 управления на следу- ющей итераций И процесс вычисления.за- |Канчивается. Максимальное время вычислеиия в тактах равно Т П - -irtt Формула изобретения Устройство для определения функции содвржа1цее шесть сдвиговых .егистров, ре гистр, выход которого соединен со входвеми иервого и второго сдвиговых регистров, блок управления, выходы которого подключе|ны ко входам сдвиговых регистров и входу ;блока памяти, сумматоры, блоки анализа сходимости и зввака, о т л и ч а ю щ е ес я тем, что, с целью упрощения устрой- |ства, вход блока анализа сходимости соеди ен с выходом третьего СДЕ ггового регистЬа, входом блока управления, вход блока анализа знака подключен к выходу первого разряда третьего сдвигового регистра, а выход - к первым входам пер вогр, второго и третьего сумматоров, второй, и третий входы первого сумматора соединеHbf с выходом блока памяти и выходом третьего сдвигового регистра,а выход - со входом третьегосдвигового регистра, второй и третий входы второго сумматора сое I динены с выходами второго и четвертого сдвиговых регистров, а его выход - со вхо-г ; йом четвертого сдвигового регистра, второй 9 третий входы третьего сумматора соедине-. ны с выходами пятого и первого сдвиговых регистров, а его выход - с первым входо л (четвертого сумматора, второй вход которо;го подключен к выходу шестого сдвигового Ьегистра, а выход кй входу этогхэ регист-г ipa, выход четвертого сдвигового регистра ; Соединен со входом пятого сдвигового р€ир гистра,.

Авторы

Даты

1976-07-15—Публикация

1973-07-03—Подача