1

Изобрет-ение относится к вычислительной технике и может быть использовано в универсальных специализированных цифровьк вычислительных системах при решении краевых задач для уравнений в.частных производных и обыкновенных дифферен- 5 циальных уравнений.

Изв-есгно устройство, содержащее блок управления, блок ввода-вывода и второй блоки памяти, .первый и второй сумматоры, первый и второй блоки умножения, эле.менты И, элементы ИЛИ jYj .

Недостатком данного устройства является низкое быстродействие, обусловленное последовательным принципом обработки информации.

Наиболее близким по технической сущности к предложенному является устройство для решения разностных краевых задач, содержащее два блока памяти, блок управления, блок ввода-вьшода, два блока умножения, два блока суммирования, два блока деления, элементы И, элементы ИЛИ И .

Недостаток устройства - сложность схемы, обусловленная наличием двух каналов обработки информации.

Целью изобретения является упрощение схемы устройства.

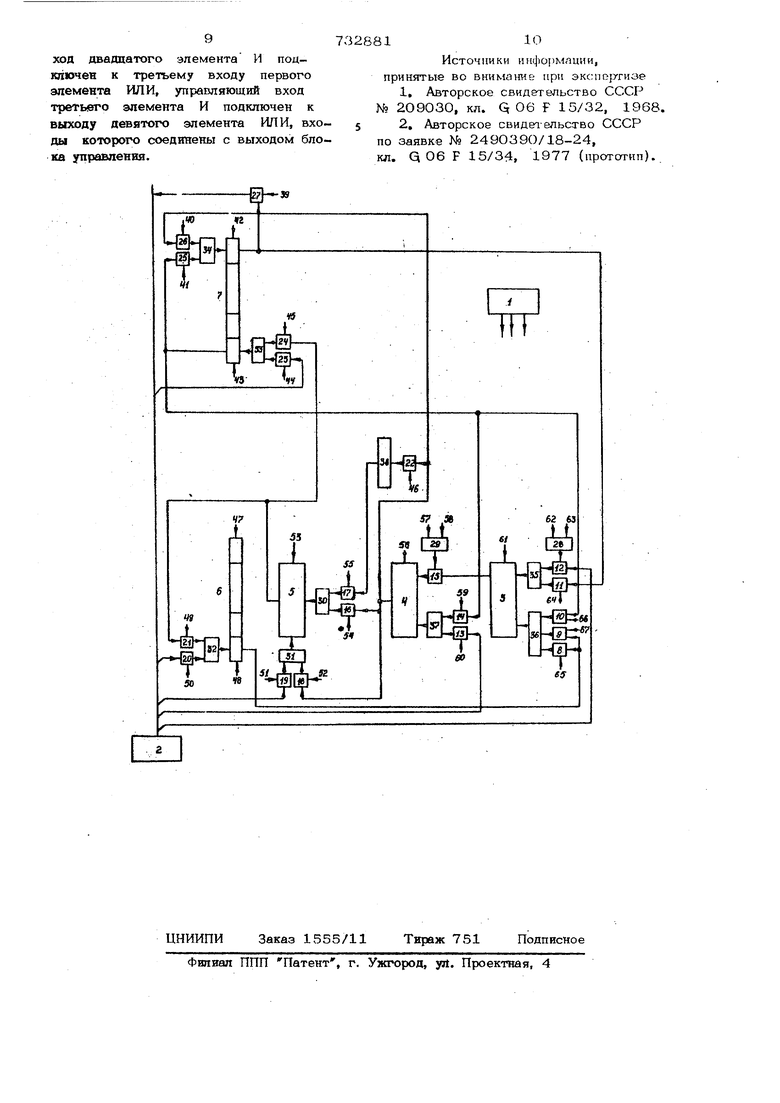

Поставленная цепь достигается тем, что в устройство, содержащее первый блок памяти, выход которого подключен к информационным входам первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход .которого подключен к первому аходу блока умножения, второй в.ход которого соединен с вькодом второго элемента ИЛИ, первый и второй входы которого подключены к выходам третьего и четвертого элементов И, быход блока умножения соединен с информационным, аходом пятого элемента И, управляющий аход которого подключен к выходу третьего элемента ИЛИ, выход пятого элемента И соединен с первым аходом сумматора, второй аход которого подключен к выходу четвертого элепснта ИЛИ, первый и второй аходы которого соединены с выходами шестого и сед мого элементов И, выход сумматора подключен к информационным входам восьмог и девятого элементов И, блок деления, выход которого соединен с информационным аходом десятого элемента И, выход которого подключен к первому входу четвертого элемента ИЛИ, второй вход кото рого соединен с выходом одиннадцатого элемента И, выход четвертого элемента ИЛИ подключен по входу первого блока памяти, выход девятого элемента И сое,динен с первым аходом пятого элемента ИЛИ, .второй вход которого подключен к выходу двенадцатого элемента И, информационный аход которого соединен с первым выходом второго блока памяти и с информационным аходом шестого элеме.нта И, выход пятого элемента ИЛИ подключен к первому аходу второго блока памяти, второй выход которого соединен с информационными аходами четвертого и тринадцатого элементов И, второй аход второго блока памяти подключен к выходу шестого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами четыренадцатого и пятнадцатого элементов И, блок управления, вьгходы которого соединены с управляющими входами первого, второго, четвертого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, две- надцатого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадца- того, восемнадцатого, девятнадцатого и двадцатого элементов И, третьего элемента ИЛИ и с управляющими входами блоков умножения, деления, первого и второго блоков памяти и сумматора, бло ввода-вьюода, выход которого подключен к информационным аходам третьего, седь мого, одиннадцатого, пятнадцатого и шестнадцатого элементов И, а аход блока -ввода-вьгвода соединен с выходом три надцатого элемента И, дополнительно вве дены регистр, седьмой, восьмой- и девяты элементы ИЛИ, причем информационный аход семнадцатого элемента И соединен с вь1Х.одом сумматора и с информационным входом девятого элемента И, выход семнадцатого элемента И подключен К9 входу регистра, выход которого соединен с информационным входом восемнад цатрго элемента И, выход которого подключен к первому аходу седьмого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, ыход седьмого элемента ИЛИ подключен первому входу блока деления, выход которого соединен с информационным входом четырнадцатого элемента И, второй аход блока деления соединен с выходом восьмого элемента ИЛИ, первый и второй аходы которого подключены соответственно к выходам шестнадцатого и девятнадцатого элементов И, информационный аход девятнадцатого элемента. И подключен к выходу сумматора, инфор.мационный аход двадцатого элемента И соединен с первым выходом второго блока памяти, .выход двадцатого элемента И подключен к третьему в.ходу первого элемента ИЛИ, управляющий вход третьего элемента И подключен к выходу девятого элемента ИЛИ, входы которого соединены с выходом блока управления. На чертеже схематически представлено устройство, Оно содержит блок 1 управления, блок 2 ввода-вьюода, блок 3 умножения, сумматор 4, блок 5 деления, блоки 6 и 7 памяти, элементы 8-27 И, элементы 28-37 ИЛИ, регистр 38 управляющие аходы 39-67 соответствуюших блоков и элементов устройства. Устройство предназначено для решения разностных краевых задач вида A-,.. VO.V-) по рекурентному алгоритму с.-В. о i Acj-c -vNi A.p;.F. РиГс- Л А-. - ,Н- где AjjBj Cj F:- известные величины; Vj - искомое решение задачи; (Xj а. промежуточные коэффициУстройство работает следующим образом. Блок 2 ввода-вывода по сигналу блока 1 управления выставляет на вькодные шины значения BQ и Р.которы8 по сигналам . Х записьшаются в первые раз- 573 ряды регистров блоков 6 и 7 памяти соответственно (X j -управляющий сигнал, подаваемый на управляк щий вход с номе- ром I по чертежу устройства). Эти oneрации соответствуют формулам (2) рекуррентного алгоритма. Дал&е реализуются формулы (3) и (4). БЛОК 2 ввода-вывода выставляет на шину значение А , По сигналу Xgg на первый блока 3 умножения поступает с обратным знаком с. , а на второй нход блока 3 умножения по сигналу Xg2 подается А, По сигналу Х выполняется- умножение. Блок 2 ввода-вьшода вьгставляет на шину значение С, По сигналам и результат с выхода блока умножения подаются на аходы ;сумматора 4. Начинается циклический участок работы устройства. По сигналу Х производится суммирование. Блок 2 ввода-вьто да выставляет на выходные шины значения В и Р-, , Одновременно по сигналу происходит запись результата с выхода сумматора в запоминающий регистр 38, по сигналу Х выход сумматора подается на вход делителя блока 5 деления, Bj по сигналу Хд подается на вход делимого блока 5 деления, а на входы блока- 3 умножения по сигналам XgjH X подаются А и В-, , хранящееся в первых разрадах регистров второго блока 7 памяти. Далее одновременно по сигналам 53 48 4 выполняются соответственно умножение, деление и сдвиг вправо на один разряд в регистрах обоих блоков памяти. Затем блок 2 ввода-вывода выставляет на выходную шину величину F; . По сигналам произведение с выхода блока 3 умножения подаются на входы сумматора 4, Одновременно по сигналу X производится запись вычисленного дс, с выхода блока 5 деления в первые разряды регистров первого блока 6 памяти. Затем по сигналу Хд -«выполняется сложение. Блок 2 вводаг-вывода вьставляет на шину значение А ,. По сигналам Хез -) и с1 из первых разрядов первого блока 6 памяти подаются; на входы блока 3 умножения. По сигналу Х результат с выхода сумматора 4 подается на вход делимого блока 5 деления, а содержимое регистра 38 по сигналу подается на вход делителя блока 5 деления. Затем по сигналам Х и Х запускаются блоки умножения и деления. Блок 2 ввода-вььвода выставляет на шину значение С} 16 По сигналам произведение с выхода блока 3 умножения поступают на вход cyNO-taTOpa 4, вьиисленное выхода блока 5 деления по сих налу Хд записывается в первые разряды . регистров второго блока 7 памяти. Описанный циклический участок повторяется в течение Н тактов работы устройства. На М -м такте величины и Л равны нулю, в результате в регистрах первого и второго блоков памяти будут записаны коэффициенты d j и B-j , причем значения о1 и р,| будут записаны в (Ч , разрядах регистров, а значения и , храниться в первых разряда регистров памяти, На втором этапе работы устройства реализуются вычисления по формулам (5) и (6). Устройство управления вырабатывает одновременно сигналы Х, v 47 ° этим сигналам происходит сдвиг вп-ево в регистрах первого блока 6 памяти и циклический сдвиг влево в регистрах второго блока 7 памяти, В результате циклического сдвига первые разделы регистров второго блока 7 памяти, la которьк хранится By дут переписаны в освободившееся (Н +)-€ разр$щы ре- гистроБ второго блока 7 памяти. Далее устройство работает по циклическому алгоритму, реализующему формулу (6), По сигналу Х и Xg на входы блока 3 умножения подаются V, ., хранящееся в (Ы+1)-х разрядах регистров второго блока 7 памяти и ч-(раписанное в первых разрядах п-ервого блока 6 памяти. По сигналу Xg выполняется умножение. Затем по сигналу Xg и на входы сумматора 4 подаются л записанное в первых разрядах регистров второго блока 7 памяти, и произведение с выхода блока 3 умножения. По сигналу Xgg производится сложение, а по сигналам Xjj сдвиг |влево в регист pax обоих блоков памяти. По сигналу Х значение У с выхода сумматора записывается в ( N +1)-еразряды второго блока 7.памяти, В результате выполнения описанного алгоритма через И тактов в регистрах второго блока 7 памяти окажутся значения , Величина V будет записана в первых разрядах регистров, а величина V будет храниться в (Ч+1)-х разрядах регистров второгоблока 7 паМ5гги., ройства производится одновременной по. дачей (N +1)-го сдвигающего сигнала Хд на регистры второго блока 7 памяти и ( Н +1)-го управляющего сигнала Xgg на схему И 27, открывающую выход на щину блока 2 ввода-вывода. Поря док выдачи информации в этом случае: Vo/4 - NВьшод решения может производиться . также в процессе его получения путем подачи управляющего сигнала Х одновременно с сигналом . В этом случае решение будет выведено в порядке Н Значение УО будет вьщано по сигналу X,jQ , поданному вслед за пос ледним сигналом Хд . Благодаря наличию новых элементов и связей между ними достигается упрощение схемы устройства для.решения раз ностных краевых задач. Форму л- а изобретения Устройство для решения разностньк краевых задач, содержащее первый блок памяти, выход которого подключен к информационным входам первого и второго элементов И, вьгходы которьк соединены соответственно с первым и вторым входами- первого элемента ИЛИ, выход которого подключен к первому входу блока умножения, второй вход которого соедине с выходом второго элемента ИЛИ, первый и второй входы которого подключены к выходам третьего и четвертого элементов И, выход блока умножения соединен с информационным входом пятого элемен И, управляющий вход которого подключен к выходу третьего элемента И ЛИ, выход пято элемента И соединен с первым входом сум-матора, второй вход которого п 5аключен к вы ходу четвертого элемента ИЛИ, первый ,и второй входы которого соединены с вы ходами шестого и седьмого элементов И, вькод сумматора подключен к информационным входам восьмого и девя.того элементов И, блок деления, вьгход которого соединен с информационным BXO дом десятого элемента И, вьгход которого подключен к первому входу. четвертого элемента ИЛИ, второй вход которог соединен с выходомодиннадцетого элемента И; вьгход четвертого элемента ИЛИ -подключен ко входу первого блока памяти, вьгход девятого элемента И соединен с первым входом пятого элемента ИЛИ, второй вход которого подклюинформационньй аход которого соединен с первым выходом второго блока памяти и с информационным входом шестого элемента И, вьгход пятого элемента ИЛИ подключен к первому входу второго блока памяти, второй выход которого соединен с информационными входами четвертого и тринадцатого элементов И, второй входвторого блока памяти подключен к выходу шестого элемента ИЛИ, первый и второй входы которого соединены соответственно с вьгсодами четырнадцатого и пятнадцатого элементов И, блок управления, выходы которого соединены с управляющими входами первого, второго, четвертого, шестого, седьмого, восьмого, девятого, десятого, одиннадца- oro, двенадцатого, тринадцатого, четыг надцат ого, пятнадцатого, шестнадцатого, семнадцатого, восемнадцатого, девятнадцатого и двадцатого элементов И, третьего элемента ИЛИ и с управляюишми входами блоков умножения, деления, перво- го и второго блоков памяти и сумматора, блок ввода-вывода, выход которого подключен к информационным входам третьего, седьмого, одиннадцатого, пятнадцатого и шестнадцатого элементов И, а вход блока ввода-вьшода соединен с выходом тринадцатого элемента И, о тличающееся тем, что, с целью упрощения .устройства, в него введены регистр, седьмой, восьмой и девятый эле- менты ИЛИ, причем информационный вход семнадцатого элемента И соединен с вы-, ходом сумматора и с информационным входом девятого элемента И, вькод семнадцатого элемента И подключен ко вхоДУ регистра, вьгход которого соединен с информационным входом восемнадцатого элемента И, выход которого подключен к первому входу седьмого элемента ИЛИ второй вход которого соединен с выходом восьмого элемента И, выход седьмого -. « элемента ИЛИ подключен к первому входу блока деления, вьгход которого соединен с информационным входом четырнадцато о элемента И, второй вход блока соединен с вьгеодом восьмого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам шестнадцатого и девятнадцатого элементов И, инфор 1ационный вход девятнадцатого элемента И подключен к выходу сумматора, информационный вход двадцатого элемента И соединен с перiBbiM вькодом второго блока памяти, выход двадцатого элемента И подключен к третьему входу первого элемента ИЛИ, управляющий вход третьего элемента И подключен к выходу девятого элемента ИЛИ, вхо ды которого соединены с выходом бло ка управления. 110 Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР NO 209030, кл. Q 06 F 15/32, 1968. Авторское свидетельство СССР по заявке № 249039О/18-24, кл. Q 06 F 15/34, 1977 (нрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1280613A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

Авторы

Даты

1980-05-05—Публикация

1977-10-17—Подача