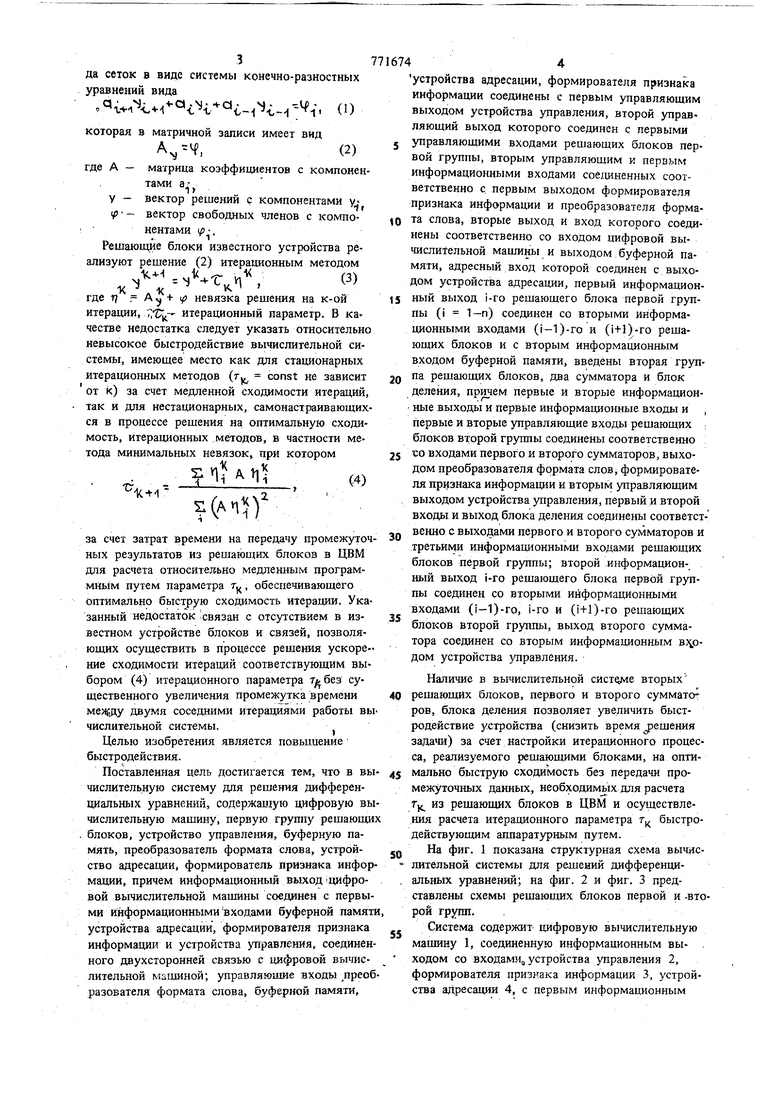

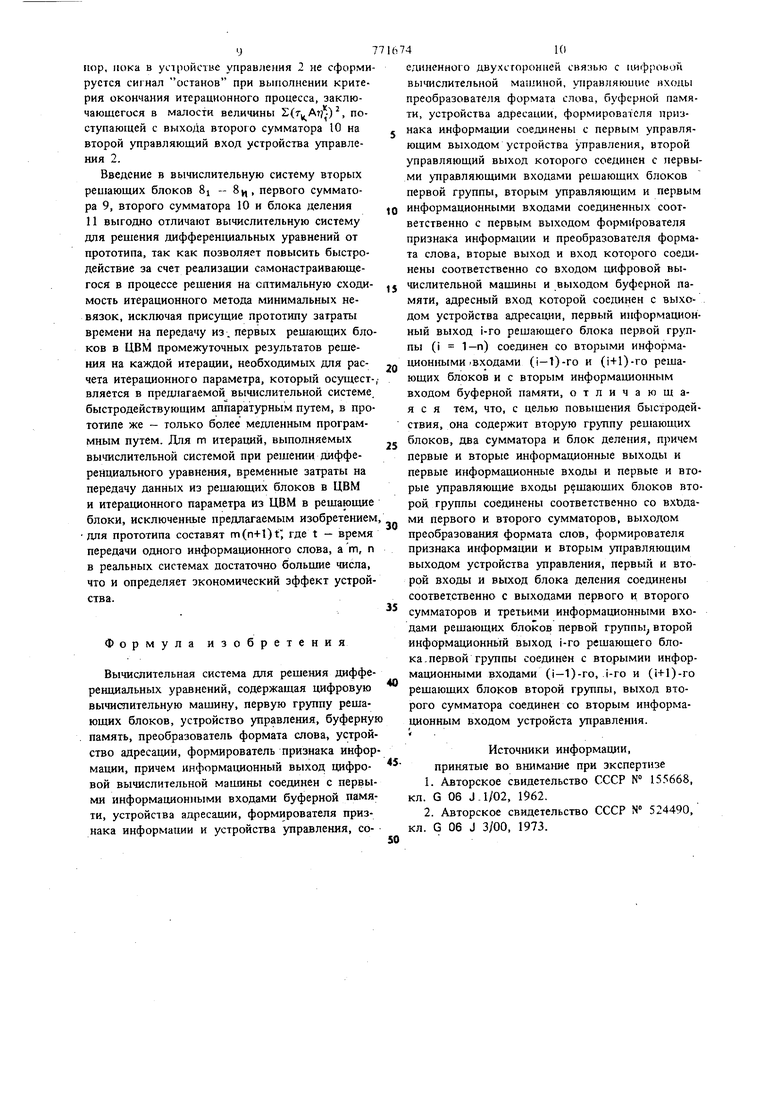

. 1 изобретение относится к области вычислитель ной техники и может быть использовано при решении дифференциальных уравнений в частных производных. Известна комбинированная вычислительная машина, в состав которой входят два арифмеАческих блока, соединенных обшим оперативным запоминающим устройством, причем один из блоков выполнен интегрирующим 1 . Недостатком такого устройства является относительно невысокое быстродействие, обусловленное тем, что оба вычислительных блока име к)т последовательную структуру. Из известных устройств наиболее близким по техническому решению-является комбинированная вычислительная система 2, содержащая ЦВМ общего назначения, информационный выход которой через блок буферной памяти, первый преобразователь, блок коммутаторов соединен со входами первых решающих блоков, подключенных информационными входами и выходами между собой, управляющими входами и выходами к устройству управления, ин формационными выходами через блок буфер- . НОЙ памяти и второй преобразователь - ко входу ЦВМ, информационный выход которой соединен также со счетчиком адреса буферной liaмяти, регистром адреса граничных решающих блоков, регистром признака информации и блоком местного управления, имеющего двухстороннюю связь с ЦВМ и устройством управления и подключенного выходом к управляющему входу регистра, признака информации, соединенного с дешифратором признака информации, подключенным ко входу блока коммутаторов, к управляющему входу регистра адреса граничных рещающих блоков, соединенного с дешифратором адреса граничных решающих блоков, подключенным к адресным входам решающих блоков, к управляющему входу счетчика адреса буферной памяти, соединенйому с дешифратором адреса буферной памяти, подключенным ко входу блока буферной памяти, к управляющему входу блока коммутаторов и к управляющему входу блока буферной памяти. Известное устройство предназначено для решения дифференДиальнь х уравнений в частных производных, представленных с помощью метода сеток в виде системы конечно-разностных уравнений вида ,а{,).Ч- аг-1 -{,нЛ (1) которая в матричной записи имеет вид ,(2) где А - матрица коэффициентов с компонентами 3;У - вектор решений с компонентами уVJ-- вектор свободных членов с компо нентами f-.. Решающие блоки известного устройства реализуют решение (2) итераш онным методом ,, где 77 . А. + i;) невязка решения на к-ой итерации, -TfC итерационный параметр. В качестве недостатка следует указать относительно невысокое быстродействие вычислительной системы, имеюшее место как для стационарных итерационных методов (j const не зависит от к) за счет медленной сходимости итераций, так и для нестационарных, самонастраивающихся в процессе решения на оптимальную сходимость, итерационных методов, в частности метода минимальных невязок, при котором (4) tl(An i за счет затрат времени на передачу промежуточ ных результатов из решаюи их блоков в ЦВМ для расчета относительно медленным программным путем параметра Тц, обеспечивающего оптимально быструю сходимость итерации. Ука занный недостаток связан с отсутствием в известном устройстве блоков и связей, позволяющих осуществить в процессе решения ускорение сходимости итераций соответствующим выбором (4) итерационного параметра т;-без существенного увеличения промежутка времени Meatfly двумя соседними итерациями работы вы числительной системы. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в вы числительную систему для решения дифференциальных уравнений, содержащую цифровую вы числительную машину, первую группу решающи . блоков, устройство управлеьшя, буферную память, преобразователь формата слова, устройство адресации, формирователь признака инфор мации, причем информационный выход |цифровой вычислительной машины соединен с первы ми информационнымивходами буферной памя устройства адресации, формирователя признака информации и устройства управления, соединен ного двухсторонней связью с цифровой вычислительной машиной; управляющие входы ,прео разователя формата слова, буферной памяти. устройства адресации, формирователя признака информации соединены с первым управляющим выходом устройства управления, второй управляющий выход которого соединен с первыми управляющими входами решающих блоков первой группы, вторым управляющим к первым информационными входами соединенных соответственно с первым выходом формирователя признака информации и преобразователя формата слова, вторые выход и вход которого соединены соответственно со входом цифровой вычислительной машины и выходом буферной памяти, адресный вход которой соединен с выходом устройства адресации, первый информационный выход i-ro решающего блока первой группы (i Т-п) соединен со вторыми информационными входами (i-1)-го и (i+l)-ro рещающих блоков и с вторым информационным входом буферной памяти, введены вторая группа решающих блоков, два сумматора и блок деления, причем первые и вторые информационные выходы и первые информационные входы и , первые и вторые управляющие входы решающих : блоков второй группы соединены соответственно СО входами первого и второго сумматоров, выходом преобразователя формата слов, формирователя признака информации и вторым управляющим выходом устройства зшравления, первый и второй входы и выход блока деления соединены соответствеяно с выходами первого и второго сумматоров и третьими информащюнными входами решающих блоков первой группы; второй информационный выход i-ro решающего блока первой группы соединен со вторыми ийформационными входами (i-1)-го, i-ro и (i+l)-ro решающих блоков второй группы, выход второго сумматора соединен со вторым информационным в одом устройства управления. Наличие в вычислительной систу е вторых рещающйх блоков, первого и второго сумматор ров, блока деления позволяет увеличить быстродействие устройства (снизить время решения задачи) за счет настройки итерационного процесса, реализуемого решающими блоками, на оптимально быструю сходимость без передачи промежуточных данных, необходимых для расчета Гц из решающих блоков в ЦВМ и осуществления расчета итерационного параметра г, быстродействующим аппаратурным путем. На фиг. 1 показана структурная схема вычислительной системы для решений дифференциальных уравнений; на фиг. 2 и фиг. 3 представлены схемы решающих блоков первой и -второй групп. . Система содержит Щ1фровую вычислительную машину 1, соединенную информационным вы- . ходом со входами устройства управления 2, формирователя признака информации 3, устройства адресаш1И 4, с первым информационным

входом буферной памяти 5, адресный вход которой подключен к выходу устройства адреса1даи 4, а управляющий вход, а также управляющие входы преобразователя формата слова 6, устройства адресадии 4 и формирователя признака информации 3 подключены к выходу устройства управления 2, соединенного первыми управляющими входом и выходом с ЦВМ 1, вторьЕми управляющими входом и выходом - с первыми управляющими входом и выходом устройства управления 2, подключенного вторым управляющим выходом к первым управляющим входам рещающих блоков 7i - 7j первой группы и рещающих блоков Sj - 8 у, второй группы, соединенных вирыми управляющиг лш входами с выходом формирователя признака информации 3 и подключенных первыми (блоки 7i - 7, и блоки 8i - 8,) информационными входами;ко второму выходу преоб- , разователя 6, соединенного первым выходом с ЦВМ 1, и информационным входом - с выходом буферной памяти 5. Рещающие блоки - 1у( подключены между собой вторыми информационными входами и первыми информационными выходами, соединенными также со вторым информационным входом буферной памяти 5. Каждый i-ый рещающий блок 8 соединен первыми информационными входами со вторым информационным выходом каждого i-ro и подключенных к i-му рещающих блоков 7-, .. л. подключен первым и вторым информационным выходом ко входу первого 9 и второго 0 сумматора, соединенного выходом со вторым управляющим входом устройства управления 2 и с первым входом блока деления 11, подключенного вторым входом к выходу первого сумматора 9, а выходом - к третьим информационным входам первых рещающих блоков 7i - 7ц .

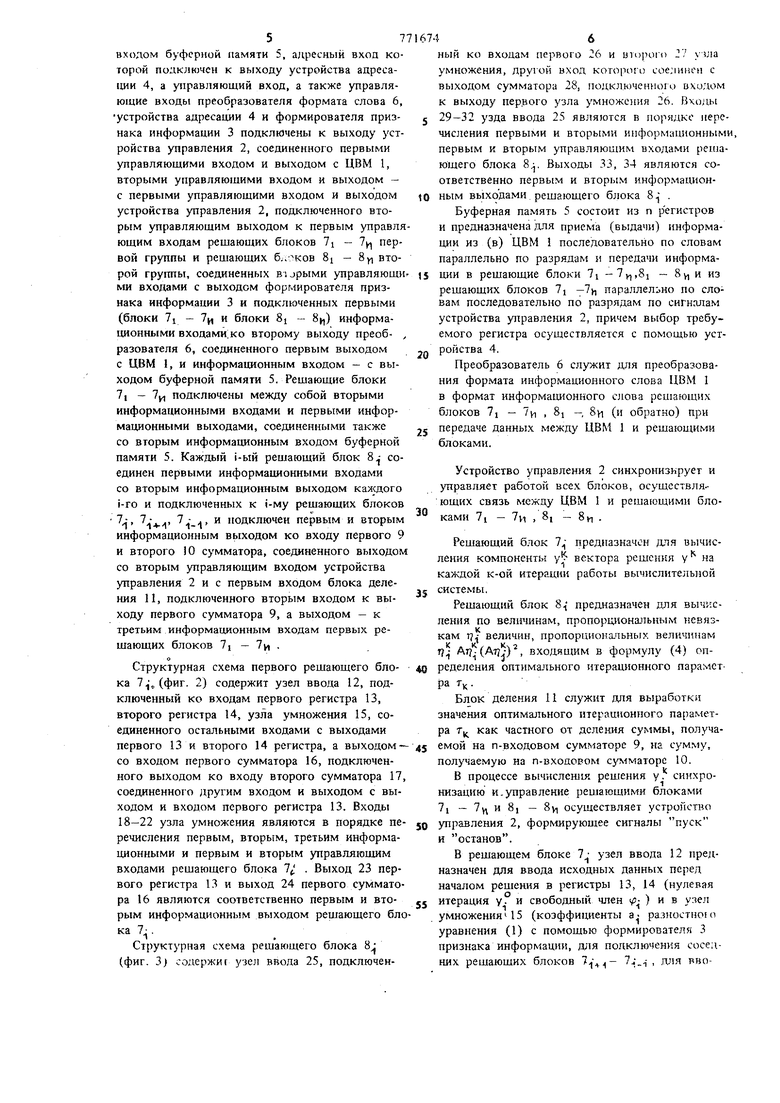

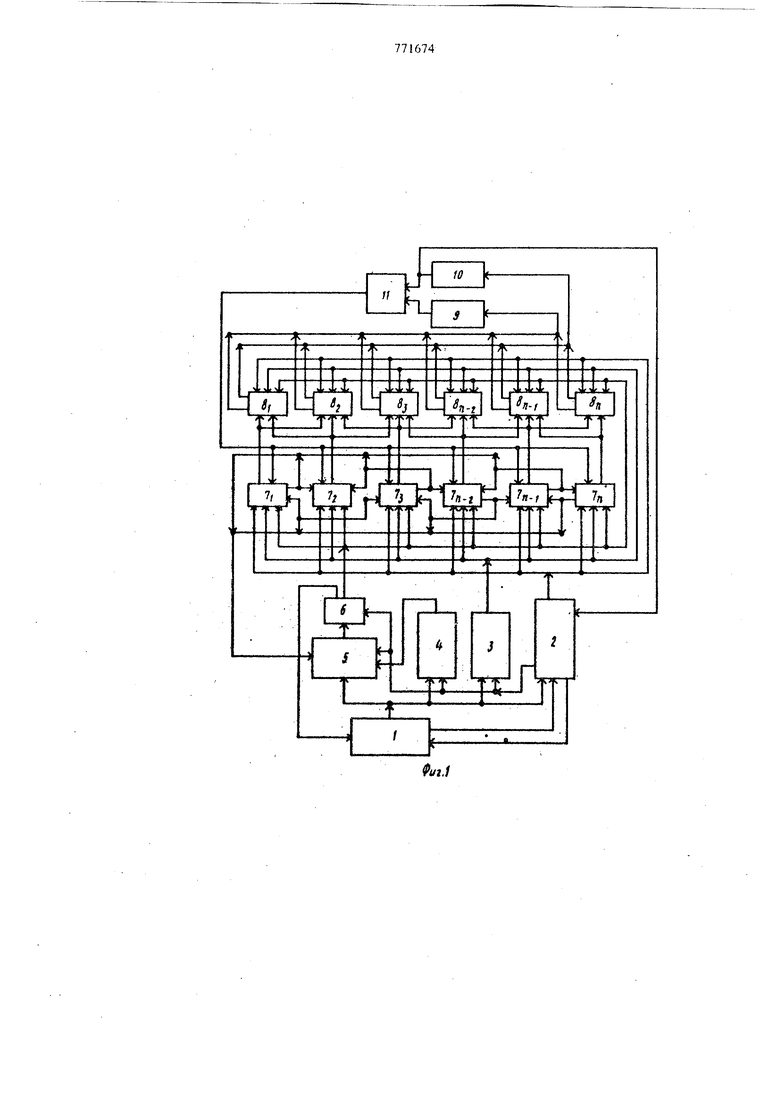

Структурная схема первого решающего блока 7 Дфиг. 2) содержит узел ввода 12, подключенный ко входам первого регистра 13, второго регистра 14, узла умножения 15, соединенного остальными входами с выходами первого 13 и второго 14 регистра, а выходом - со входом первого сумматора 16, подключенного выходом ко входу второго сумматора 17, соединенного другим входом и выходом с выходом и входом первого регистра 13. Входы 18-22 узла умножения являются в порядке перечисления первым, вторым, третьим информационными и первым и вторым управляющим входами рещающего блока 1 . Выход 23 первого регистра 13 и выход 24 первого сумматора 16 являются соответственно первым и вторым информационным выходом рещающего блока 7.

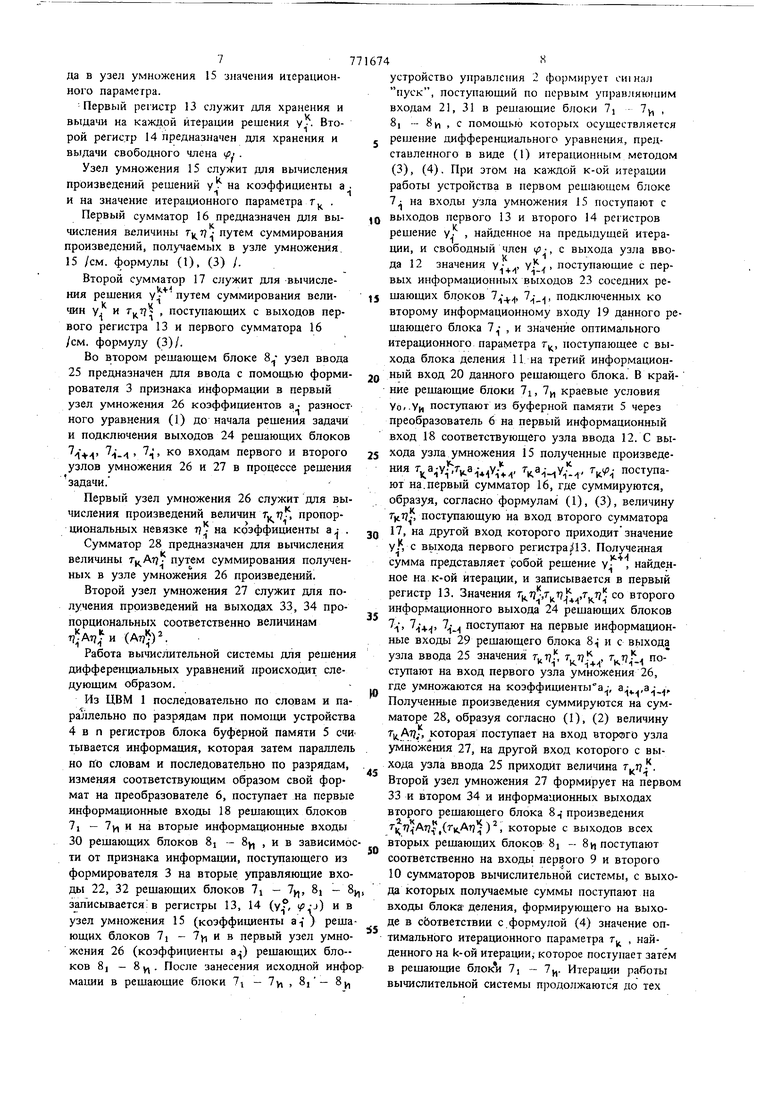

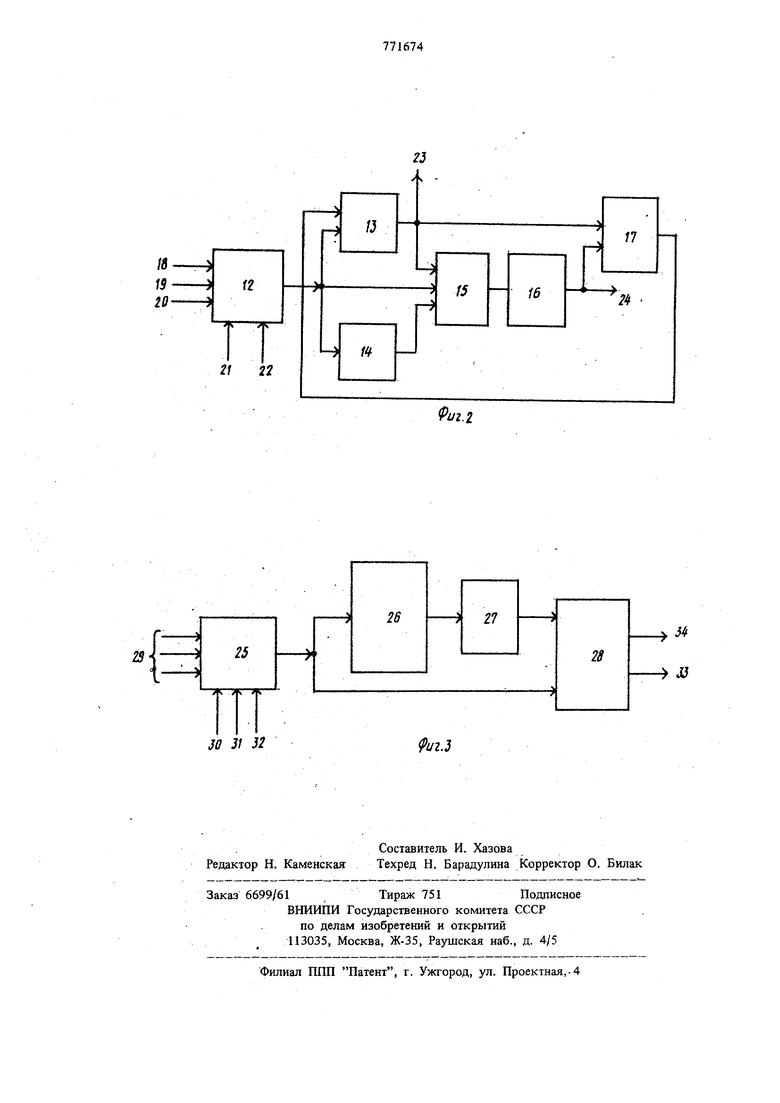

Структурная схема решающего блока 8 (фиг. 3} содержи г уэел ввода 25, подключенный ко входам первога 26 и июрого 27 улпа умножения, другой вход которого соелине с выходом сумматора 28, подкл.мченного входом к выходу первого узла умножения 26. Входы 29-32 узда ввода 25 являются в порядке перечисления первыми и вторыми информационными, первым и вторым управляющим входами решающего блока 8.. Выходы 33, 34 являются соответственно первь М и вторым информационным выходами рещающего блока 8.J .

Буферная память 5 состоит из п регистров и предназначена для приема (выдачи) информации из (в) ЦВМ 1 последовательно по словам параллельно по разрядам я передачи информа11ЛИ в рещающие блоки 7i - 7y,,8i - 8у, и из рещающих блоков 7i -7), параллельно по словам последовательно по разрядам по сигналам устройства управления 2, причем выбор требуемого регистра осуществляется с помощью устройства 4,

Преобразователь 6 служит для преобразования формата информационного слова ЦВМ 1 в формат информационного слова решающих блоков 7i - 7vi , 81 -, Svi (и обратно) при передаче данных между ЦВМ 1 и рещающими блоками.

Устройство управления 2 синхронизирует и управляет работой всех блоков, осуществляющих связь между ЦВМ 1 и решающими блоками 7i - 7и ,8, - 8 .

Решающий блок предназначен для вычисления компоненты у вектора решения у на каждой к-ой итерации работы вычислительной

системы,

Решающий блок 8.( предназначен для вычисления по величинам, пропорщюнальным невязкам 771 величин, пропорциональных величинам Ат (Ат) , входящим в формулу (4) определения оптимального итерационного параметра т.

Блок деления И служит для вьфаботкя значения оптимального итерационного параметра т как частного от деления суммы, получаемой на п-входовом сумматоре 9, на сумму, получаемую на п-входовом с тмматоре 10.

В процессе вычисления решения у. синхронизацию и.управление решающими блоками 7i - 7yjn8j - BVI осуществляет устройство

управления 2, форлиирующее сигналы пуск и останов.

В решающем блоке узел ввода 12 предназначен для ввода исходных данных перед началом решения в регистры 13, 14 (нулевая

итерация уР и свободный член ) и в узел умножения 15 (козффи1щенты а разностно о уравнения (1) с помощью формирователя 3 признака информации, для подключения сосецних рещающих блоков - 7 , для пвода в узел умножения 15 значе}1ия итерационного параметра. Первый регистр 13 служит для хранения и выдачи на каждой итерации решения у v. Второй регистр 14 предназначен для хранения и выдачи свободного члена Узел умножения 15 служит для вычисления произведений решений у . на коэффициенты а . и на значение итерационного параметра гj . Первый сумматор 16 предназначен для вычисления величины путем суммирования произведений, получаемых в узле умножения. 15 /см. формулы (1), (3) /. Второй сумматор 17 служит для вычислеКИЯ решения у. путем суммирования величин у. и , поступающих с выходов первого регистра 13 и первого сумматора 16 /см. формулу (3)/. Во втором решающем блоке узел ввода 25 предназначен для ввода с помощью формирователя 3 признака информации в первый узел умножения 26 коэффициентов а разностного уравнения (1) до начала решения задачи и подключения выходов 24 решающих блоков 7у{, , 7,, ко входам первого и второго узлов умножения 26 и 27 в процессе решения задачи. Первый узел умножения 26 служит для вычисления произведений величин , пропорциональных невязке т на коэффициенты . Сумматор 28 предназначен для вычисления величины т(A.r) путем суммирования полученных в узле умножения 26 произведений. Второй узел умножения 27 служит для получения произведений на выходах 33, 34 пропорциональных соответственно величинам п1|Аг |и () Работа вычислительной системы для решени дифференциальных уравнений происходит; следующим образом. Из ЦВМ 1 последовательно по словам и параллельно по разрядам при помощи устройств 4 в п регистров блока буферной памяти 5 счи тывается информация, которая затем параллел но словам и последовательно по разрядам, изменяя соответствующим образом свой формат на преобразователе 6, поступает на первы информационные входы 18 решающих блоков 7i - 7ц и на вторые информационные входы 30 решающих блоков Sj - 8у, , и в зависимо ти от признака информации, поступающего из формирователя 3 на вторые управляющие вхо ды 22, 32 решающих блоков 7i - 7у, Sj - записывается в регистры 13, 14 (у, ip-j) и в узел умножения 15 (коэффициенты a-f ) реш ющих блоков 7i - и в первый узел умно жения 26 (коэффи1щенты а) решающих блоков 8, - By,. После занесения исходной инф маиии в решающие блоки 7i - 7у, , 81 - 8, 7 « устройство управления 2 с юрмнрует си| нал пуск, поступающий по первым управлян)1иим входам 21, 31 в решающие блоки 7j - 7у, , 8 - 8ц , с помощью которых осуществляется решение дифференциального уравнения, представленного в виде (1) итерационным методом (3), (4). При этом на каждой к-ой итерации работы устройства в первом решающем блоке 7 на входы узла умножения 15 поступают с выходов первого 13 и второго 14 регистров решение у , найденное на предыдущей итерации, и свободный член , с выхода узла ввода 12 значения У., поступающие с первых информационных выходов 23 соседних решающих блоков -f--| подключенных ко второму информационному входу 19 д.анного решающего блока , и значение оптимального итерационного параметра Г(, поступающее с выхода блока деления И на третий информационный вход 20 данного решающего блока. В крайние репиющие блоки 7i, 7, краевые условия УО..УИ поступают из буферной памяти 5 через преобразователь 6 на первый информационный вход 18 соответствующего узла ввода 12. С выхода узла умножения 15 полученные произведения , ,., поступают на.первый сумматор 16, где суммируются, образуя, согласно формулам (1), (3), величину к IK , поступающую на вход второго сумматора 17, на другой вход которого приходит значение у., с вь1хода первого регистра(13. Полученная сумма представляет собой решение у, найденное на к-ой итерации, и записывается в первый регистр 13. Значения со второго информационного выхода 24 решающих блоков , VH поступают на первые информационные входы 29 решающего блока 8:, и с вь1хода узла ввода 25 значения , т i , . поступают на вход первого узла умножения 26, где умножаются на коэффициенты а а.,. Полученные произведения суммируются на сумматоре 28, образуя согласно (1), (2) величину , которая поступает на вход вторхэго узла умножения 27, на другой вход которого с выхода узла ввода 25 приходит величина .. Второй узел умножения 27 формирует на первом 33 и втором 34 и информационных выходах второго решающего блока 8 произведения ,{Гк.), которые с выходов всех вторых решающих блоков 8| - 8ц поступают соответственно на входы первого 9 и второго 1 лЧ 10 сумматоров вычислительной системы, с выхода которых получаемые суммы поступают на входы блока деления, формирующего на выходе в сЬответствии с.формулой (4) значение оптимального итерационного параметра т , найденного на k-ой итерации, которое поступает затем в решающие 7 - 7. Итерации работы вычислительной системы продолжаются до тех у пор, пока в устройстве управления 2 не сформи руется сигнал останов при выполнении критерия окончания итерационного процесса, заключающегося в малости величины () , поступающей с выхода второго сумматора 10 на второй управляющий вход устройства управления 2. Введение в вычислительную систему вторых решающих блоков Sj --8ц, первого сумматора 9, второго сумматора 10 и блока деления 11 выгодно отличают вычислительную систему для рещения дифференциальных уравнений от прототипа, так как позволяет повысить быстродействие за счет реализации самонастраивающегося в процессе решения на оптимальную сходимость итерационного метода минимальных невязок, исключая присущие прототипу затраты времени на передачу из. первых решающих бло ков в ЦВМ промежуточных результатов ращения на каждой итерации, необходимых для расчета итерационного параметра, который осуществляется в предлагаемой вычислительной системе быстродействующим аппаратурным путем, в прототипе же - только более медленным программным путем. Для m итераций, выполняемых вычислительной системой при решении дифференциального уравнения, временные затраты на передачу данных из решающих блоков в ЦВМ и итерационного параметра из ЦВМ в решающие блоки, исключенные предлагаемым изобретением для прототипа составят m(n-H)t, где t - время передачи одного информационного слова, а т, п в реальных системах достаточно больщие числа, что и определяет экономический зффект устройства. Формула изобретения Вычислительная система для решения дифференциальных уравнений, содержащая цифровую вычислительную машину, первую группу решающих блоков, устройство управления, буферну память, преобразователь формата слова, устройство адресации, формирователь признака инфор мации, причем информационный выход цифровой вычислительной машины соединен с первыми информационными входами буферной памяти, устройства адресации, формирователя признака информации и устройства управления, со410единенного двухсторонней свянью с цифровой вычислительной машиной, управляющие входы преобразователя формата слова, буферной памяти, устройства адресации, формирователя признака информации соединены с первым управляющим выходом устройства управления, второй управляющий выход которого соединен с первыми управляющими входами решающих блоков первой группы, вторым управляющим и первым информационными входами соединенных соответственно с первым выходом форм1 рователя признака информации и преобразователя формата слова, вторые выход и вход которого соединены соответственно со входом цифровой вычислительной машины и выходом буферной памяти, адресный вход которой соединен с выходом устройства адресац11и, первый информационный выход i-ro решающего блока первой группы (i 1-п) соединен со вторыми информационными )ВХ одами (-Т)-го и (i-H)-ro решающих блоков и с вторым информационным входом буферной памяти, отличающаяся тем, что, с целью повыше(шя быстродействия, она содержит вторую группу решающих блоков, два сумматора и блок деления, причем первые и вторые информационные выходы и первые информационные входы и первые и вторые управляющие входы рещаюших блоков второй группы соединены соответственно со входами первого и второго сумматоров, выходом преобразования формата слов, формирователя признака информации и вторым управляющим выходом устройства управления, первый и второй входы и выход блока деления соединены соответственно с выходами первого и второго сумматоров и третьими информационными входами решающих блоков первой гpyппь второй информационный выход i-ro решающего блока, первой группы соед1шен с вторымии информационными входами (i-1)-го, .i-ro и (i+l)-ro решающих блоков второй группы, выход второго сумматора соединен со вторым информационным входом устройста управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 155668, кл. G 06 J Л/02, 1962. 2.Авторское свидетельство СССР № 524490, кл. G 06 J 3/00, 1973.

/fl/520

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинированная вычислительная система | 1977 |

|

SU670942A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Вычислительное устройство для поворота вектора | 1979 |

|

SU857979A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

25

25

30 J/ 32

иг.2

Авторы

Даты

1980-10-15—Публикация

1978-06-19—Подача