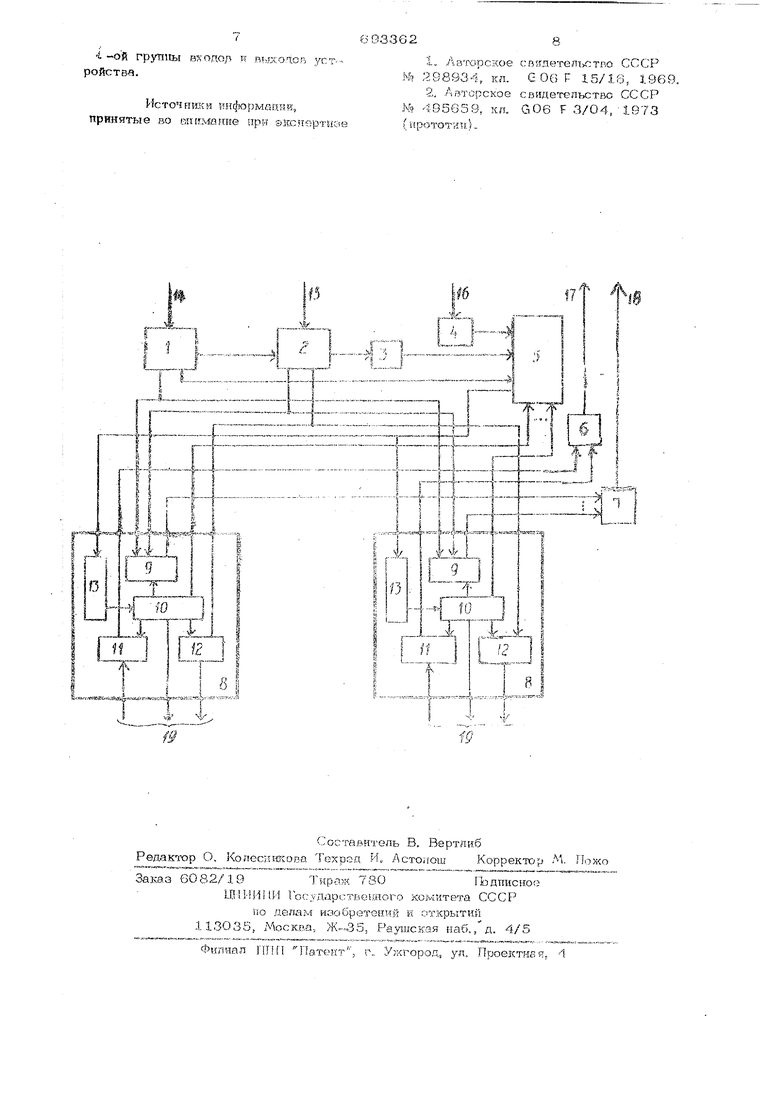

которые хранятся в оперативной памяти мультиплексного канала (ОПМК). УСК содержит адрес памяти центрального процессора и информацию, необходимую для выполнения операции ввода-вывода. Каждому внешнему устройству соответствует свое УСК. При-ус танов леднв свя эя с данным внешнем устройством его yCk извлекается нэ ОПМК в ганоси я в общий регистр УСК, с которого вейется управление обменом. После передачи информации УСК для данного абонента .передается обратно в ОПМК на хранение На передачу УСК яз ОПМК в регистр УСК и обратно затрачивается несколько машинньгх тавлхэв, что увеличивает время на установление связи с внешним устройством. Кроме того, данное устройство для связи процессора с устройствами ввода-вывода в каждый момент времени обменивается информацией только с одним внешним устройством, что исключает возможность ойяовременной работь нескольких быстродейств5гго1ЦИх внешних устройств. Таким образом, недостаток этого устройства состоит в малой пропускной способности. Целью изобретения является повышение пропускной способности устройства Поставленная цель достигается тем, что в устройство введены подканальт по числу устройств ввода-вывода, каждый из которых содержит регистр управляющих слов, соединен41ый первым входом с первым выходом формирователя yпpaвлян ших сигналов, второй и третий выходы которого подключены соответственно KD входу регистра записи и первому входу регистра чтения, и управляемый счетчик машинных тактов, выходом подключенны ко входу формирователя управляющих сигналов, причем, третий выход блока обработки инструкций процессора и второй выход регистра связи подключены соотвественно ко второму и треттэему входу регистров управляющих слов, выходы которых соединены с соответствую шими входами блока выдачи данных, чет вертые выходы формирователей управляк щих сигналов подканалов подключены к соответствуюшим входам из группы входов блока анализа приоритетов, выход КОТОРОГО подключен ко входам управляемых счетчиков машиншлх тактов, выходы регистров записи подключены к соответс-п уютим входам блока выдачи адреса, третий выход регистра связи с процессором соединен со вторыми вхоай МИ регистров чтения подканалов, второй вход регистра записи, пятый вход фбрми- рователя управляюших сигналов и выход регистра чтения i -го подканала являются входом и выходом 1--ОЙ группы входов и выходов устройства. На чертеже приведена блок-схема устройства, содержащая блок 1 обработки инструкций, регистр 2 связи с процессором, регистр 3 маски, регистр 4 запросов, блок 5 анализа приоритетов, блок 6 выдачи адреса, блок 7 выдачи данных, подканал 8, включакпний ретнстр 9 управляющих слов, формирователь Ю управляк)щих сигналов, регистр 11 записи, регистр 12 чтения и .управляемый счетчик 13 машинных тактов, первый 14, второй 15 и третий 16 входы устройства, адресный 17 и информационный 18 выхогш устройства и группу 19 входов и выходов устройства для подключения устройства ввода-вывода. Устройство работает следующим образом. В блок I по входу 14 поступает инструкция - прием управляющего слова из процессора с кодом номера устройства ввода-вывода (ЙУ). С выхода блока 1 сигнал првема управляющего слова поступает в регистр 2, а сигнал, представляющий собой дешифрованный номер ВУ - в регистр 9 соответствующего подканала 8. По сигналам блока I управляющее слово для одного подканала поступает через вход 15 в регистр 2, а затем в регистр 9 соответствующего подканала. Во время передачи управляющего слова из процессора в устройство работа блока 5 блокируется сигналом из блока 1.. Реализация запросов устройств ввода-вывода на обмен информацией осуществляется в такрй последовательности. Запросы устройства ввода-вывода на обмен данными поступают на вход 16 и регистр 4, связанный с блоком 5. 1)и наличии управляющего слова для данного абонента, иниц1труемого сигналом, поступающим на соответствующий вход блока 5 на формирователя 1О, и отсутствии сигнала мжки запроса в регис:тре 3, запрос анализируется блоком 5. В итоге анализа блок 5 выдает ста{1щий но приоритету запр&с, который поступает в соответствующий подканал 8. 5Г Зяпрос ип блокп 5 1юступяет в полканал 8 нп упрявлякппий счетчик 13 мшпиишлх тпктой и ;-«1тускпот его. Тактовые импульсы счетчико постугтют на формирователь 10, который управляет рп(ботой Подканала Я. Работа в режиме чтения ип пямяти в ycTpoHCTfjo вводя-пмвода ироилкоиктся следующим образом. Запрос от абонента через блок 5 аапупкает управляющий счетчик 13. С формирователя 10 п регистр 9 выдается сигнал, рапрешающий регистру управляющего слова выдачу адреса памяти центрального вычислителя на вход блока 6 адреса, от которого адрес поступает на выход 17 в процессор. Последний, получив адрес, выбирает из памяти информацию и выставляет ее иа вход 15, откуда она поступает в регистр 2. Формирователь Ю выдает в регистр 12 разрешение на прием информации. Информация из регистра 2 заносится в регистр 12. Затем по выходам 19 выдается в соответствун5щее устройство ввода-вывода информация из ре- гистра 12 и формирователя 1О. При записи в процессор устройство ввода-вывода выставляет информацию на вход 19 которая при наличии разрешающего сигнала от блока формирователя 10 записывается в регистр 11 записи. Формирователь 1О выдает в регистр 9 управляющего слова сигнал, разрешающий выдачу адреса памяти центрального вычислителя в блок 6 и далее по выходу 17 в процессор. Выдача информации из регистра 11 осуществляется через блок 7 выдачи данных. Блок индикаторов осуществляет объединение сигналов возбуждения устройств ввода-вывода, анализ их состояния и передачу их в процессор. Каждое из устройств ввода-вывода имеет непосредственный доступ к подканалу, где в регистре 9 хранится управляющее слово, а в регистрах буферируется. информация. Наличие в подканалах управляющих счетчиков 13 машинных тактов позволяет выполнять параллельную и независимую обработку запро сов от нескольких устройств ввода-вывода. Таким образом устройство обеспечив параллельный обмен информацией между процессором и несколькими устройствам l fюДfl выmJПД, что iipWfjonHT к повышенвю пропускпой f;nof-o6ffocTR устройства. Формула изобретения Уст{юйстио лпя сопряжения процессора с уптройствами ввода-вывода, содержашее блок 1 обработки инструкций процессоря, соединенный первым выходом с первым входом регистра связи с процессором, первый выход котоорго через регистр масок подключен к первому входу блока анализа приоритетов, второй и третий входы которого подключены соответственно к выходу регистра запросов, и второму выходу блока обработки инструкций процессора, входы которых и второй вход регистра связи с процессором являются соответствующими входами устройства, блок выдачи адреса в блок выдачи данных, выходы, которых являются соответственно адресным и информационным выходами устройства, отличающееся тем, что, с целью повышения пропускной способности устройства, в него введены подканалы по числу устройств вводавывода, каждый из которых содержит регистр управляющих слов, соединенный первым входом с первым выходом формирователя управляющих сигналов, второй и третий выходы которого Подключены соответственно ко входу регистра записи и первому входу регистра чтения, и управляеквый счетчик машинных тактов, выходом подключенный ко входу формирователя управляющих сигналов, причем третий выход блока обработки инструкций процессора и второй выход регистра связи подключены соответственно ко второму и третьему входу регистров управляющих слов, выходы которых соединены с соответствующими входами блока выдачи данных, четвертые выходы формирователей управляющих сигналов всех подканалов подключены к соответствующим входам из группы входов блока анализа приоритетов, выход которого подключен ко входам управляемых счетчиков машинных тактов выходы регистров записиподключены к , соответствующим входим блока выдачи адреса, третий выход регистра связи с npdneccopoM соединен со вторыми входами регистров чтения подканалов, второй вход регистра записи, пятый выход формирователя управляющих сигналбв и вьЬсод регистра чтения (-го подканала являются входом и выходом

-t -ой группы входо; и выходов устройства.

Источники информации, принятые во внимание тфи экспертизе

свидетельство СССР

G06 F 15/16, 1969.

свидетельство СССР GO6 F 3/04, 1973

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для управления обменом | 1988 |

|

SU1667086A1 |

| Устройство ввода-вывода | 1976 |

|

SU781803A1 |

| Устройство для сопряжения | 1978 |

|

SU736086A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Мультиплексный канал | 1979 |

|

SU860048A1 |

Авторы

Даты

1979-10-25—Публикация

1977-06-10—Подача