(54) УСТРОЙСТВО ВВОДА-ВЫВОДА 1 .. .. .Изобретение относится к вычислительной технике и может быть исполь зовано при конструировании селекторных каналов ввода-вывода. Каналы осуществляют обмен данньрс с внешними устройствами. Пе15едача данных между внешними устройствами и каналом выполняется параллельными кодами, которые далее называются бай тами и содержат в типичном случае 8 двоичных разрядов. В операции чтения канал принимает данные из внешне го устройства по входным информацион ньм шинам интерфейса и из полученных байтов формирует единицу информации, пригодную для записи в оперативную пгмять и называемую далее словом.Раз мер слова определяется разрядностью оперативной памяти и обычно сОставля ет 2,4 или 8 байтов. После фЬрмирова ния каждого очередного слова кангш посылает в процессор запрос на передачу этого слова в оперативную память. В операции записи канал формирует запросы на считывание слов из оперативной памяти и побайтно передает эти слова во внешнее устройство по выходным информационным шинам интерфейса. Канал содержит также средства, позволягогцие распознать условия

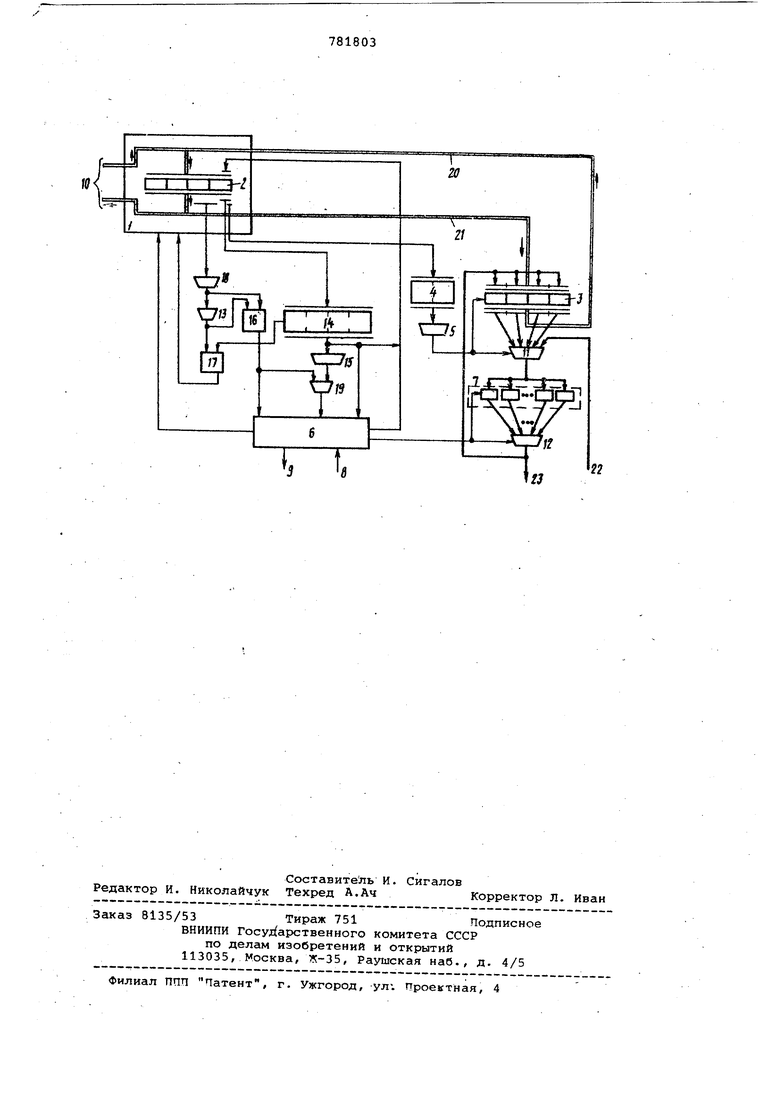

Г окончания передачи данных и сообщить об этом процессору и внешнему устройству. Процессор осуществляет иннциироваиие операций ввода-вывода, передачу данных между каналами и оперативной пшлятью. Известно устройство для ввода-вывода, содержащее главный канал, в состав которого входит информационный регистр, соединенный по входу и выходу с сумматором, блоком местной памяти, информационной магистралью оперативной памяти и регистрами данных подканалов содержгицих счетчик номерй байта с дешифратором, выход которого подключен к управлякадему входу регистра данных, и узел управления, первый выход которого соединен со входам блока управления главного канала l. Недостаток этого устройства низкая скорость передачи массивов, связанных цепочкой данных. Этот недостаток обусловлен тем, что расположение байта данных в буферном регистре подканала определяется позицией этого байта в слове. Указанный недостаток существенно снижает быстродействие канала при передаче массивов с использованием цепочек данных. пусть, к примеру, требуется прочитать зону с магнитной ленты, причем этот массив надо записать в две п смежные области оперативной памяти. Программа канала в этом случае состоит из двух управляющих слов, связанных цепочкой данных. Первое управляющее слово содержит начальный адрес первой области оперативной памяти и число байтов, которое в эту область надо поместить, второе управляющее слово содержит аналогичную информацию о второй облас ти памяти. Передача данных начинается с использованием информации в первом управляющем слове. Как только принят последний байт из числа относящихся к первой области памяти,обмен с внешним устройством временно приостанавливается, так как подканал не знает, в какое место поместить следукяйий байт данных. Обмен возобновляет.ся лишь после выполнения всех действий, связанных с переходом по цепочк данных (записи последнего слова данных в первую область оперативной памяти, считывания из оперативной памя ти и размещения из местной памяти второго управляющего слова, заполнения счётчика и регистра информацией из второго управляющего слова).Время перехода по цепочке данных во много раз (примерно на порядок) превышает период следования байтов, не связанных цепочкой, и, следовательно, во столько же раз уменьшается скорость Оомена с синхронными и нё буЛеризован ными внешними устройствами (типа маг нитных дисков и лент). Недостатком устройства является также сложность алгоритма формирования остаточного счета, обусловленная принятым способом подсчета количества переданных байтов, при котором требуются дополнительный регистр специальные микрооперации сумматора значительные затраты времени главным каналом и усложнение блока управления. Наиболее близкое к предлагаемому техническое решение - устройство вво да-вывода, содержащее регистр данных первый и второй счетчики, первый и второй дешифраторы, блок управления блок буферных регистров, причем пер вый, второй и третий выходы блока у равления являются соответственно пе вым, вторым и третьим выходами устройства, первый, второй, третий и четвертый выходы устройства соедине ны со входом первого счетчика, с пе вым информационным входом регистра Данных, со входом второго счетчика и с первым выходом блока управления, выход первого счетчика соединен со Входом первого дешифратора, выход к орого соединен с управляющим входом егистра данных, первый выход региста данных является четвертым выходом стройства, выход второго счетчика оединен со входом второго дешифраора, со вторым входом блока управения и с третьим выходом устройства. Недостаток этого устройства - низая скорость передачи данных, обусовленная тем, что каждый передаваеый байт последовательно проходит ерез всё буферные регистры. Другим недостатком является больой расход оборудования на построеие узла счета байтов - содержащего олноразрядный счетчик с дешифратоом и связи с выходовэтого счетчиа на вход сумматора. Разрядность четчика равна длине поля счета в упавляющем слове. От длины этого поля ависит величина массива, который ожно передать в одной операции ввоа-вывода. Поэтому поле счета обыгчно остаточно большое. Цель изобретения - повышение прозводительности и сокращение аппараурных затрат. Поставленная цель достигается тем, что в устройство введены первый и второй элементы ИЛИ, третий дешифратор, элемент НЕ элемент И/ первый и второй триггеры/ причем пятый и вюстой входы устройства соединены соответственно со входом первого элемента ИЛИ и со входом третьего дешифратора, выход которого соединен с единичным входом первого триггера и со входом элемента НЕ, выход которого соединен с нулевым входом первого триггера и с единичным входом второго триггера, нулевоЧ выход второго триггера является пятым выходом устройства, единичный выход первого триггера соединен с третьим входом блока управления и первым входом элемента И, выход второго де111иАратора соединен со вторым входом элемента И, выход которого соединен с четвертым входом блока управления, четвертый выход блока управления соединен СО ВХОДОМ второго элемента ИЛИ и с управляющим входом блока буферных регистров, выходы которого соединены соответственно со входами второго элемента ИЛИ, выход второго элемента ИЛИ соединен со вторым информационным входом регистра данных и является шестым выходом устройства, выход первого дешифратора соединен со входом первого элемента ИЛИ, выход которого соединен с информационным входом блока буферных регистров, вторые информационные выходы регистра данных соединены соответственно со входами первого элемента ИЛИ. На чертеже изображена блок-схема устЕ ойств ввода-вывода. Устройство содержит процессор 1, информационный регистр 2, регистр 3 данных, первый счетчик 4, первый дешифратор 5, блок б управления, блок 7 буферных регистров,в котохялЯ входят п буферных регистров, входную 3 и выходную 9 линии управления интерфейсом ввода-вывода, инфор 1аци онную магистраль 10 оперативной памяти, первый элемент ИЛИ 11, второй элемент ИЛИ 12, элемент НЕ 13, второй счетчик 14, второй дешифратор 15, первый триггер 16, второй триггер 17, третий дешифратор 18, элемен ты И 19, входную 20 и выходную 21 шины информационного регистра,входную 22, и выходную 23 информационные шины интерфейса ввода-вывода. Устройство работает следующим образом. Процессор 1, воспринимая команду ввода-вывода, подключается к указанному в команде каналу и считывает из оперативной памяти управляющее слово которое через регистр 2 записывается в память подканёшов (предполагается что обмен с оперативной памятью выполняется 4-байтовыми слоьами,- такую же разрядность имеют магистрали 10, 20-22 и регистры 2 и 3,другой размер слова не противоречит существу изобретения) . Два младших разряда поля данных в управляющем слове, определяющие позицию байта дгшных в слове, передаются из регистра 2 в первый счетчик 4. Несколько младших разрядов поля счета в управляющем слове передаются из регистра 2 во второй счетчик 14, число этих разрядов и соответственно разрядность счетчика 14 зависят от суммарной емкости регистров данных 3 и блока 7 буферных регистров. Максимальный код в счетчике 14 должен быть не меньше количества байтов в блоке буферных регистров {если, как показано на чер теже, счетчик 14 - четырехразрядный то при 4-байтоврм регистре 3 данных блок буферных регистров содержит 411 буферных регистров). Одновременно с заполнением счетчика 14 включается третий деши-Ъратор 18. Этот Дешифратор - общий для всех кангшов, подключенных к процессору. Он анализирует старяиУю часть поля счета. Если этот код отличен от нулевого, воз буждается сигнал на инверсном выходе дешифратора, который по линии устанавливает второй триггер 17 и сбрасы вает первый триггер 16. Затем младшая часть, поля счета обнуляется и в таком виде счет записывается в память подканалов процессора. Далее канал устанавливает связь с внешним устройством и начинает передачу данных. Прием и выдача байтов сопровождаются обменом сигналами управления по линиям 8 и 9. Если выпО:Лняе1ся операция чтения, байт данных принимается с шин 22 на соответствунадий вход первого элемента ИЛИ 11 и затем помещается в блок 7 буферных регистров, следующий байт помещается в регистр 7 и т.д. Буферные регистры используются по кольцевому принципу - после заполнения регистра 7 вновь используется регистр 7 , если он к этому времени освобождается. Параллельно с накоплением в буферных регистрах данные через второй элемент ИЛИ 12 передаются дальше в регистр 3, где формируется слово для записи в оперативную память. байтов из блока 7 буферйых регистров происходит в порядке их посту|гления из внешнего устройства (сначала считывается первый байт из регистра 1 и т.д.). Блок 6 управления следит за расположением данных в блоке 7 буферных регистров и управляет приемом и выдачей информации. Блок 6 управления содержит, в частности, счетчик буфера, который указывает, сколько байтов находится в буферных регистрах, при приеме в буферные регистры каждого байта к содержимому счетчика прибавляется единица, при вьщаче - вычитывается. С выхода второгоэлемента ИЛИ 12 данные записываются в тот байт регистра 3, который указан кодом в перэом счетчике 4. Затем к содержимому счётчика 4 прибавляется единица, и очередная передача выполняется в следующий байт регистра 3. Во время каждой передачи в регистр 3 происходит также вычитание единицы из содержимого второго счетчика 14. После того как заполнится последний байт регистра 3, блок б управления посылает запрос на передачу слова в оперативную память и пооцессор 1 переключается на обслуживание данного канала. Из памяти подканала считывается адрес данных, который помещается в регистр 2и оттуда по шинам 21 передается на магистргшь 10 оперативной памяти и в сумматор. Последний увеличивает адрес на 4 (при 4-байтовом слове), и новое значение адреса возвращается в памятъ подканалов. Затем данные из регистра 3 через гайку 20, регистр 2, шины 21 и 10 передаются в оперативную память. Регистр 3 освобождается и возобновляет прием данных из буферных регистров. По мере Формирования в регистре 3 каждого следующего слова обращения к оперативной памяти повторяются. В ходе передачи байтов в регистр 3содержимое второго счетчика 14 уменьшается и в какой-то момент становится нулевым. После следующего вычитания в счетчике образуется максимашьный код и формируется сигнал , заема, который срабатывает второй

триггер 17. Нулевое состояние этого триггера воспринимается процессором и во время ближайшего обращения к оперативной памяти происходит модификация счета и анализ его значения. Счет считывается из памяти подканалов и через регистр 2 подается в сумматор, где он уменьшается на 16 (при 4-разрядном счетчике байтов 14). Новое значение счета помещается в регистр 2, анализируется третьим дешифратором 18 и возвращается в память подканалов. Если счет отличен от нулевого, то сигнал на ин1версном ВБкодё дешифратора вновь устанавливает второй триггер 17 и подтверждает нулевое состояние первого триггера 16.

Когда счет после очередной модификации становится нулевым, срабатывает третий дешифратор 18, выходной сигнал которого устанавливает первый триггер 16. С этого момента блок б управления анализирует на равенство текущее содержимое второго счетчика 14 и счетчика буфера. Совпадение этих кодов Означает, что в буферные регистры принят последний байт данных начального управляющего слова. Тогда блок б управления анализирует условия перехода по цепочке данных и, если они отсутствуют, посылает внешнему устройству по линии 9 сигнал окончания передачи данных. Затем в оперативную память передаются данные,имеющиеся еще в регистре 3 и блоке 7 буферных регистров. Сигнал с первого выхода блока 6 управления, как сигнал окончания передачи данных, поступает в процессор. Если условия перехода по цепочке данных существуют,то вырабатывается соответствующий скгаал процессор считывает из оперативной па.мяти следующее управлянвдее слово и заполняет ячейки местной памяти подканалов, счетчики 4 и 14 и триггеры 16 и 17 новой информацией. Во время выполнения этого процесса переход по цепочке прием данных из внешнего устройства продолжается без перерыва и в прежнем темпе. Байты данных, связанные с новым управляющим словом/накапливаются в блоке 7 буферных регистров и, когда переход завершается передаются дальше в регистр 3 и в оперативную память. Таким образом,если количество регистров 7 -7ц блока буферных регистров достаточно для буферизации всех байтов, поступающих за время выполнения перехода п6 цепочке данных, то этот переход выполняется с максимальной скоростью канала. ..

В операции записи данные передаются в противоположном направлении. Слово считывается из оперативной памяти через шины 10 и 20, регистр 2, шину 21, записывается в регистр 3 и затем побайтно передается в блок 7

буферных регистров чере.з первый элемент 11, управляемый выходом первого дешифратора 5. После каждой выдачи из блока буферных регистров регистра 7 происходит прибавление единицы к содержимому первого дешифратора 5 и содержимому первого счетчика 4/ а также вычитание единицы из содержимого второго счетчика 14. Из блока 7 буферных регистров данные поступают . на .шину 23 через второй элемент ИЛИ 12. Таким образом, независимо от объема буфера байты в подканале последовательно проходят толико через два регистра. После освобождения регистра 3 обргццение к оперативной па5 мятй повторяется. На каждом таком обращении выполняется, как и в опера.ции чтения, модификация адреса данных и, если второй триггер 17 сброшен, - модификация счета с последую0 вдим анализом результата. Когда устанавливается первый триггер 16, потенциал на его выходе подготавливает элемент И 19 к приему выходного сигнала второго дешифратора 15. Последний анализирует на нуль содержимое счетчика 14. Когда дешифратор срабатывает, на выходе элемента И , 19 вырабатывается сигнал, воспринимаемый блоком б управления. Появление этого сигнала означает, что из 0 регистра 3 выдан последний байт из числа указанных в поле счета начального управлякяцего слова. Далее анализируются условия перехода по цепочке данных и в процессор посылается 5 сигнал окончания передачи данных либо сигнал перехода. Если необходимо, переход выполняется одновременно с вьщачей из блока 7 буферных регистров последних байтов старого массива. Если цепочки данных нет, то после выдачи этих байтов внешнему устройству посылается по линии 9 сигнал окончания передачи данных.

г Передача данных может завершиться до исчерпания счета. Происходит это по инициативе канала либо внешнего устройства вследствие обнаружения необычной ситуации или зо-- ны на носителе.

По сигналу окончания передачи данных процессор 1 формирует информацию, характеризую 4УЮ завершившуюся операцию и содержащую, в частности, остаточный счет. Последний образуется следующим образом. Счет из памяти подканалов через регистр 2 подается в сумматор, где он логически суммируется с содержимым счетчика 14 байтов. Результат и является остаgQ точным счетом для операции чтения. Если выполнялась операция записи,к этому результату прибавляется содержимое счетчика буфера, соединенного с сумматором, как и счетчик 14, рез, группу разрядов регистра 2.

В предлагаемой структуре буфера г.анных отсутствуют непосредственные передачи из одного буферного регистра в другой и в каждый момент времени обращение выпопняется только к одному буферному регистру. Благодаря этим свойствам буфер может быть построен на элементах современной полупроводниковой памяти. Такой буфер,обладая большой емкостью, имеет простую схему и содержит мало элементов.

Формула изобретения

Устройство ввода-вывода, содержащее регистр данных, первый и втЬрой счетчики, первый и второй дешиЛраторы, блок управления, блок буферньос регистров, причем первый, второй и третий выходы блока управления являются соответственно первым, вторым и третьим 8ыход 1ми устройства, первый, второй третий и Ч€тверть7й выходы устройства соед йненц соответственно со входом перво1ч Ciet4«Ka, с первым информационным входом регбист- ра данных, со входом второго счетчика и с первым выходом блока управления, выход первого счётчика соединен со входом Первого дешифратора, выход которого соединен с управляющим входом регистра данных, первый выход регистра данных является четвертым выходом устройства, выход второго счетчика соединен со входом второго дешифратора, со вторым входом блока упргшления и- с третьим выходом устройства, отличающееся тем, что, с целью повышения производиteльнocти и сокращения аппаратурньос затрат, в устройство введены первый и второй элементы ИЛИ, третий

дешифратор, элемент НЕ. элемент И, первый и второй триггеры, пятый и шестой входы устройства соединены соответственно со входом первого -элемента ИЛИ и со входом третьего дешифратора, выход котррого соединен с единичным входом первого триггера и со входом элемента НЕ, выход которого соединен с нулевым входом первого триггера и с единичным входом второго триггера, нулевой выход второго триггера является пятым выходом устройства, единичный выход первого триггера соединен с третьим входом блока управления и с первым входом элемента И, в.ыход второго дешифратора соединен со вторым входом элемента И, выход которого соединен с четвертьм входом блока управления, четвертый выход блока управления соединен со входом второго элемента ИЛИ и с управляющим входом блока буферных регистров, выходы которого соединены соответственно со входами второго элемента ИЛИ, выход второго элемента ИЛИ соединен со вторьм информационным входом регистра данньрс и являет- ся шестым выходом устройства, выход первого дешиЛратора соединен со входом первого элемента ИЛИ, выход которого соединен с информационным входом блока буферных регистров, вторые информационные выходы регистра данных соединены соответственно со входами первого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 312254, кл. G 06 F.

. 2. Хассон С. Микропрограммное управление. М., Мир, 1974, т.2, гл. 7, 8 (прототип) . I I I I 113.HI 1 %г: У :j f. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

Авторы

Даты

1980-11-23—Публикация

1976-12-27—Подача