1

Изобретение относится к области радиотехники, в частности к радиоприемным устройствам, и может быть использовано в качестве регулятора для усилителей с автоматической регулировкой усиления (АРУ).

Известны устройства, содержащие дифференциальный усилитель (ДУ), инвертирующий вход которого через конденсатор соединен с вьаходом и Через резистор) со входом устройства, и цепь, создающую пороговое напряжение на нёинвертирующем входе ДУ 1 и 21.

Недостаток аналогов - большое время установления, под которым следует понимать интервал от момента, когда поданный входной сигнал превысит пороговЬе напряжейие, до момента перехода ДУ из режима ограничения в режим.линейного усиления, т.е. до момента начала интегрирования.

Наиболее близким по технической сущности является интегрирующее устройство, содержащее дифференциальный усилитель, инвертирующий вход которого Через интегрирующий конденсатор соединен с выходом дифференциального усилителя и через масштабный резис,тор со входом устройства, и источник

;Пг1Орогового напряжения, подключенный к неинверТИруй)йГбМ5ГвхбдУ дифференциального усилителя. При указанном .соединении элёйёйТс в сИ1 наЛ на выходе устройства пропорционален- интегралу разностного сигнала, т.е. разности потенциалов инвертирующего и неинвертирующего входов ДУ 3.

Однако известное устройство имеет

0 недостаток - большое время установления. Это обусловлено следующим. Одно из основных требований к ДУ -.большой коэффициент усиления. Поэтому современные ДУ работают в режиме линейного

5 усиления только если разностный сигнал не прейос5 бДит единиц милливольт. Пороговое напряжение ДУ обычно выбирается порядка сотен милливольт. Следовательно, при исчезновении входного

0 сигнала разностный сигнал возрастает до 9отен милливольт и ДУ переходит в режим глубокого ограничения. Этот режим будет начальным (статичёрким) режимом рассматриваемого устройства

5 при отсутствии входного си.гнала. Очевидно, что при подаче входного сигнала, даже имеющего крутой и поэтому практически мгновенно превышеиощего пороговое напряжение, имеющееся

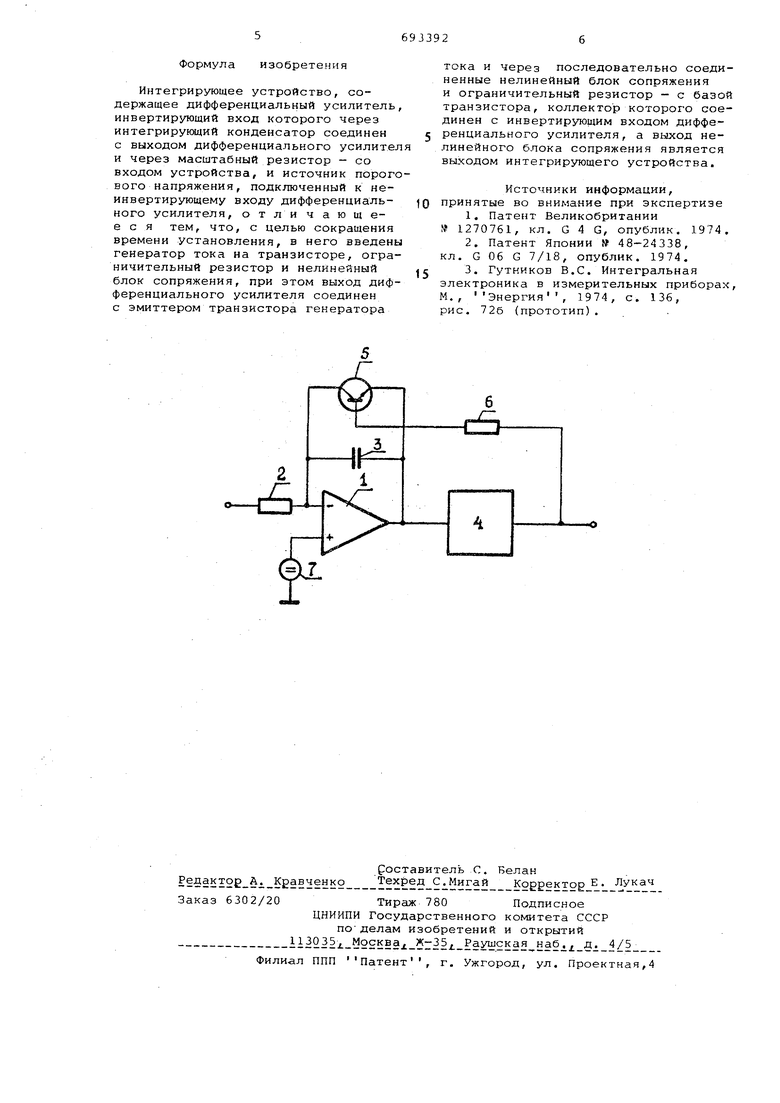

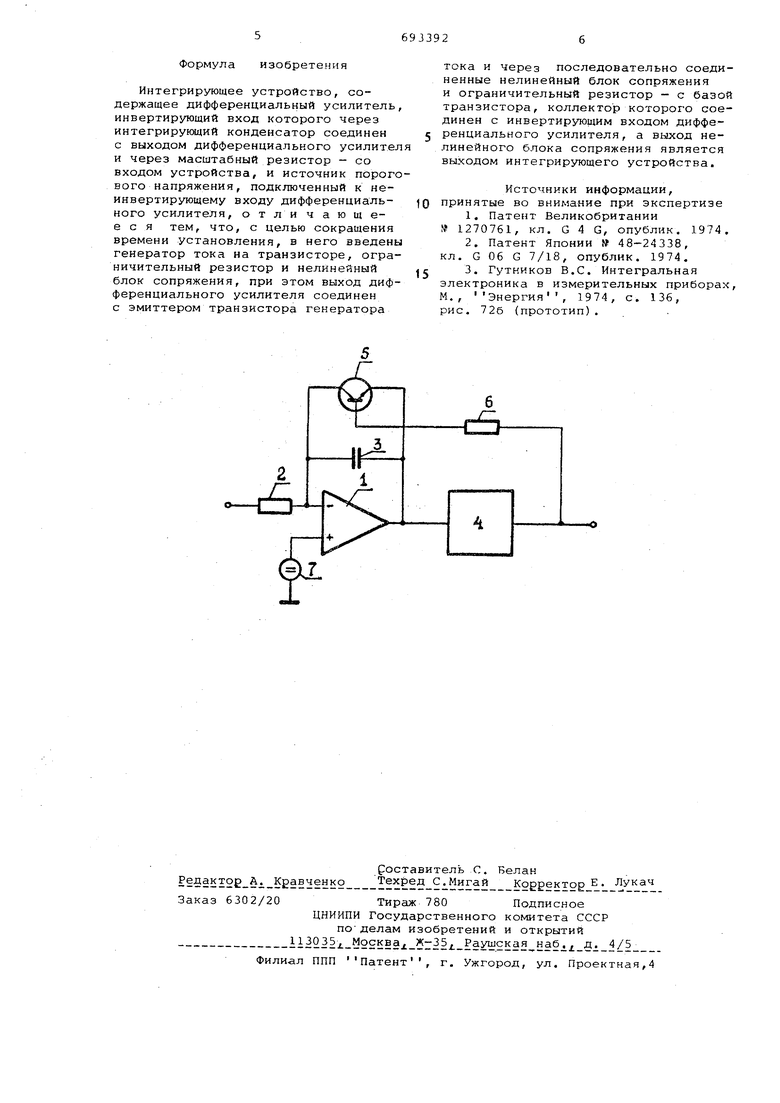

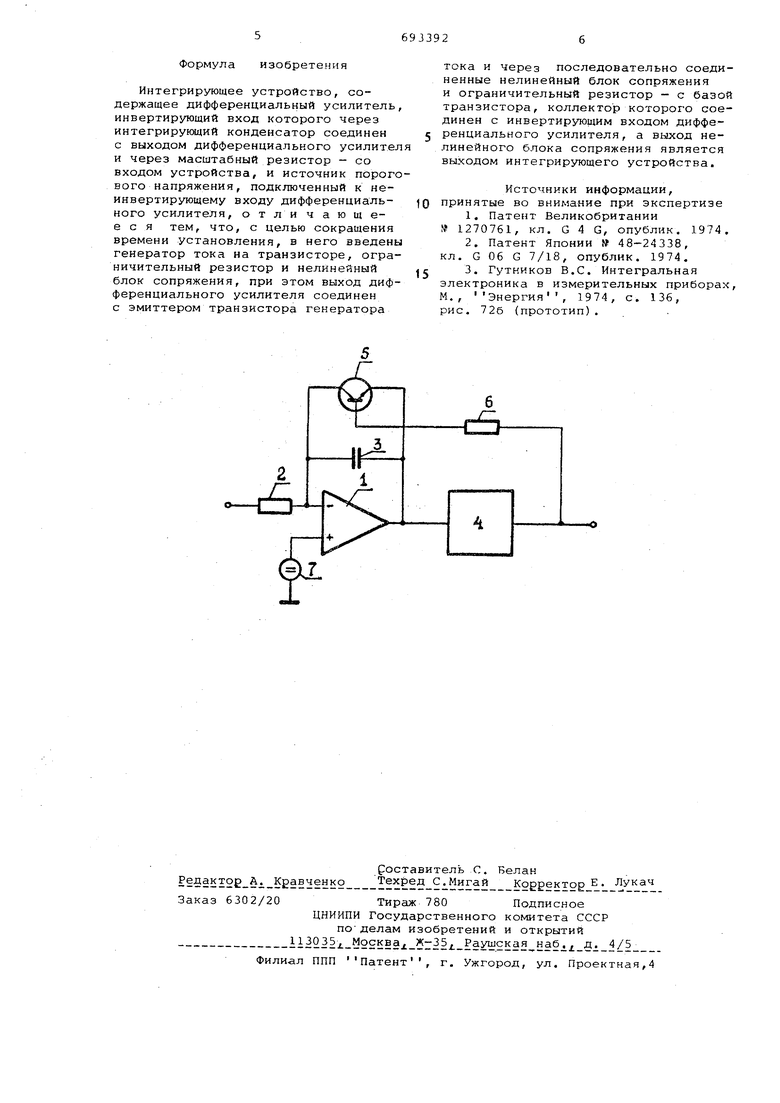

0 на неинвертирующем, входе ДУ, устройство начнет выполнять свою основную функцию интегрирования разностного сигнала не сразу. Интегрирование как линейная операция начнется с запаздыванием на время, необходимое для перехода ДУ из режима ограничения в режим линейного усиления. Время установления, характеризующее это запаздывание, на практике составляет несколько десятков микросекунд. Целью изобретения является сокращение времени установления. Поставленная цель достигается тем, что в интегрирующее устройство введены генератор тока на транзисторе, ограничительный резистор и нелинейный блок сопряжения, при этом выход дифференциального усилителя , соединен с эмиттером транзистора 17енератЬра тока И через последовательно соединенные нелинейный блок сопряжения и ограничительный резистор - с базой транзистора, коллекTdp которого соединен с инвертирующим входом дифференциального усилителя, причем выход нелинейного блока сопряжения является выходом интегрирующего устройства. . На чертеже приведена функцион.альная схема устройства. . Интегрирующее устройство содержит дифференциальный операционный усилитель 1, масштабный резистор 2, интег рирующий конденсатор 3, нелинейный блок сопряжения 4, генератор тока на транзисторе 5, ограничительный резистор 6 и источник порогового напр 7, ; : Инвертирующий вхбд дифференциального усилителя через интегрирующий конденсатор 3 соединен с выходом эт го усилителя и через масштабный резистор 2 со входом, устройства. Не , инвертирующий вход дифференциального усилителя 1 присоединен к одному полюсу источника порогового напряже ния 7, д;ругой; полюс которого эаземлен. Выход дифференциального усилит ля 1 соединен с эмиттером транзисто ра 5 и через последовательно соедин ные нелинейный блок сопряжения 4 и ограничительный резистор б г- с базо этого же транзистора. Коллектор тра зистора 5 соединен с инвертирующим входом дифференциального усилителя Точка соединения нелинейного блока сопряжения 4 и резистора б является выходом интегрирующего устройства. . Назначение элементов заключается в следующем. ДУ 1, резистор 2 и кон денсатор 3 образуют интегратор с постоянной времени, в К раз (К - коэффициент усиления ДУ) превосходя щей постоянную времени RC-цепи, сос тоящей из резистора 2 и .конденсатор 3. Нелинейный блок сопряжения (НБС) 4 выполняет две функции: линейного буферного каскада, устраняющего влияние нагрузки на параметры интегратора; нелинейного элемента, управляющего коллекторным током транзистора 5. Транзистор 5 служит генератором компенсирующего тока для инвертирующего входа ДУ 1 при отсутствии сигнала на входе устройства. Ограничительный резистор 6 задает ток базы транзистора 5. Источник порогового напряжения 7 определяет требуемый порог срабатывания интегратора Рассмотримработу устройства, считая, что сигнал и пороговое напряжение, создаваемое источником 7, имеют отрицательную полярность (при положительной полярности принцип работы не изменится, но Транзистор 5 должен иметь другой тип проводимости) . Пока входйой сигнал отсутствует (начальнь1й статичёс1 ий режим) , транзистор 5. открыт, поскольку отрицательное напряжение на входе устройства по абсолютной величине меньше отрицательного напряжения на выходе ДУ 1. Путём выбора величины коэффициента передачи Напряжения НБ.С 4 и сопротивления резистора б обеспечивается такая величина коллекторного тока транзистора 5, являющегося компенсирующим током инвертирующего входа ДУ 1, при которой ДУ 1 Находится в линейном режиме а напряжение;., на выходе устройства имеет заданную начальную величину.- . .-, При по-явлении входного сигнала напряжение на выходе ДУ 1 начинает уменьшаться, а напряжение на выходе НБС 4, благодаря его нелинейности, изменяется незначительно. Поэтому коллекторный ток транзистора 5 быстро уменьшается, и после превьддения сит.налом на инвертирующем входе ДУ 1 уровня порогового напряжения источника 7 компенсирующий ток инвертирующего входа ДУ 1 становится пренебрежимо мал и на дальнейшую работу устройства не влияет. Поскольку при отсутствии входного сигнала, компенсирующий ток инвертирующего входа ДУ 1 .предотвращает переход ДУ в режим ограничения, в предлагаемом устройстве линейное интёгрирова.ние разностного сигнала начинается практически без запаздывания, введенный в предлагаемую схему НБС 4 может быть выполнен, например, в виде .последовательно соединенных резистивного делителя напряжения и эмиттерного повторителя, рабочая точка которого установлена так, чтобы начальный участок его а:мплитудной характеристики был нелинеен. Использование изобретения позволит создавать усилители с АРУ, сочетающие пренебрежимо малую статичес|Кую ошибку регулирования.с высоким быстродействием АРУ.

Формула изобретения

Интегрирующее устройство, содержащее дифференциальный усилитель, инвертирующий вход которого через интегрирующий конденса тор соединен с выходом дифференциального усилител и через масштабный резистор - со входом устройства, и источник порогового напряжения, подключенный к неинвертирующёму входу дифференциа:льного усилителя, отличающееся тем, что, с целью сокращения времени установления, в него введены генератор тока на транзисторе, ограничительный резистор и нелинейный блок сопряжения, при этом выход дифференциального усилителя соединен с эмиттером транзистора генератора

тока и через последовательно соединенные нелинейный блок сопряжения и ограничительный резистор - с базой транзистора, коллектор которого соединен с инвертирующим входом дифференциального усилителя, а вьлход нелинейного блока сопряжения является выходом интегрирующего устройства.

Источники информации,

0 принятые во внимание при экспертизе

1.Патент Великобритании

1270761, кл. G 4 G, опублик. 1974.

2.Патент Японии № 48-24338, кл. G 06 G 7/18, опублик. 1974.

3.Гутников B.C. Интегральная

5 электроника в измерительных приборах, М., Энергия, 1974, с. 136,

рис. 726 (прототип). . ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| Амплитудный ограничитель | 1989 |

|

SU1757094A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2005 |

|

RU2282303C1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| КВАРЦЕВЫЙ ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ АМПЛИТУДЫ | 1991 |

|

RU2020726C1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Аналоговое делительное устройство | 1979 |

|

SU858008A1 |

| Аналоговый умножитель | 1980 |

|

SU945871A1 |

Авторы

Даты

1979-10-25—Публикация

1975-10-20—Подача