Изобретение относится к области вычислительной техники и может применяться в различных цифровых приборах и устройствах. Известны множительные устройства использующие число-импульсный метод умножения двух чисел и содержащие регистры сомножителей, выходной регистр, блок триггеров, генератор им пульсов, дополнительные триггеры, элементы И и ИЛИ 1. Недостатком таких устройств явля ются низкое быстродействие и ограни ченные функциональные возможности. Наиболее близким по технической сущности к предложенному устройству является число-импульсное множительное устройство, содержащее п счетчиков множимого, m счетчиков множител выходной регистр, управляющие счетчи ки, триггеры элементы И и ИЛИ, причем выходы счетчиков множителя подк.г ючены к единичным входам соответст венно I -г п-го триггеров, единичные выходы которых соединены с первыми входами соответственно I -г п-го элементов И, единичный вход (п+1)-го триггера подк.пючен к управляющему входу устройства, а единичный выход к первому входу (п+1)-го элемента И, второй вход которого подключен к тактовому входу устройства 2, Недостатком этого устройства является низкое быстродействие и невозможность представления чисел в любой системе счисления без изменения структуры схемы. Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства. Поставленная цель достигается тем, что число-импульсное множительное устройство содержит коммутаторы и элемент задержки, причем первый выход первого коммутатора подключен ко входам счетчиков множимого, вторым входам 1 -т- п-го элементов И и входу первого управляющего счетчика, выход которого соединен с нулевыми входами 1 -г п-го триггеров, входом элемента задержки и первьлм входом первого элемента ИЛИ, второй вход которого подключен ко второму выходу первого коммутатора, выходы 1 -г п-го элементов И подключены к соответствующим входам второго коммутатора, (m+n) выходов которого соединены с соответствующими разрядными входами выходного регистра, управляющий вход которого подключен к выходу элемента

эалдержки, выход первого элемента ИЛИ подключен ко входу второго управляющего счетчика, выход которого соединен со входом третьего управляющего счетчика и единичным входом (п+2)-го триггера, нулевой вх-ц которого подключен к выходу второго элемента ИЛИ входы которого подключены к выходам счетчиков множителя, входы которых соединены с соответствующими выходами третьего коммутатора, m управляющих входов которого подключены к соответствующим разрядным выходам третьего управляющего счетчика, которые подключены также к соответствующим m управляющим входам второго коммутатора, вход третьего коммутатора соединен с выходом первого элемента ИЛИ, первый разрядный выход третьего управляющего счетчика подключен также к нулевому входу (п+1)-го триггера,единичный выход (п+2)-го триггера подключен к первому входу первого коммутатора, второй вход которого подключен к выходу (п+1)-го элемента И.

Поставленная цель достигается также тем, что выходной регистр содержит (m+n) разрядов, каждый из которых содержит счетчик, триггер и элемент И, причем вход счетчика подключен к соответствующему разрядному входу выходного регистра, а выход - к единичному входу триггера, единичный выход которого подключен к первому входу элемента И, выход которого подключен к дополнительному входу счетчика последующего разряда, вторые входы элементов И и нулевые входы триггеров всех разрядов выходного регистра подключены к его управляющему ВХОДУ

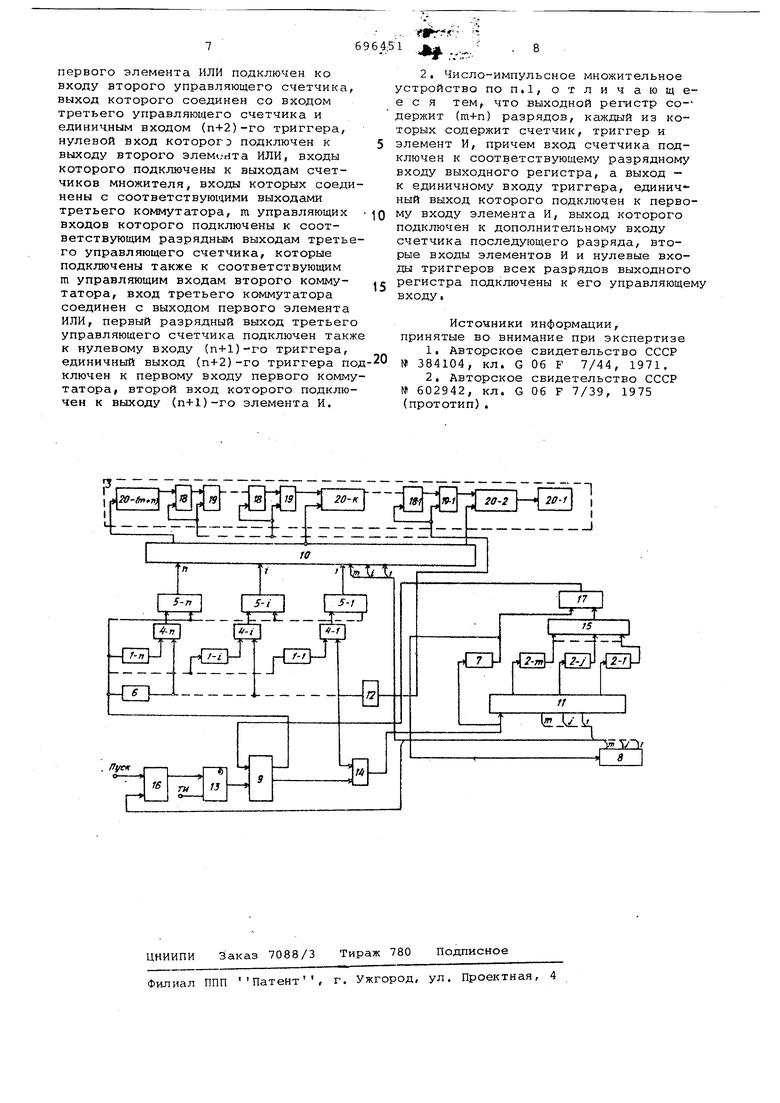

Устройство содержит п счетчиков множимого 1, m счетчиков множителя 2 выходной регистр 3, 1 -г п-ый триггеры 4; первый элементы И 5, управляющие счетчики 6, 7, 8, коммутаторы 9, 10, 11, элемент задержки 12 (п+1)-ый элемент И 13, элементы ИЛИ 14, 15., (п+1)-ый триггер 16, (п+2)-о Триггер 17. Выходной регистр 3 содержит в своем составе триггеры 18, элементы И 19 и счетчики 20,

Выходы счетчиков 1 подключены ко входам соответствующих триггеров 4., другие входы которых подключены к выходу управляющего счетчика б, а Выходы - ко входам соответствующи элементов И 5, другие входы которых соединены со входами счетчиков 1, входом управляющего счетчика 6 и первым выходом коммутатора 9.

Выходы счетчиков 2 подключены ко входам элемента ИЛИ 15, а входы - к разрядн1.1м выходам коммутатора 11. Выход элемента ИЛИ 15 подключен ко входу триггера 17, другой вход которого соединен с выходом управляюшего счетчика 7 и входом управляющего счетчика 8 выходы оторого подключены к управляющим ходам ког /пчутатора 10 и коммутатоа 11. Вход коммутатора 11 соединен о входом счетчика 7. Выход триггеа 17 подключен к первому входу комутатора 9, второй вход которого одключен к выходу элемента И 13, ходы которого соединены с выходом риггера 16 и с тактовым входом стройства. Входы триггера 16 соедиены с управляющим входом устройства и с первым выходом счетчика 8.

Выходы элементов И 5 подключены к разрядным входам коммутатора 10. Выход счетчика 6 подключен ко входу элемента задержки 12 и первому входу элемента. ИЛИ 14.

Выходной регистр 3 содержит (m+n) счетчиков 20, элементы И 19 и триггеры 18. Вход первого счетчика 20 подключен к выходу второго счетчика 20. Первый вход второго и последующих счетчиков 20 подключены к выходу соответствующего элемента и 19, а другие входы счетчиков 20 соединены с разрядными выходами коммутатора 10. Первые входы элементовИ 19 подключены к выходам соответствующих триггеров 18, входы которых подключены к выходам соответствующих счетчиков 20, Другие входы триггеров 18 и вторые входы элементов И 19 объединены и подключены к управляющему входу регистра 3, который соединен с выходом элемента задержки 12.

Количество состояний счетчиков 1, 2, 6, 7, 20 равно основанию выбранной системы счисления,.

Работа, устройства заключается в следующем.

В исходном состоянии в счетчиках 1 и 2 записаны значения обоих сомножителей, в счетчики 20, б, 7, 8 записаны нули. На выходах триггеров 16 и 18 находятся запрещающие потенциалы, состояние триггера 17 разрешает коммутацию входной шины коммутатора 9 на второй выход.

Сигнал, Пуск на управляющем входе устройства переводит триггер 16 в разрешающее состояние. Тактовые импульсы (ТИ) через элемент. И 13,коммутатор 9,элемент ИЛИ 14 начинают поступать на вход счетчика

7и через коммутатор 11 на вход первого счетчика 2/ где было записано значение старшего разряда множителя. Сигнал переполнения счетчика 2-1 через элемент ИЛИ 15 изменяет состояние триггера 17, переключая тем самым входную шину коммутатора 9. Анализ старшего разряда множителя заканчивается записью его значения

в дополнительном коде в счетчик 7.

8случае нулевого значения старшего разряда множителя импульс переполнения появляется одновременно в счетчиках 2-1 и 7, триггер 17 не изменяет своего состояния, а счетчик 8 переходит в следующее состояние, переключая входную шину коммутатора 11 на второй выход и подготавливая тем самым устройство к ана лизу второго разряда множителя. Следующая операция заключается в параллельном поразрядном сугчмировании множимого в регистре произведени Число суммирований равно значению старшего разряда множителя, ТИ через элемент И 13 и коммутатор 9 поступают на входы счетчиков 1,6 и на первые входы элементов И 5 На выходе i-того (i 1,...,п) триггера 4 формируется импульс с длитель ностью равной значению i-того (i 1, . . . ,п) разряда множимого, пропус кая на выход i-Toro (i l,,..,n) элемента И 5 соответствующее количество импульсов. Через коммутатор 10 эти импульсы поступают на второй вход К+1-ГО счетчика 20/суммируясь со значением его исходного состояния. Количество таких параллельных суммирований множимого определяется значением анализированного разряда множителя. При окончании последнего суммирования количество переполнений счетчика 6, поступивших через элемент ИЛИ 14 на счетчик 7 и через ком мутатор 11 на счетчик 2-1 станет равным значению анализируемого разря да множителя. Счетчики 2-1 и 7 вернутся в исходные состояния, а импуль переполнения последнего изменит состояние триггера 17 и состояние счетчика 8, подготавливая устройство к анализу следующего разряда множителя При возникновении переполнений счетчиков 20 взводится соответствующий триггер 18, переходя в разрешающее состояние. Импульс переполнения счетчика б через элемент задержки 12 проходит через элемент И 19 на первы вход следующего счетчика 20 и своим задним фронтом возвращает взведенный триггер 18 в исходное состояние. В случае сквозного переноса импульс пе реполнения К-того счетчика 20, образ ванный в свою .очередь переполнением (К+1)-го счетчика 20, своим передним фронтом взводит К-2-ой триггер 18, возвращаемый задним фронтом импульса с выхода элемента задержки 12 в исходное состояние, разрешая таким образом прохождение импульса перенос через элемент И 19 - (К-2) на первый вход К-1-го счетчика 20. Дальнейшая работа устройства происходит аналогично вышеописанному. Процесс умножения заканчивается пере полнением счетчика 8, которое переводит триггер 16 в исходное состояни К этому моменту в регистре 3 записан число равное произведению обоих сомножителей, а счетчики 1 и 2 приведены в исходное состояние. Быстродействие данного устройства значительно выше, чем у известного. Так для выполнения операции умножения двух 12 разрядных десятичных чисел при помощи заявленного устройства необходимо (1+9+10) такта. При умножении же двух 12-разрядных чисел при помощи известного устройства необходимо около 2-10 тактов. Поэтому данное устройство по быстродействию в большей степени приближается к известным устройствам умножения чисел, представленных параллельным двоичным кодом, но позволяет не меняя структуру схемы использовать любую систему счисления. Эти особенности предлагаемого устройства отвечают требованиям, предъявляемым к цифровым приборам и системам управления. Формула изобретения 1. Число-импульсное множительное устройство, содержащее п счетчиков множимого, m счетчиков множителя, выходной регистр, управляющие счетчики, триггеры, элементы И и ИЛИ, причем выходы счетчиков множителя подключены к единичным входам соответственно 1 -г п-го триггеров, единичные выходы которых соединены с первыми входами соответственно первого т: п-го элементов И, единичный вход (п+1)-го триггера подключен к управляющему входу устройства, а единичный выход - к первому входу (п+1)-го элемента И, второй вход которого подключен к тактовому входу устройства, отличающееся тем, что, с целью.повышения быстродействия и расширения функциональных возможностей устройства, заключающемся в возможности представления сомножителей в произвольной системе счисления, устройство дополнительно содержит коммутаторы и элемент задержки, причем первый выход первого коммутатора подключен ко входс1М счетчиков множимого, вторым входам 1 -г п-го элементов И и входу первого управляющего счетчика, выход которого соединен с нулевыми входами первого -гп-го триггеров, входом элемента задержки и первым входом первого элемента ИЛИ, второй вход которого подключен ко второму выходу первого коммутатора, выходы первого 4-п-го элементов И подключены к соответствующим входам второго коммутатора, (га+п) выходов которого соединены с соответствующими разядными входами выходного регистра, правляю1аий вход которого подключен к выходу элемента задержки, выхол первого элемента ИЛИ подключен ко входу второго управляющего счетчика, выход которого соединен со входом третьего управляющего счетчика и единичным входом (п+2)-го триггера, нулевой вход которого подключен к выходу второго элем.;г1та ИЛИ, входы которого подключены к выходам счетчиков множителя, входы которых соеди нены с соответствующими выходами третьего коммутатора, m управляющих входов которого подключены к соответствующим разрядным выходам третье го управляющего счетчика, которые подключены также к соответствующим m управляющим входам второго коммутатора, вход третьего коммутатора соединен с выходом первого элемента ИЛИ, первый разрядный выход третьег управляющего счетчика подключен такж к нулевому входу (п+1)-го триггера, единичный выход (п+2)-го триггера п ключен к первому входу первого комм татора, второй вход которого подклю чен к выходу (п+1)-го элемента И. 2, Число-импульсное множительное устройство по п,1, отличающееся тем,- что выходной регистр содержит (m+n) разрядов, каждый из которых содержит счетчик, триггер и элемент И, причем вход счетчика подключен к соответствующему разрядному входу выходного регистра, а выход к единичному входу триггера, единич ный выход которого подключен к первому входу элемента И, выход которого подключен к дополнительному входу счетчика последующего разряда, вторые входы элементов И и нулевые входы триггеров всех разрядов выходного регистра подключены к его управляющему входу. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 384104, кл. G Об F 7/44, 1971, 2.Авторское свидетельство СССР № 602942, кл. G Об F 7/39, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1977 |

|

SU696453A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения | 1976 |

|

SU744563A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-29—Подача