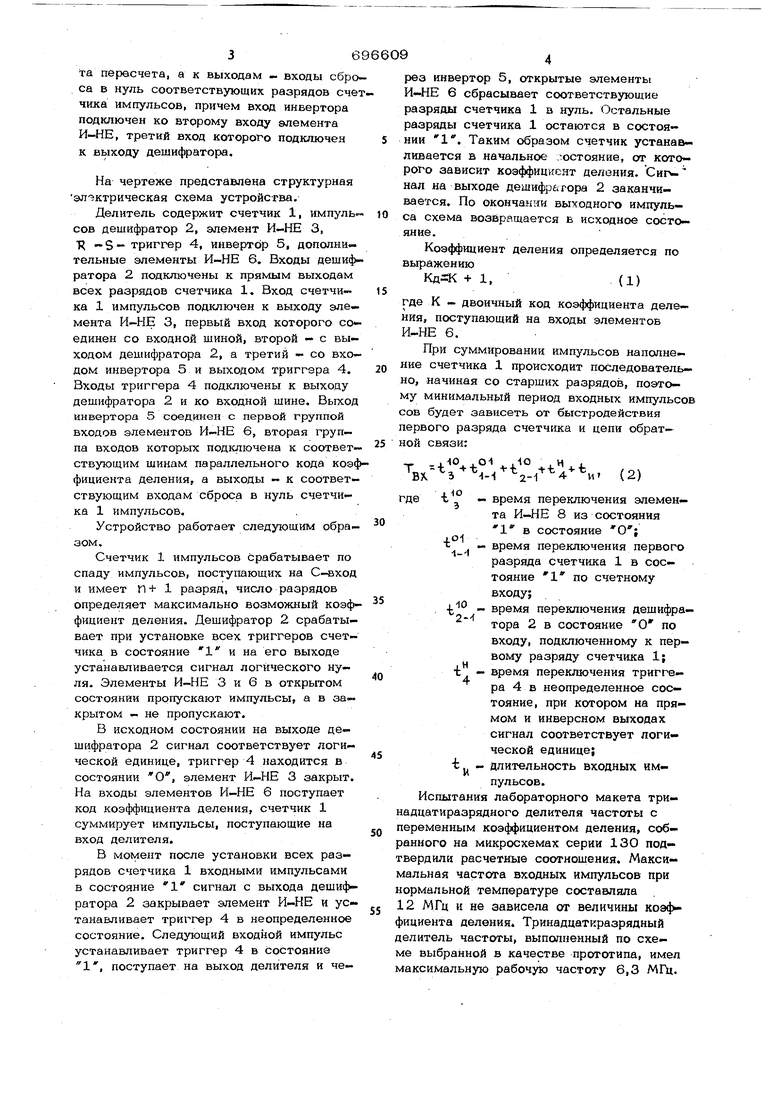

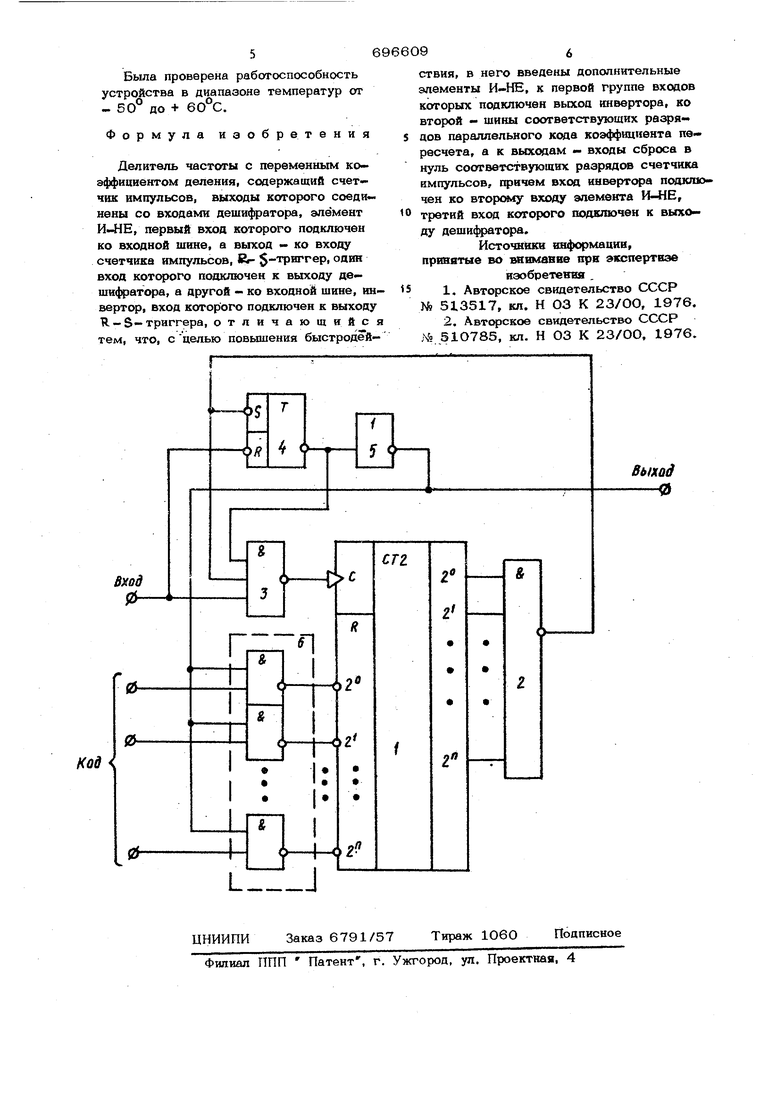

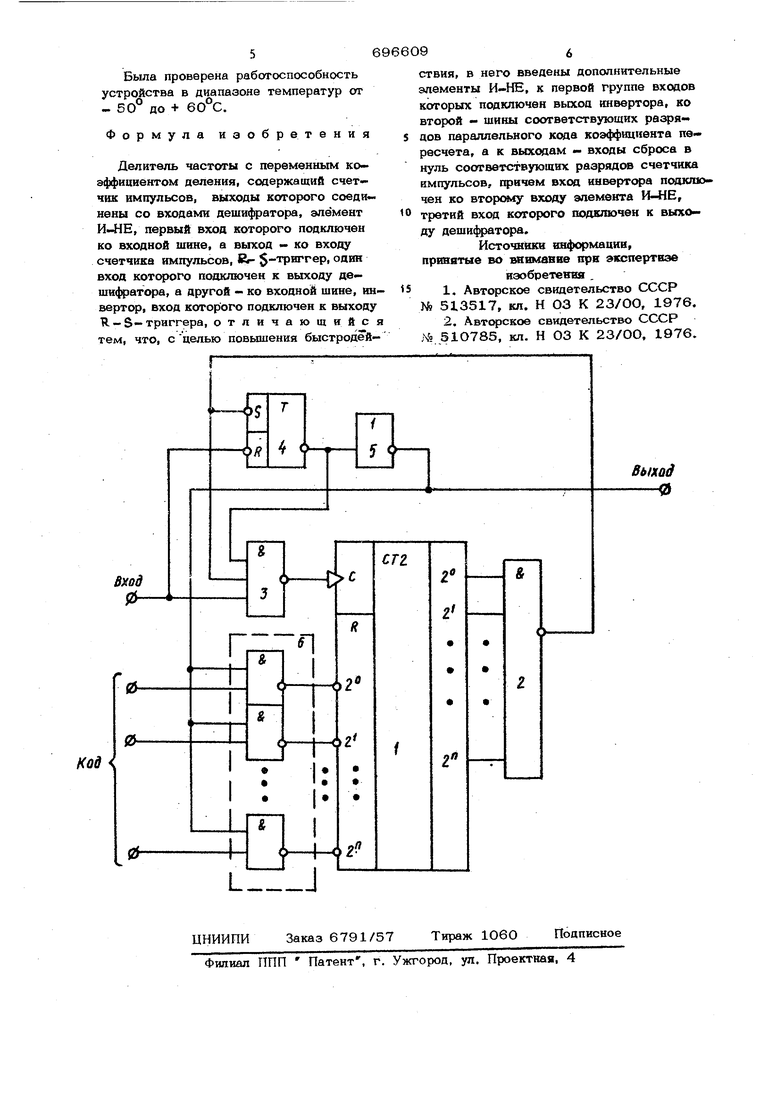

Изобретение относится к импульсной технике и может быть использовано, в частности, Б устройствах синхронизации. Известен делитель частоты, содержащий счетчик импульсов, дешифратор, и элементы И l. Недостатком этого делителя является низкое быстродействие и невозможность управления коэффициентом деления с помощью двоичного кода. Из известных делителей частоты наиболее близким по технической сущности и схемному решению к предлагаемому является делитель частоты с коэффициентом пересчета не равным 2 . Этот делитель содержит счетчик, дешифратор, -5 триггер, элемент И-НЕ на входе счетчика, инвертор на выходе триггера 2. Максимальная частота входных импул сов зависит не только от быстродействия цепи обратной связи - дешифратора, /R -3- триггера, инвертора, но и от быс родействия всего счетчика, что снижает быстродействие устройства с увеличением числа разрядов счетчика. Таким образом, недостатком известного устройства является низкое быстродействие. Целью настоящего изобретения является повышение быстродействия делителя частоты с переменным коэффициентом деления. Поставленная цель достигается тем, что в делитель частс ы с переменным коэффициентом деления, содержащий счетчик импульсов, выходы которого соединены со входами дешифраторов, элемент И-НЕ, первый вход которого подключен i , ко входной шине, а ;звыход - ко входу счетчика импульсов, R - 5- триггер, один вход которого подключен к выходу дещи(} ратора, а второй - ко входной шине, инвертор, вход которого подключен к выходу 1 -S- триггера, введены дополнительные элементы И-НЕ, к первой группе входов которых подключены выход инвертора, ко второй - шины соответствующих разрядов параллельного кода коэффициен- та пересчета, а к выходам входы сбро са в нуль соответствующих разрядов сче чика импульсов, причем вход инвертора подключен ко второму входу элемента И-НЕ, третий вход которого подключен к выходу дешифратора. На чертеже представлена структурная электрическая схема устройства. Делитель содержит счетчик 1, импуль™ сов дешифратор 2, элемент И-НЕ 3, Tj -S- триггер 4, инвертор 5, дополнительные элементы И-НЕ 6. Входы дешифратора 2 подключены к прямым выходам всех разрядов счетчика 1, Вход счетчика 1 импульсов подключен к выходу элемента И-НЕ 3, первый вход которого соединен со входной шиной, второй - с выходом дешифратора 2, а третий - со входом инвертора 5 и выходом триггера 4. Входы триггера 4 подключены к выходу дешифратора 2 к ко входной шине. Выход инвертора 5 соединен с первой группой входов элементов И-НЕ 6, вторая группа входов которых подключена к соответствующим шинам параллельного кода коэф фициента деления, а выходы - к соответствующим входам сброса в нуль счетчика 1 импульсов. Устройство работает следующим образом. Счетчик 1 импульсов срабатывает по спаду импульсов, поступающих на и имеет ГИ- 1 разряд, число разрядов определяет максимально возмохшый коэф- фициент деления. Дешифратор 2 срабатывает при установке всех триггеров счетчика в состояние и на его выходе устанавливается сигнал логического нуля. Элементы И-НЕ 3 и 6 в открытом состоянии пропускают импульсы, а в закрытом - не пропускают. В исходном состоянии на выходе дешифратора 2 сигнал соответствует логической единице, триггер 4 находится в состоянии О, элемент И-НЕ 3 закрыт. На входы элементов И-НЕ 6 поступает код коэффициента деления, счетчик 1 суммирует импульсы, поступающие на вход делителя. В момент после установки всех разрядов счетчика 1 входными импульсами в состояние сигнал с выхода дешифратора 2 закрывает элемент И-НЕ и устанавливает триггер 4 в неопределенное состояние. Следующий входной импульс устанавливает триггер 4 в состояние , поступает на выход делителя и через инвертор 5, открытые элементь И-НЕ 6 сбрасывает соответствующие разряды счетчика 1 в нуль. Остальные разряды счетчика 1 остаются в состоянии . Таким образом счетчик устанавливается в начальное .-остояние, от которого зависит коэффициент деления. нал на выходе дешифр&гора 2 заканчивается. По окончании выходного импульса схема возвращается в исходное состояние. Коэффициент деления определяется по выражению +1,(1) где К - двоичный код коэффициента деления, поступающий на входы элементов И-НЕ 6. При суммировании импульсов наполнение счетчика 1 происходит последовательно, начиная со старших разрядов, поэтому минимальней период входных импульсов сов будет зависеть от быстродействия первого разряда счетчика и цепи обратной связи: 1-tV-b -время переключения элемента И-НЕ 8 из состояния 1 в состояние О; -время переключения первого разряда счетчика 1 в состояние по счетному входу; время переключения дешифратора 2 в состояние О по входу, подключенному к первому разряду счетчика 1; время переключения триггера 4 в неопределенное состояние, при котором на прямом и инверсном выходах сигнал соответствует логической единице; t - длительность входных импульсов. Испытания лабораторного макета триадцатиразрядного делителя частоты с еременным коэффициентом деления, собанного на микросхемах серии 130 подвердили расчетные соотношения. Максиальная частота входных импульсов при ормальной температуре составляла 2 МГц и не зависела от величины коэфициента деления. Тринадцаткразрядный елитель частоты, выполненный по схее выбранной в качестве прототипа, имел аксимальную рабочую частоту 6,3 МПх.

Была проверена работоспособность устройства в диапазоне температур от - 50° до + 60°С.

Формула изобретения

Делитель частоты с переменным ко эффиииентом деления, содержащий счетчик импульсов, выходы которого соединены со входами дешифратора, элемент И-НЕ, первый вход которого подключен ко входной шине, а выход - ко входу счетчика импульсов. Кг- §-триггер, один вход подключен к выходу де- ши(атора, а другой - ко входной шине, инвертор, вход которого подключен к выходу R - S- триггера, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительные элементы И-НЕ, к первой группе входов которых подключен выход инвертора, ко второй - шины соответствующих

дов параллельного кода коэффициента пе ресчета, а к выходам - входы сброса в нуль соответствующих разрядов счетчика импульсов, причем вход инвертора подклю чен ко входу элемента И-НЕ,

третий вход которого подключен к выходу дешифратора.

Источники информации, принятые во ш1имаВЕе прв экспертизе изобретентаг .

1. Авторское свидетельство СССР N9 513517, кл. Н ОЗ К 23/00, 1976.

2. Автсфское свидетельство СССР .4 51О785, кл. Н ОЗ К 23/ОО, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119177A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU980291A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Синусно-косинусный функциональный преобразователь | 1980 |

|

SU888111A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Делитель частоты следования импульсовС пРОгРАММНыМ упРАВлЕНиЕМ | 1979 |

|

SU841123A1 |

| Делитель частоты с переменным коэффициентом деления | 1989 |

|

SU1691958A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-08—Подача