(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПРОГРАММНЫМ УПРАВЛЕНИЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| Преобразователь перемещения в код | 1982 |

|

SU1043701A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты с програмным управлением | 1976 |

|

SU652709A1 |

| Управляемый делитель частоты | 1978 |

|

SU741474A2 |

| Устройство для деления число-импульсного кода на константу | 1981 |

|

SU1012443A1 |

| Делитель частоты следования импульсов с программным управлением | 1982 |

|

SU1027831A1 |

| Синусно-косинусный функциональный преобразователь | 1980 |

|

SU888111A1 |

1

Изобретение относится к импульсной технике и может использоваться в устройствах автоматики, вычислительной и измерительной техники.

Известен делитель частоты апедования импульсов с переменным коэффициентом, содержащий 2 п-разрядных счетчика, элемент задержки и п элементов совпадения, причем п-й разряд первого п-разрядного счетчика соединен с входом элемента задержки и входом второго п-разрядного счетчика, а выход элемента задержки со вторыми вхрдами элементов совпадения, первые входы которых соединены с выходами второго п-разрядного счетчика соответственно l.

Недостатке известного устройства является невозможность программирования его работы.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее счетчик импульсов , нулевые входы разрядных ячеек которого соединены с выходами управляемых вентилей, а выходы - через элемент совпадения с управляющим входом переключателя, его другой вход подключен к выходу генератора, а выход - ко входу программного блока и к одному из входов управляемых вентилей, инвертор, вход которого подключен к выходу элемента совпаде- ния, а выход - ко входу ячейки первого разряда счетчика, счетный зход последнего соединен с выходом гене-: ратора, причем выходы программного блока подключены к управляющим входам управляемых вентилей 2.

0

Недостатками известного устройства являются ограниченные функциональные возможности, не обеспечивающие получение выходных импульсов, отличающихся по фазе.

5

Цель изобретения - расширение фиункционсшьных возможностей.

Поставленная цель достигается тем, что в делитель частоты следования импульсов с программным управлением,

0 содержащий счетчик импуль.сов, счетный вход которого подключен к входной шине, элементы совпсщения, первые входы которых соединены с выходами программного блока, а выходы - с вхо5дами управления счетчика импульсов, введен распределитель импульсов, вход которого подключен к выходу счетчика импульсов и вторым входам элементов совпадения, первая группа

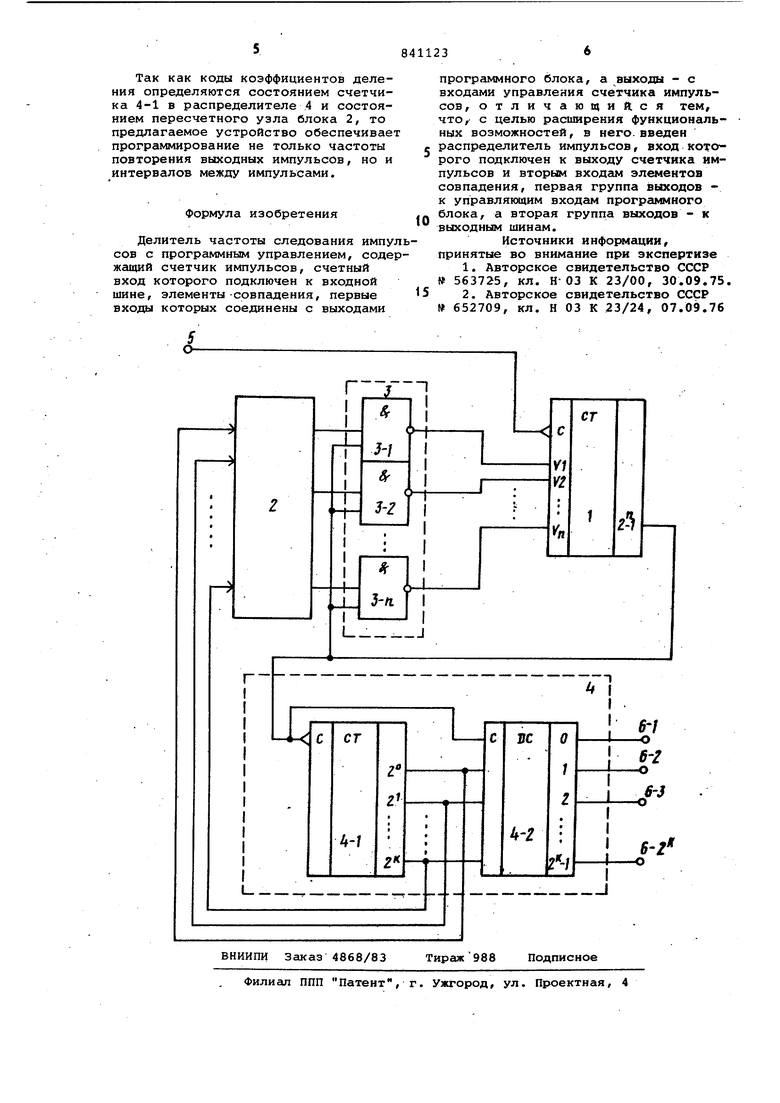

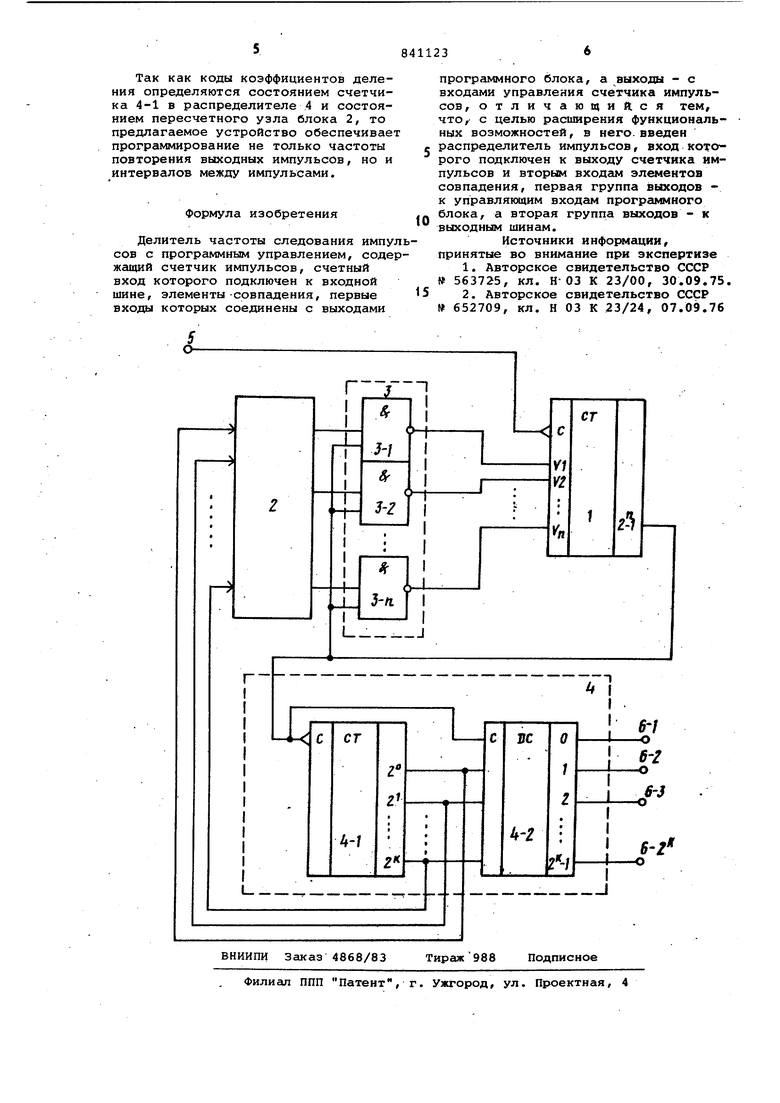

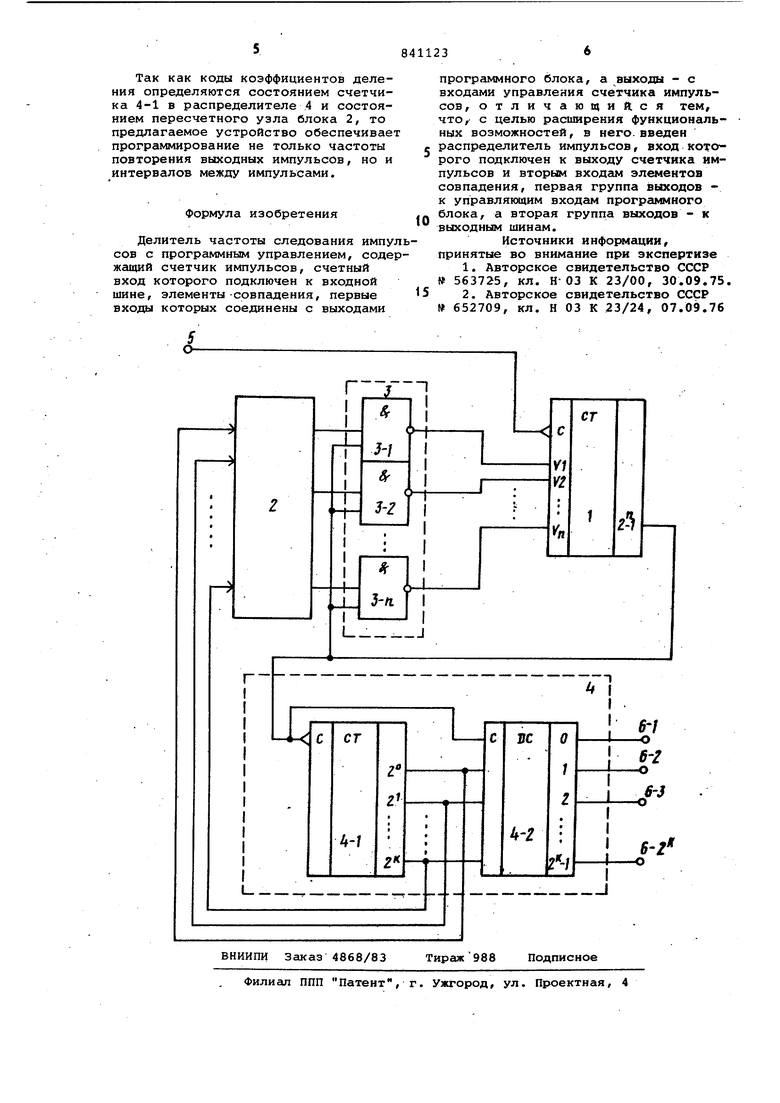

0 выходов - к управляющим входам программного блока, а вторая группа выходов - к йыходным шинам, На чертеже представлена структурная схема устройства. Устройство содержит счетчик 1 импульсов, блок 2 программный, элемент 3-1-3-п И, распределитель 4 импульсо включаняций в себя счетчик 4-1 импуль сов и дешифратор 4-2. Цифрами 5 к6-1-6-2 обозначены входная и выходные шины. Счетчик 1 представляет собой двои ный, счетчик, входы управления которо го размещают срабатывание каждого разряда по счетном / входу при наличии логической 1 на соответствующе входе. При логическом О на входе управления соответствующий разряд не может изменить свое состояние при по даче импульсов на его счетный вход. На выходе переноса () сигнал при нимает значение логической 1 тольк при установке всех разрядов счетчика 1 в состояние единицы. При любых других состояниях счетчика 1 на вы. ходе () сигнал соответствует логическому 1. Распределитель 4 обеспечивает поочередное подключение к шинам 6.-1.-б.-2. В состав распределител 4 входят, например к-разрядный счет чик 4-1 и дешифратор 4-2 со стробир ванием входными импульсами. Счетчик 4-1 изменяет свое состояние по спс1д входных импульсов. Дииифратор 4-2 подключает шины 6-1-6-2 в соответс вии с состояниями счетчика 4-1. Выходы счетчика 4-1, управляющие дешифратором 4-2, являются выходами распределителя 4, управляющими блоком 2. Блок 2 обеспечивает хранение и установку кодов коэффициентов делен в зависимости от состояния первой группы выходов распределителя 4 и о состояния пересчетного узла, входящего в блок 2. Элементы 3-1-3-п И формируют сиг нал логического О на выходе при п даче на оба входа сигнала единицы. При других комбинациях входных сигналов на выходе устанавливается логическая 1. Устройство работает следукнцим образом, В исходном состоянии счетчик 4-1 пересчетный узел блока 2 обнулены. Счетчик 1 срабатывает под воздействием тактовых импульсов с шины 5. Сигнал на выходе счетчика 1 соответ ствует логическому О. Код коэффициента деления на выходах блока 2 устанавливается и соответствует нулевому состоянию счетчика 4-1 и пересчетных узлов блока 2. На выход элементов 3-1-3-п И сигнал соответствует логической 1. Дешифратор 4 подколючает в шине 6-1 вход распределителя 4. В момент заполнения счетчика 1 на выходе появляется сигнал логической 1. Код коэффициента деления через элементы 3-1-3-п И поступает на входы управления счетчика 1. После прихода следующего тактового импульса с шины 5 разряды счетчика 1, на управляемые входы которых поступает логический О, остаются в состоянии единицы, остальные разряды обнуляются, на выходе устанавливается логический О, а на выходах элементов 3-1-3-п И 1. Импульс, сформировавшийся на выходе счетчика 1, проходит на выходную шину 6-Т. На выходах блока 2 устанавливается код коэффициента деления, соответствующий первому состоянию счетчика 4-1 и нулевому состоянию пересчетного узла блока 2. По окончании импульса на выходе счетчика 1 счетчик 4-1 устанавливается в первое состояние, а дешифратор 4-2 подключает вход распределителя 4 к шине 6-2. Интервал времени до следующего момента заполнения счетчика 1 определяется состоянием, в которое сбрасывается счетчик 1 после заполнения, т.е. предыдущим кодом коэффициента деления. После заполнения счетчика 1 снова происходит сброс счетчика 1 в состояние , определяемое кодом блока 2, смена состояния счетчика 4-1, и смена кода коэффициента деления на выходе блока 2, который определяется вторым состоянием счетчика 4-1 и нулевым состоянием пересчетного узла блока 2. Импульс проходит на выходную шину 6-2, после этого дешифратор 4-2 поключает вход распределителя 4 к шине 6-3. Устройство работает аналогичньли образом до момента переполнения счетчика 4-rl. После того, как импульс проходит на шину 6-2, счетчик 4-1 обнуляется, пересчетный узел блока 2 устанавливается 9 первое состояние, а вход распределителя 4 подключается к шине 6-1. Начиная с этого момента, интервалы между импульсами на шинах 6-1-6-2 определяются состояниями счетчика 4-1 и первым-состоянием пересчетного узла блока 2 и т.д. Схема возвращается в исходное состояние в момент переполнения пересчетного узла блока 2. В этот момент пересчетный узел блока 2 и счетчик 4-1 распределителя 4 обнуляется. В дальнейшем цикл работы повторяется. Интервгшы между импульсами, на шинах 6-1...6-2 определяются коэффициентами деления счетчика 1. Количество выходов делителя частоты не превышает число состояний счетчика 4-1. Период импульсов на каждом выходе равен сумме интервалов между импульсёили на шинах 6-1...6-2. Так как коды коэффициентов деления определяются состоянием счетчика 4-1 в распределителе 4 и состоянием пересчетного узла блока 2, то предлагаемое устройство обеспечивае программирование не только частоты повторения выходных импульсов, но и интервалов между импульсами. формула изобретения Делитель частоты следования импу сов с программным управлением, соде жащий счетчик импульсов, счетный вход которого подключен к входной шине, элементы-совпадения, первые входы которых соединены с выходами программного блока, а выходы - с входами управления счетчика импульсов , отличающийся тем, что, с целью расширения функциональных возможностей, в него.введен распределитель импульсов, вход которого подключен к выходу счетчика импульсов и вторым входам элементов совпадения, первая группа выходов к управляющим входам программного блока, а вторая группа выходов - к выходным шинам. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 563725, кл. Н-03 К 23/00, 30.09.75. 2.Авторское свидетельство СССР 652709, кл. Н 03 К 23/24, 07.09.76

Авторы

Даты

1981-06-23—Публикация

1979-09-12—Подача