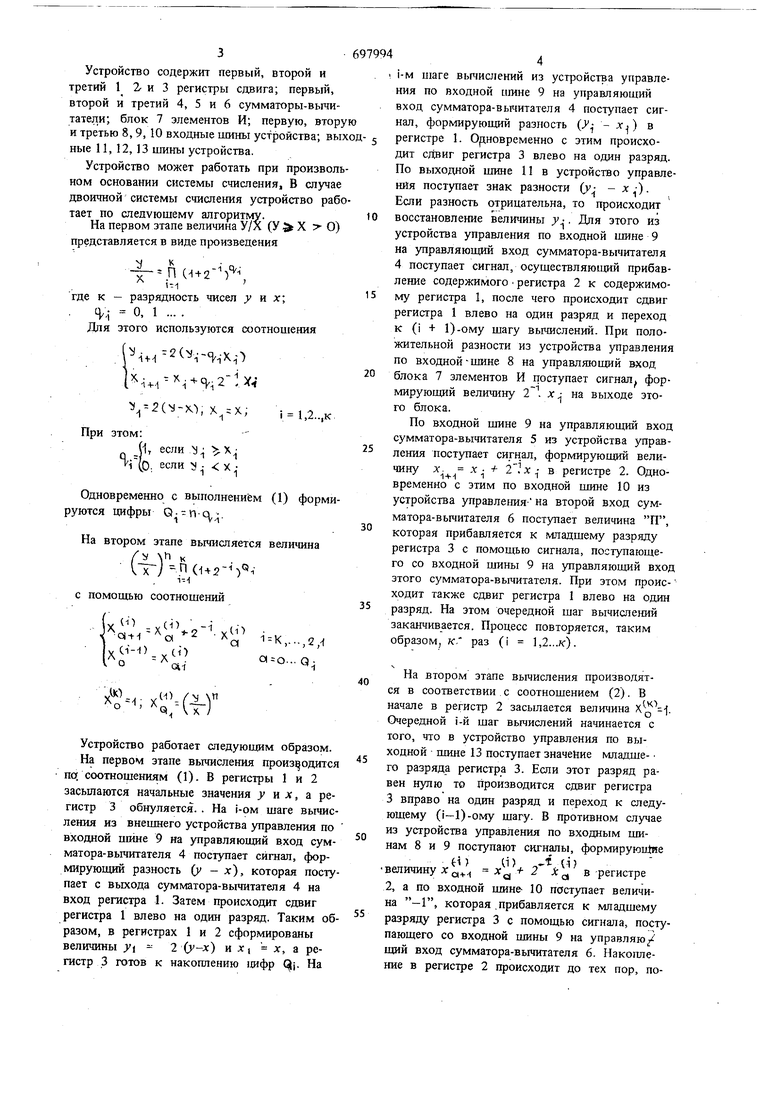

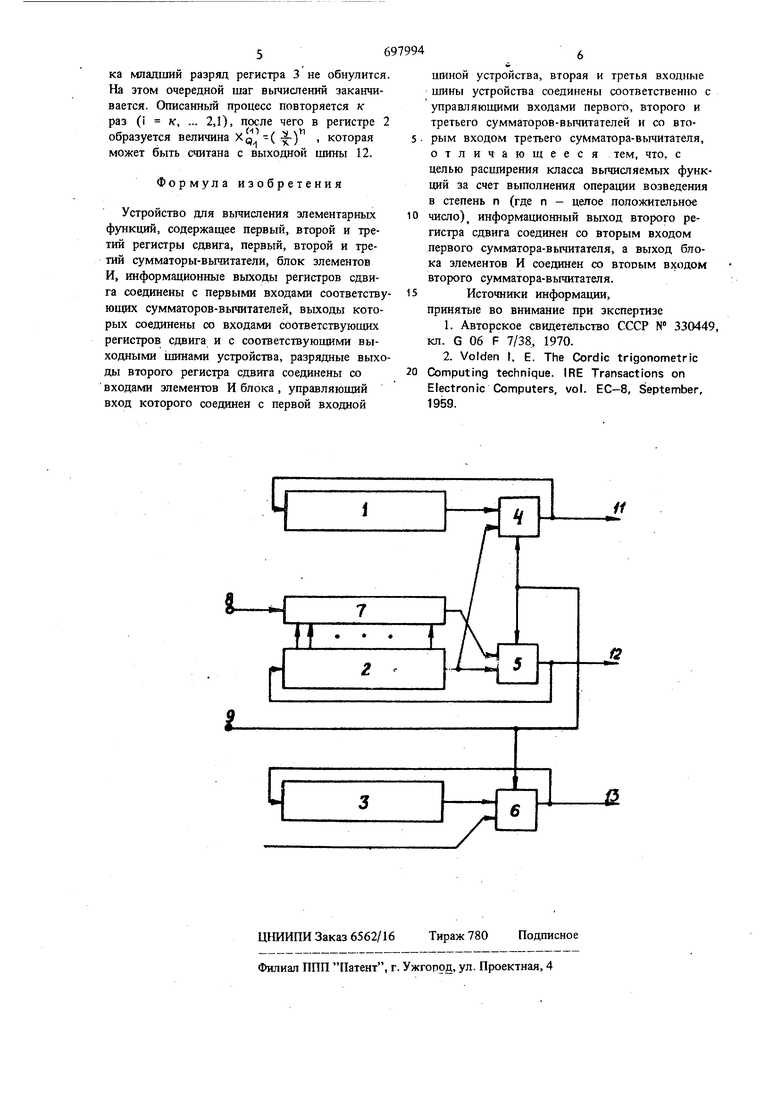

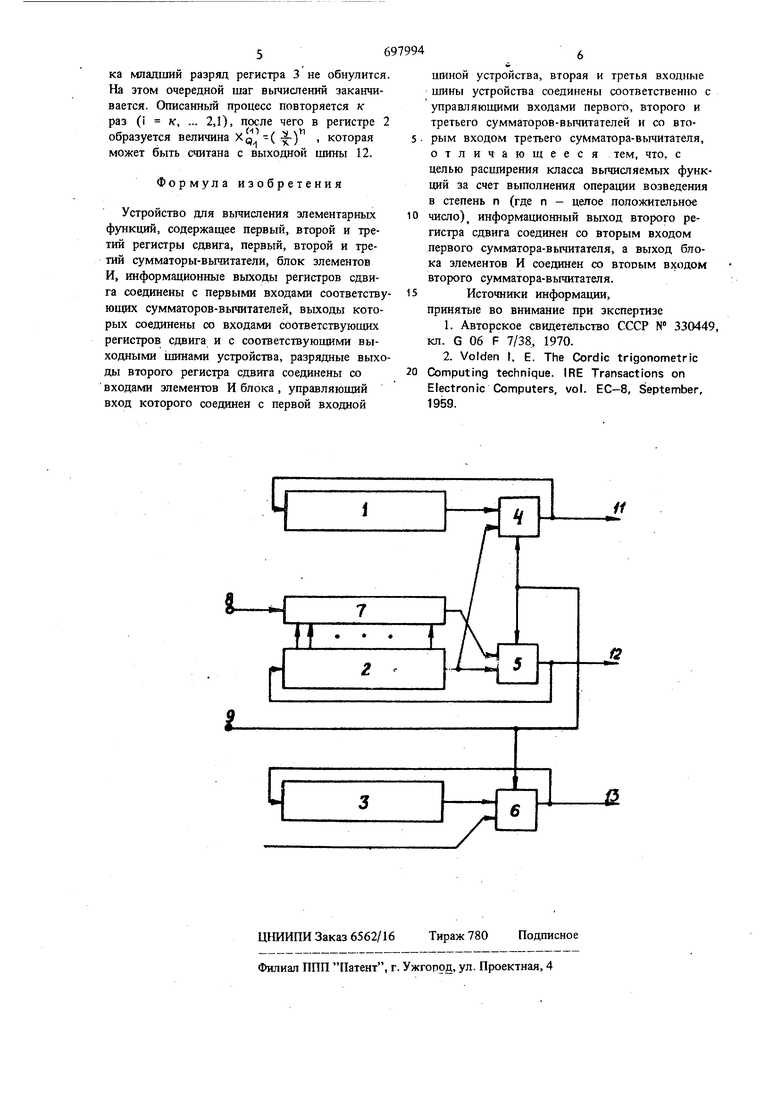

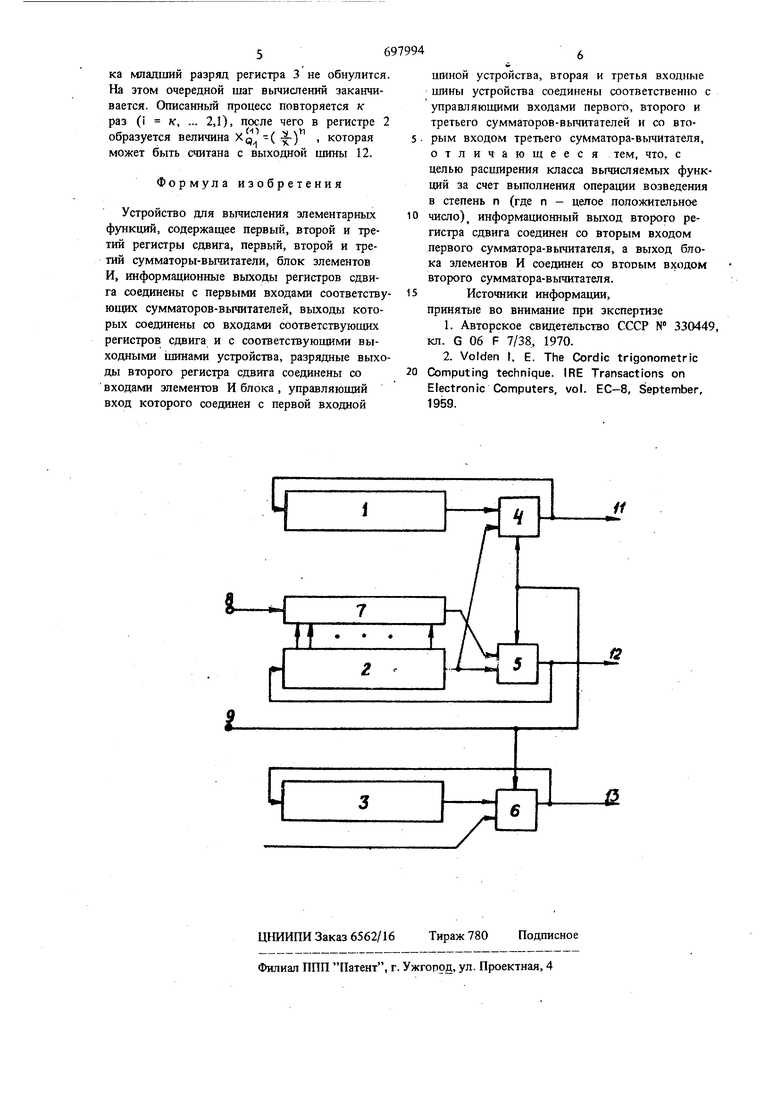

Изобретение относится к вычислительной технике и может быть использовано для аппаратной реализации элементарных функций в ЦВМ. Известны устройства, в которых используется итерационный алгоритм, допускающий аппаратную реализацию элементарных функций Недостатком известного устройства является невозможность возведения в степень. Наиболее близко к предлагаемому по технической сущности устройство для вычисления элементарных функций, содержащее первый, второй и третий регистры сдвита, первый, второй и третий , сумматоры-вычитатели, блок элементов. И, информационные вы ходы регистров сдвига соединены с первыми входами соответствующих сумматоров- вычита телей, выходы . которых соединены со входами соответствующих регистров сдвига и с соответств тощими выходными щинами устрой ства, разрядные выходы второго регистра сдв га соединены со входами элементов И блока т1равляющий вход которого подключен к пе ВОЙ входной щине устройства, вторая и третья входные шины устройства соединены соответственно с управляющи1 о{ входами первого, второго и третьего сумматоров-вьгчитателей и со вторым входом третьего сумматора вычитателя 2. . Однако в наборе базовых функций указанного устройства также отсутствует операция возведения в степень, которая часто встречается при вьтолнении вычислений в ЦВМ. Цель изобретения - рас1Ш1рение класса вычисляемых функций за счет выполнения операции возведения в степень п (где п целое положительное число). Указанная цель достигается тем, что информационный выход второго регистра сдвига соединен со вторым входом первого сумматора-вычитателя, а выход блока элементов И - со вторым входом второго сумматора-вычитателя. На чертеже изображена структ рная схема устройства дня вычисления элементарных функций. 3 Устройство содержит первый, второй и третий 1 2г и 3 регистры сдвига; первый, второй и третий 4, 5 и 6 сумматоры-вычитатели; блок 7 элементов И; первую, втор и третью 8,9, 10 входные шины устройства; вы ные 11, 12, 13 шины устройства. Устройство может работать при произволь ном основании системы счисления, В случае двоичной системы счисления устройство раб тает по следуюшему алгоритму. На нервом этапе величина У/л (У X О) представляется в виде произведения -П ( где к - разрядность чисел у к х , . q.,i О, 1 ... . Для этого используются соотношения u.,(Г,-.К; i i,2..,K, При этом: :(1, если Х Г(р. если х. Одновременно с выполнением (1) форми руются цифры Q.. На втором этапе вьгчисляется величина /i/ n к () -п, (нгЪ с помошью соотношений чДК-.. уИ) /VJ П ° ,-() Устройство работает следующим образом. На первом этапе вычисления производитс по. соотношениям (1). В регистры I и 2 засылаются начальные значения и х, а ре гистр 3 обнуляется. . На i-ом шаге вычис ления из внешнего устройства управления по входной ишне 9 на управляюший вход сум матора-вычитателя 4 поступает сигнал, формирующий разность (у - х), которая пост пает с выхода сумматора-вычитателя 4 на вход регистра 1. Затем происходит сдвиг регистра 1 влево на один разряд. Таким о разом, в регистрах 1 и 2 сформированы величины yt - 2 (у-х} и Xi дг, а регистр 3 готов к накоплению дафр QJ. На i-M шаге вычислений из устройства управления по входной шине 9 на управляющий вход сумматора-вычитателя 4 поступает сигнал, формирующий разность (У: - х) в регистре 1. Одновременно с этим происходит слЕвиг регистра 3 влево на один разряд. По выходной шине 11 в устройство управления поступает знак разности (у - л; ). Если разность отрицательна, то происходит восстановление величины у. Для этого из устройства управления по входной шине 9 на управляющий вход сумматора-вычитателя 4 поступает сигнал, осуществляю1ций прибавление содержимого регистра 2 к содержимому регистра 1, после чего происходит сдвиг регистра 1 влево на один разряд и переход к (i + 1)-ому шагу вычислений. При положительной разности из устройства управления по входной-шине 8 на управляющий вход блока 7 элементов И поступает сигнал формирующий величину 2 х j на выходе этого блока. По входной шине 9 на управляюший вход сумматора-вычитателя 5 из устройства зшравления поступает сигнал, формируюшгий величину X. Х-+ 21 X в регистре 2. Одновременно с этим по входной шине 10 из устройства управле1шя- на второй вход сумматора-вычитателя 6 поступает величина П, которая прибавляется к младшему разряду регистра 3 с помощью сигнала, поступающего со входной шины 9 на управляющий вход этого сумматора-вычитателя. При этом происходит также сдвиг регистра I влево на один разряд. На этом очередной шаг вычислений заканчивается. Процесс повторяется, таким образом, к раз (i 1,2...к). На втором этапе вычисления производятся в соответствии с соотношением (2). В начале в регистр 2 засылается величина -. Очередной i-й шаг вычислений начинается с того, что в устройство управления по выходной шине 13 поступает значение младше- го разряда регистра 3. Если этот разряд равен нулю то производится сдвиг регистра 3 вправо на один разряд и переход к следующему (i-1)-ому шагу. В противном случае из устройства управления по входным шинам 8 и 9 поступают сигналы, формирующее величину лг, t регистре 2, а по входной шине- 10 поступает величина -1, которая . прибавляется к младшему разряду регистра 3 с помощью сигнала, поступающего со входной шины 9 на управляю/ щий вход сумматора-вычитателя б. Накопление в регистре 2 происходит до тех пор, пока младший разряд регистра 3 не обнулится. На этом очередной шаг вычислений заканчивается. Описанный процесс повторяется к раз (i к, ... 2,1), после чего в регистре 2 образуется величина q ( которая может быть считана с выходной шины 12.

Формула изобретения

Устройство для вычисления элементарных функций, содержащее первый, второй и третий регистры сдвига, первый, второй и третий сумматоры-вычитатели, блок элементов И, информационные выходы регистров сдвига соединены с первыми входами соответствующих сумматоров-вычитателей, выходы которых соединены со входами соответствующих регистров сдвига и с соответствующими выходными щинами устройства, разрядные выходы второго регистра сдвига соединены со входами элементов И блока , управляющий вход которого соединен с первой входной

щиной устройства, вторая и третья входные щины устройства соединены соответственно с управляющими входами первого, второго и третьего сумматоров-вычитателей и со вторым входом третьего сумматора-вычитателя, отличающееся тем, что, с целью расширения класса вычисляемых функций за счет выполнения операции возведения в степень п (где п - целое положительное

число) информационный выход второго регистра сдвига соединен со вторым входом первого cyMiviaTOpa-вычитателя, а выход блока элементов И соединен со вторым входом второго сумматора-вычитателя.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 330449, кл. G 06 F 7/38, 1970.

2.Volden I. Е. The Cordic trigonometric Computing technique. IRE Transactions on

Electronic Computers, vol. EC-8, September, 1959.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ | 2013 |

|

RU2541197C1 |

| Устройство для вычисления элементарных функций | 1973 |

|

SU546890A1 |

| Устройство для извлечения квадратного корня | 1977 |

|

SU640290A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления экспоненты | 1978 |

|

SU798857A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Генератор числовых функций | 1974 |

|

SU533922A1 |

Авторы

Даты

1979-11-15—Публикация

1976-12-10—Подача