,-

1 .13

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре, осуществляющей вычисление элементарных функций с помощью итерационных алгоритмов.

Цель изобретения - расширение класса решаемых задач за счет выполнения операции поворота вектора и преобразования систем координат.

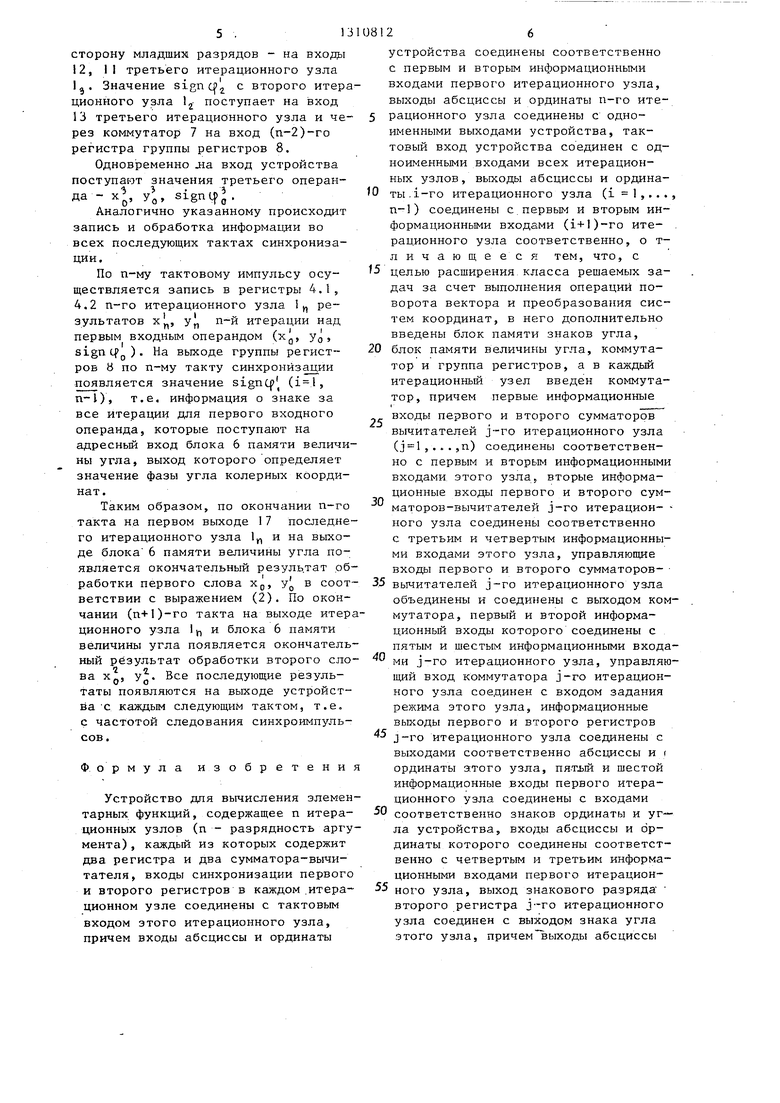

На чертеже представлена функцио- нальная схема устройства.

Устройство содержит итерационные узлы 1 (i 1,...,п), каждый из которых содержит первый и второй сумма- торы-вычитатели 2.1 и 2.2, коммутато 3, первый и второй регистры 4.1 и 4.1, блок 5 памяти знаков узла, блок 6 памяти величины угла, коммутатор 7, группу регистров 8.

Каждый итерационный узел содержит информационные входы соответственно с первого по шестой 9-14, вход 15 задания режима, тактовый вход 16.

В режиме поворота векторов на вхо устройства подаются три информацион ных слова Xjj, у, и Cf, и signqj. В этом режиме устройство реализует следующие функции

х;, х -(signcpi) у; 2 ;

Уи, У +(signq ;) .x. ; (1)

(signq ;)-arctg 2 .

На вход задания режима (Упр. 1) поступает сигнал режима поворота вектора (1), обеспечивающий прохождение через коммутатор 7 информации sign ср, от блока 5 знаков угла памяти и прохождение signcf, через коммутатор 3 итерационных узлов 1; . На вход блока 5 памяти знаков угла поступает значение углас на который необходимо повернуть вектор XQ, Ур. Значение угла (jj служит адресом, по которому выбираются из блока 5 памяти знаков угла предвари тел.ьно рассчитанные коды sign ср, , i(l,n), предназначенные дпя управления сумматорами-вычитател;ями 2.1, 2.2, работающими в режиме сложения либо в режиме вычитания в зависимости от поступающего кода управления. На каждый из итерационных узлов 1; поступает соответствующее значение кода в определенный момент в зависимости от номера узла 1; . Значения Хд и УО первого операнда поступают соответственно на входы 9, 12 и 10,

5

81

О

-

0

0

35

0

45

0

55

22

II, а значения signqig - на вход 14 первого итерационного узла 1,.

При поступлении первого тактового импульса на синхронизирующий вход (Упр.2) осуществляется запись в регистры 4.1, 4.2 первого итерационного узла 1, результатов , у, первого итерационного шага над первым входным операндом (х, ). Этим тактовым импульсом с коммутатора 7 код signqi для первого входного . операнда записывается в первый разряд всех регистров группы регистров 8. При этом на вход 14 второго итерационного узла с вькода первого регистра группы регистров 8 поступает значение sign ср .

Вычисленные, значения х, у, с регистров 4.1, 4.2 (выход 17, 18) первого итерационного узла 1( поступают на входы 9, 11 и со сдвигом на один разряд в сторону младших разрядов на входы 12, 10 второго итерационного узла Ig .

Одновременно на вход устройства поступают значения второго операн - да - Хд, УО, cf/ , sign .

По второму тактовому импульсу осуп1ествляется запись в регистры 4.1, 4.2 второго итерационного узла 1 результатов xj, у действий второй итерации над первым входным операндом (х, yj,, CfJ,), а в регистры 4.1, 4.2 первого итерационного узла - результатов х, у первой итерации соответственно от второго входного операнда (х, ) Одновременно в группе регистров 8 значение кода signq - с первого разряда переписывается во второй, а в первый разряд группы регистров 8 записывается значение кода signtf , поступающего через коммутатор 7 от блока 5 знаков угла. При этом на . вход 14 третьего итерационного узла Ц поступает значение sign ($„, а на вход 14 второго итерацио нного узла Ig значение sign ср с выхода группы регистров 8. Вычисленные значения Х|5 У, с регистров 4.1, 4.2 после первой итерации поступают на входы 9, 10 и со сдвигом на один разряд в сторону разрядов - на входы 12, 11 второго итерационного уз- ла 1л. Вычисленные значения х„, у1

1л . iJDiHiniit:iint)ie cJnd cnUTi -л.-, уС регистров 4.1, 4.2 второго итерационного узла Ц поступают на входы 9, 10 и со сдвигом на два разряда в

3 13

сторону младших разрядов - на входы 12, 11 третьего итерационного узла 1. А на вход устройства поступают значения третьего операнда - х,

УО sigi M-o-

Аналогично указанному происходит

запись и обработка информации во всех последующих тактах синхронизации.

По п-му тактовому импульсу осу- ществляется запись в регистры Д п-го итерационного узла 1 результатов х|,, у п-й итерации, соответствующих повороту первого входного операнда (XQ, у в), на угол .

Таким образом, по окончании п-го такта на выходах последнего итерационного узла появляется окончательный результат обработки первого .1 ,.

слова X

о о

в соответствии с

выражением (1). По окончаний (п+1)- го такта на входах итерационного узла 1 появляется окончательный результат обработки второго слова х, . Все последующие результаты появляются на выходе устройства с кажда1М следующим тактом, т.е. с частотой следования синхроимпульсов, поступающих на синхронизирующий вход устройства (Упр.2).

В режиме преобразования координат из прямоугольных в полярные на вход задания режима устройства (Упр.1) поступает сигнал О.

В этом режиме устройство реали- зует следующие функции:

-- x; + (sign у; )-у ;

1+1

У;м У;-(з1§п у; ) Х 2 ; tf; + i q ;+(sign yj) arctg-2 .

Сигнал Упр.1, поступая на управляющий вход коммутатора 1, открывает прохождение сигналов с выходов I9 итерационных узлов Ij на вход группы регистров 8.

Поступая на вход коммутаторов 3 итерационных узлов, сигнал Упр. обеспечивает прохождение значения signCf - на входы сумматоров вычитате- лей 2.1, 2,2 итерационных узлов I; .

На вход устройства в этом режиме поступают значения х, у, signtf,

позволяющие вычислить угол if и т|х +У

Значения sign у;, i (1,п) предназначены для управления сумматорами-вычи- тателями 2.1, 2.2, работающими в ре108

5

1015

20

25 30

35

40

45 50

,

Г 5

-124

жиме сложения либо в режиме вычитания в зависимости от поступающего кода управления согласно формуле (2). Значения xj,, у и sipnq перво го операнда поступают соответственно на входы 9, 12, 10, 11 и 13 первого итерационного узла I(.

При поступлении первого тактового импульса на синхронизирующий вход (Упр.2) осуществляется запись в регистры A.I, 4.2 первого итерационного узла I, результатов х, у, первой итерации над первым входным операндом (х, Уд). При этом вычисленные значения х, у, с регистров 4.1, 4.2 (выход 17, 18) первого итерационного узла 1, поступают на входы 9, 10 и со сдвигом на один разряд в сторону младших разрядов - на входы 12, 11 второго итерационного узла 1. Значение (выход 19) первого итерационного узла 1, поступает на вход 13 второго итерационного узла и через коммутатор 7 на вход (n-l)-ro регистра группы регистров В.

На вход устройства поступают значения второго операнда - х, -у, sign у.

По второму тактовому импульсу осу- щертвляется запись в регистры 4.1, 4.2 второго итерационного узла Ig результатов х, у второй итерации над первым входным операндом (х, у) а в регистры 4.1, 4.2 первого итерационного узла 1, - результатов х, у первой итерации над вторьм входным операндом (х, у, sip;nu)|).

Одновременно в группе регистров. 8 значение sign , поступающее через коммутатор 7, записывается в (п-1)-й регистр. При этом вычисленные значения у, с регистров 4.1, 4.2 первого итерационного узла Ц поступают на входы 9, 10 и со сдвигом на один разряд в сторону младших разрядов - на входы 12, II второго итерационного узла Ij. Значение signcf с второго регистра 4,2 первого итерационного узла 1| поступает на вход 13 второго итерационного блока и через коммутатор 7 на вход (n-l)-ro регистра группы регистров 8, а значение signtf , записанное в предыдущем такте, переписывается при этом во второй разряд этого же регистра. Вычисленные значения х , у с регистров 4.1, 4.2 второго итерационного узла Ij поступают на входы 9, 10 и со сдвигом на два разряда в

сторону младших разрядов - на входы 12, И третьего итерационного узла Ij. Значение signq) с второго итерационного узла Ij- поступает на вход 13 третьего итерационного узла и через коммутатор 7 на вход (п-2)-го регистра группы регистров 8.

Одновременно ла вход устройства поступают значения третьего операнД - 0 0 signtp.

Аналогично указанному происходит запись и обработка информапди во всех последующих тактах синхронизации.

По п-му тактовому импульсу осуществляется запись в регистры 4.1, 4.2 п-го итерационного узла 1 результатов х, yj, п-й итерации над первым входным операндом (xj,, у, signcpp). На выходе группы регистров 8 по п-му такту синхронизации появляется значение signcp (, n-l), т.е. информация о знаке за все итерации для первого входного операнда, которые поступают на адресньм вход блока 6 памяти величины угла, выход которого определяет значение фазы угла колерных координат.

Таким образом, по окончании п-го такта на первом выходе 17 последнего итерационного узла 1 и на выходе блока 6 памяти величины угла появляется окончательный результат обработки первого слова х, у в соответствии с выражением (2). По окончании (п+1)-го такта на выходе итерционного узла 1 и блока 6 памяти величины угла появляется окончательный результат обработки второго слова X

О

Все последующие результаты появляются на выходе устройства с каждым следующим тактом, т.е. с частотой следования синхроимпульсов.

Формула изобретения

Устройство для вычисления элементарных функций, содержащее п итерационных узлов (п - разрядность аргумента) , каждый из которых содержит два регистра и два сумматора-вычи- тателя, входы синхронизации первого и второго регистров в каждом .итерационном узле соединены с тактовым входом этого итерационного узла, причем входы абсциссы и ординаты

устроиства соединены соответственно с первым и вторым информационными входами первого итерационного узла, выходы абсциссы и ординаты п-го итерационного узла соединены с одноименными выходами устройства, тактовый вход устройства соединен с одноименными входами всех итерационных узлов, выходы абсциссы и ординаты.1-го итерационного узла (,..., п-1) соединены с.первым и вторым информационными входами (i+l)-ro ите- . рационного узла соответственно, о т- личающееся тем, что, с

целью расширения.класса решаемых задач за счет выполнения операций поворота вектора и преобразования систем координат, в него дополнительно введены блок памяти знаков угла,

блок памяти величины угла, коммутатор и группа регистров, а в каждый итерационньм узел введен коммутатор, причем первые информационные

5

0

5

0

5

0

5

входы первого и второго сумматоров вычитателей итерационного узла (,...,n) соединены соответственно с первым и вторым информационными входами этого узла, вторые информационные входы первого и второго сум- маторов-вычитателей j-ro итерацион- - ного узла соединены соответственно с третьим и четвертым информационными входами этого узла, управляющие входы первого и второго сумматоров- вычитателей j-ro итерационного узла объединены и соединены с выходом коммутатора, первый и второй информа- ционньм входы которого соединены с пятым и шестым информационными входами j-ro итерационного узла, управляющий вход коммутатора j-ro итерационного узла соединен с входом задания режима этого узла, информационные вькоды первого и второго регистров J-ro итерационного узла соединены с выходами соответственно абсциссы и г ординаты этого узла, пятьй и шестой информационные .входы первого итерационного узла соединены с входами соответственно знаков ординаты и угла устройства, входы абсциссы и ординаты которого соединены соответственно с четвертым и третьим информа- ционньдан входами первого итерационного узла, выход знакового разряда второго регистра j-ro итерационного узла соединен с выходо.м знака угла этого узла, причем Ъыходы абсциссы

713

и ординаты i-ro итерационного узла

(i 1п-1) соединены со сдвигом

иа i разрядов в сторону младших разрядов с четвертью и третьим информационными входами (i+l)-ro итерацион- ного узла соответственно, выход знака угла i-ro итерационного узла соединен с пятым информационным входом (i+l)-rp итерационного узла, вход величины угла устройства соединен с адресным входом блока памяти знаков угла, выходы которого соединены с информационными входами первой группы коммутатора, информационные входы второй группы которого соединены с выходами знака угла соответствующих

Редактор М.Дылын

Составитель С.Куликов

Техред;Л.Опейник Корректор Г.Решетник

Заказ 1892/45 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

28

итерационных узлов, j-й выход коммутатора соединен с.входом первого разряда j-ro регистра группы, выход j-ro разряда j-ro регистра группы соединен с шестым информационным входом j-TO итерационного узла, строби- рующие входы регистров группы соединены с тактовым входом устройства, вход задания режима устройства соединен с одноименными входами всех итерационных узлов и с управляющим входом коммутатора, выход j-ro разряда j-ro регистра группы соединен с J-ii, адресным входом блока памяти величины угла, выход которого является выходом фазы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1982 |

|

SU1086437A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1476462A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Генератор систем функций Аристова | 1989 |

|

SU1746373A1 |

Изобретение относится к области вычислительной техники и предназначено для вычисления ряда элементарных функций с помощью итерадарн- ных алгоритмов Волдера. Целью изобретения является расширение класса решаемых задач за счет выполнения опера щ1й поворота вектора и преобразования систем координат. Устройство содержит итерационные узлы lu (i 1,...,n), содержащие сумматоры- вычитатели 2.1, 2.2, коммутатор 3 и регистры 4.1, 4.2, блоки памяти 5 и 6 соответственно знаков и величины угла, коммутатор 7-, группу регистров 8. Вычисления могут производиться для различных режимов, задаваемых по входу задания режима устройства . Вычисления организованы конвейерным способом, причем в каждом итерационном узле реализуется одна итерация рекуррентным соотношением алгоритма Волдера. 1 ил. (Л Сдбиг ног Кп

| Вычислительное устройство | 1978 |

|

SU687448A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство дляРЕАлизАции АлгОРиТМА ВОлдЕРА | 1979 |

|

SU813423A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-02—Подача