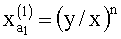

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и в автоматизированных системах научных исследований, в частности при вычислении функции вида (y/x)n.

Известны устройства для вычисления элементарных функций [А.с. 330449 СССР Устройство для получения частного, 1972 г.], а также [А.с. 1755650 A1 Устройство для вычисления функций, 1994 г.].

Недостатком первого является невозможность возведения в степень отношения двух величин (т.е. частного двух чисел), а недостатком второго - невозможность нахождения частного и возведения его в степень одновременно (т.е. за время одной операции).

Наиболее близким по технической сущности является устройство для вычисления элементарных функций [А.с. 697994 СССР Устройство для вычисления элементарных функций, 1979 г.], служащее для возведения в степень n частного (n - натуральное число).

Оно содержит первый, второй и третий регистры сдвига, первый, второй и третий сумматоры-вычитатели, блок элементов И, информационные выходы регистров сдвига соединены с первыми входами одноименных сумматоров-вычитателей, выходы которых соединены со входами одноименных регистров сдвига и с одноименными выходными шинами устройства, разрядные выходы второго регистра сдвига соединены со входами элементов И блока, управляющий вход которого соединен с первой входной шиной устройства, вторая и третья входные шины устройства соединены соответственно с управляющими входами первого, второго и третьего сумматоров-вычитателей и со вторым входом третьего сумматора-вычитателя.

Информационный выход второго регистра сдвига соединен со вторым входом первого сумматора-вычитателя, а выход блока элементов И соединен со вторым входом второго сумматора-вычитателя. Кроме того, третья входная шина 10 соединена с входом третьего сумматора-вычитателя 6.

Недостатком этого устройства является низкое быстродействие.

Задачей настоящего изобретения является повышение технической эффективности.

Технический результат настоящего изобретения - повышенное быстродействие устройства при вычислении натуральной степени отношения (частного) двух величин без снижения точности вычисления.

Поставленная задача решена предложенным устройством для вычисления элементарных функций, которое содержит первый, второй и третий регистры сдвига, первый, второй и третий сумматоры-вычитатели, блок элементов И, информационные выходы регистров сдвига соединены с первыми входами одноименных сумматоров-вычитателей, выходы которых соединены со входами одноименных регистров сдвига и с одноименными выходными шинами устройства, разрядные выходы второго регистра сдвига соединены со входами элементов И блока, управляющий вход которого соединен с первой входной шиной устройства, вторая и третья входные шины устройства соединены соответственно с управляющими входами первого, второго и третьего сумматоров-вычитателей и со вторым входом третьего сумматора-вычитателя.

Информационный выход второго регистра сдвига соединен со вторым входом первого сумматора-вычитателя, а выход блока элементов И соединен со вторым входом второго сумматора-вычитателя. Кроме того, третья входная шина 10 соединена с входом третьего сумматора-вычитателя 6. Кроме того, в устройство входит блок ограничения числа итераций, состоящий из четвертого регистра, счетчика итераций, генератора серии импульсов и четвертого сумматора-вычитателя, выход которого образует дополнительную четвертую выходную шину, а его информационный и управляющий входы связаны с выходами счетчика итераций и генератора серии импульсов, соответственно, входы которых, в свою очередь, связаны со второй входной шиной и с первой выходной шиной, соответственно.

Введение дополнительного блока ограничения числа итераций сокращает число итераций в несколько раз, что экономит время одного вычисления элементарной функции и, таким образом, ускоряет время выдачи полученного результата без снижения его точности. Это является новым техническим решением в технике цифрового функционального преобразования, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить в несколько раз быстродействие вычисления элементарных функций, в частности, вида (y/x)n.

Предложенное устройство для вычисления элементарных функций вида (y/x)n промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральные логические микросхемы).

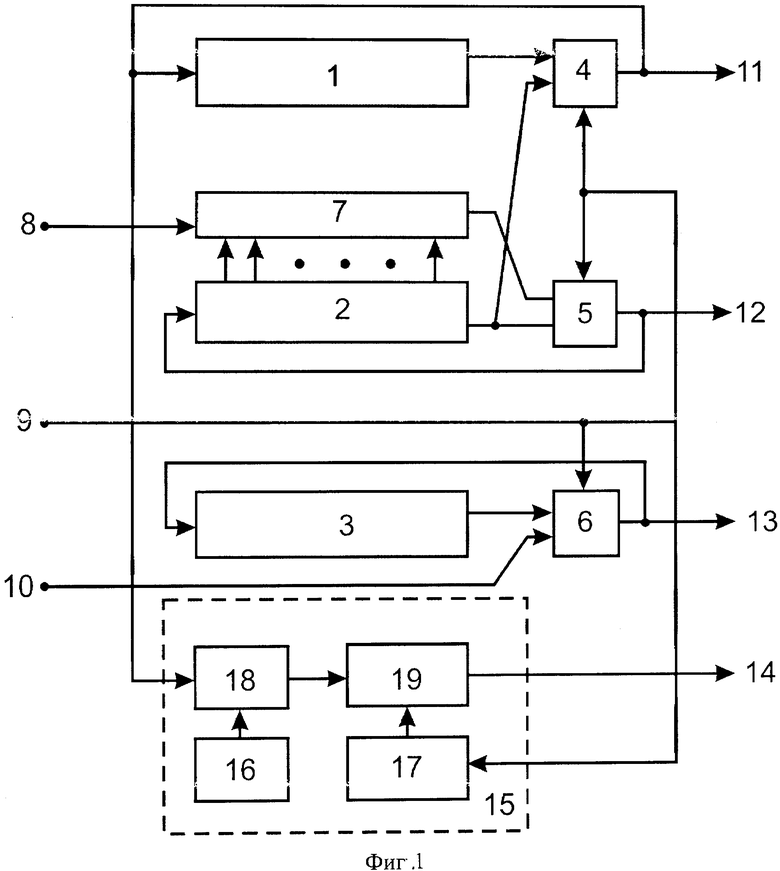

На фиг.1 приведена структурная схема устройства для вычисления элементарных функций.

Заявленное устройство содержит первый, второй и третий 1, 2 и 3 регистры сдвига; первый, второй и третий 4, 5 и 6 сумматоры-вычитатели; блок 7 элементов И; первую, вторую и третью 8, 9, 10 входные шины устройства; первую, вторую, третью и четвертую 11, 12, 13, 14 выходные шины.

Для повышения быстродействия устройства используется блок ограничения числа итераций 15, содержащий четвертый регистр 16, счетчик итераций 17, генератор серии импульсов 18 и четвертый сумматор-вычитатель 19, выход которого соединен с четвертой выходной шиной 14.

При этом информационные выходы регистров сдвигов 1, 2, 3 соединены с первыми выходами одноименных сумматоров-вычитателей 4, 5, 6, выходы которых соединены со входами одноименных регистров сдвига 1, 2, 3 и одноименными выходными шинами 11, 12, 13 устройства, разрядные выходы второго регистра сдвига 2 соединены со входом блока элементов И 7, управляющий вход которого соединен с первой входной шиной 8 устройства, вторая 9 и третья 10 входные шины соединены соответственно с управляющими входами первого 4, второго 5 и третьего 6 сумматоров-вычитателей.

Информационный выход второго регистра сдвига 2 соединен со вторым входом первого сумматора-вычитателя 4, а выход блока элементов И 7 соединен со входом второго сумматора-вычитателя 5, кроме того, третья входная шина 10 соединена со входом третьего сумматора-вычитателя 6.

Выход блока ограничения числа итераций 15 является четвертой выходной шиной 14 устройства. В самом блоке 15 организованы следующие связи: информационный и управляющий входы четвертого сумматора-вычитателя 19 связаны с выходами счетчика итераций 17 и генератора серии импульсов 18, соответственно, входы которых, в свою очередь, связаны со второй входной шиной 9 и с первой выходной шиной 11, соответственно.

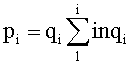

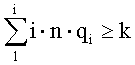

Достоверность достижения поставленной цели изобретения - повышение технической эффективности устройства - подтверждается математическим обоснованием того факта, что окончательный результат вычислений сформирован намного раньше, чем заканчиваются k итераций, где k - разрядность чисел y и x. Это происходит из-за того, что уже после p сдвигов (p<k) содержимое второго регистра сдвига 2 больше не изменяется, так как к нему подсуммируется нуль. А результат вычисления функции (y/x)n уже содержится во втором регистре сдвига 2. Математически установлено, что

Математическое моделирование показало, что si>k уже для итераций с номером i, в два-три раза менее, чем разрядность k второго регистра сдвига 2.

В качестве примера приведена таблица 1 с результатами хода итераций для контрольного примера y=994 и x=697 (взяты из номера а.с. - прототипа)

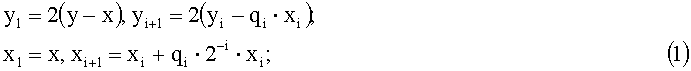

Устройство может работать при произвольном основании системы счисления. В случае двоичной системы счисления оно работает по следующему алгоритму.

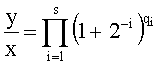

На первом этапе величина y/x (y>x>0) представляется в виде произведения

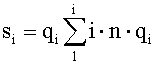

Для этого используются итерационные соотношения:

где i - номер итерации, равный 1, 2, …, s.

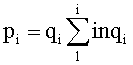

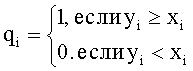

Одновременно с выполнением действий на первом этапе формируются величины Qi=n·qi. На втором этапе вычисляется результат (y/x)n с помощью итерационных соотношений:

Тогда в конце цикла получают

Устройство работает следующим образом. На первом этапе вычисления производятся по соотношениям (1). В регистры 1 и 2 засылаются начальные значения y и x, а регистр 3, счетчик итераций 17 и сумматор-вычитатель 19 обнуляются. А в сумматор-вычитатель 19 заносится число n - степень в формуле. В регистр 16 также заносится степень n. На первой итерации вычисления из внешнего устройства управления по входной шине 9 на управляющий вход сумматора-вычитателя 4 поступает сигнал, формирующий разность (y-x), которая поступает с выхода сумматора-вычитателя 4 на вход регистра 1. Затем происходит сдвиг регистра 1 влево на один разряд. Таким образом, в регистрах 1 и 2 сформируются величины y1=2(y-x) и xi=x, регистр 3 готов к накоплению цифр Qi. Кроме того, сигнал на входной шине 9 вычитает 1 из содержимого сумматора-вычитателя 19 (и так на каждой итерации).

На i-й итерации вычислений из устройства управления поступает сигнал, формирующий разность (yi-xi) в регистре 1.

Одновременно с этим на i-й итерации происходит сдвиг регистра 3 влево на один разряд. По выходной шине 11 в устройство управления поступает знак разности (yi-xi). Если разность отрицательна, то происходит восстановление величины yi. Для этого из устройства управления по выходной шине 9 на управляющий вход сумматора-вычитателя 4 поступает сигнал, осуществляющий прибавление содержимого регистра 2 к содержимому регистра 1, после чего происходит сдвиг регистра 1 влево на один разряд и переход к (i+1)-й итерации. При положительной разности из устройства управления по входной шине 8 на управляющий вход блока 7 элементов И поступает сигнал, формирующий величину 2-i·xi на выходе этого блока. Одновременно формируется сигнал qi=1. Он поступает на генератор серии из n импульсов (n задается регистром 16), которые вычитают n раз номер i-й итерации из содержимого сумматора-вычитателя 19. В дальнейшем, когда изменится знаковый разряд этого сумматора-вычитателя с 0 на 1, будет выдан сигнал по выходной шине 14 в устройство управления на прекращения итераций.

По входной шине 9 на управляющий вход сумматора-вычислителя 5 из устройства управления поступает сигнал, формирующий величину xi+1=xi+2-i·xi, в регистре 2. Одновременно с этим по входной шине 10 из устройства управления на второй вход сумматора-вычислителя 6 поступает величина "n", которая прибавляется к младшему разряду регистра 3 с помощью сигнала, поступающего с входной шины 9 на управляющий вход этого сумматора-вычитателя. При этом происходит также сдвиг регистра 1 влево на один разряд. На этом очередная итерация заканчивается. Процесс повторяется, таким образом, s раз (i=1, 2, …, s). Он прерывается досрочно по сравнению с прототипом (s<k) сигналом из блока ограничения числа итераций 15 по выходной шине 14 в устройство управления.

На втором этапе вычисления производятся в соответствии с соотношениями (2). Сначала в регистр 2 засылается величина

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Цифровой функциональный преобразователь | 2017 |

|

RU2642381C1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Функциональный преобразователь | 2017 |

|

RU2649955C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ M-МЕРНОГО ВЕКТОРА | 1995 |

|

RU2080650C1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2565010C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и автоматизированных системах научных исследований, в частности, при вычислении функции вида (y/x)n. Техническим результатом является повышение быстродействия устройства. Устройство содержит сумматоры-вычитатели, регистры сдвига, блок элементов И, блок ограничения числа итераций, включающий сумматор-вычитатель, счетчик итераций, регистр и генератор серии импульсов. 1 ил., 1 табл.

Устройство для вычисления элементарной функции (y/x)n, содержащее первый, второй и третий регистры сдвига, первый, второй и третий сумматоры-вычитатели, блок элементов И, информационные выходы регистров сдвига соединены с первыми входами соответствующих сумматоров-вычитателей, выходы которых соединены со входами соответствующих регистров сдвига и с соответствующими выходными шинами устройства, разрядные выходы второго регистра сдвига соединены со входами элементов И блока, управляющий вход которого соединен с первой входной шиной устройства, вторая и третья входные шины устройства соединены соответственно с управляющими входами первого, второго и третьего сумматоров-вычитателей и со вторым входом третьего сумматора-вычитателя, информационный выход второго регистра сдвига соединен со вторым входом первого сумматора-вычитателя, выход блока элементов И соединен со вторым входом второго сумматора-вычитателя, а третья входная шина соединена со входом третьего сумматора-вычитателя, отличающееся тем, что в устройство дополнительно введен блок ограничения числа итераций, состоящий из четвертого регистра, счетчика итераций, генератора серии импульсов, четвертого сумматора-вычитателя, выход которого образует дополнительную четвертую выходную шину, а его информационный и управляющий входы связаны с выходами счетчика итераций и генератора серии импульсов, соответственно, входы которых, в свою очередь, связаны со второй входной шиной и с первой выходной шиной, соответственно, кроме того, выход четвертого регистра связан с другим входом генератора серии импульсов.

| Устройство для вычисления элементарных функций | 1976 |

|

SU697994A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| JP 6175824 A, 24.06.1994 | |||

| US 6108682 A, 22.08.2000 | |||

| JP 5100762 A, 23.04.1993 | |||

Авторы

Даты

2015-02-10—Публикация

2013-07-11—Подача