1

Изобретение относится к области вычислительной техники и может найти ирименение при создании цифровых вычислительных машин, выполняющих вычисление элементарных функций аппаратными средствами.

Известно устройство для вычисления элементарных функций 1, содержащее блок унравления и блок односторонней памяти. Недостатком известного устройства является низкое быстродействие при вычислении функции Sina и Coscc.

Наиболее близким к предлагаемому изобретению является устройство для вычисления элементарных функций 2, содержащее блок управления, счетчик шагов, регистры, сумматор - вычитатель и блок односторонней памяти.

Недостатком такого устройства является отсутствие возможности непосредственного вычисления функций , Since и Cosa, как базовых. Это ириводит к необходимости составления соответствующих программ для указанных функций, что требует значительных затрат времени и оборудования при аипаратпой реализации программ.

Целью изобретения является создание устройства для непосредственного вычисления функций К- , Sina и Cosa, как базовых т. е. расширение функциональных воз.можностей устройства. При этом все функции вычисляются по единой инерционной схеме, что позволяет уменьшить аппаратурные затраты в устройстве управления и увеличить быстродействие устройства.

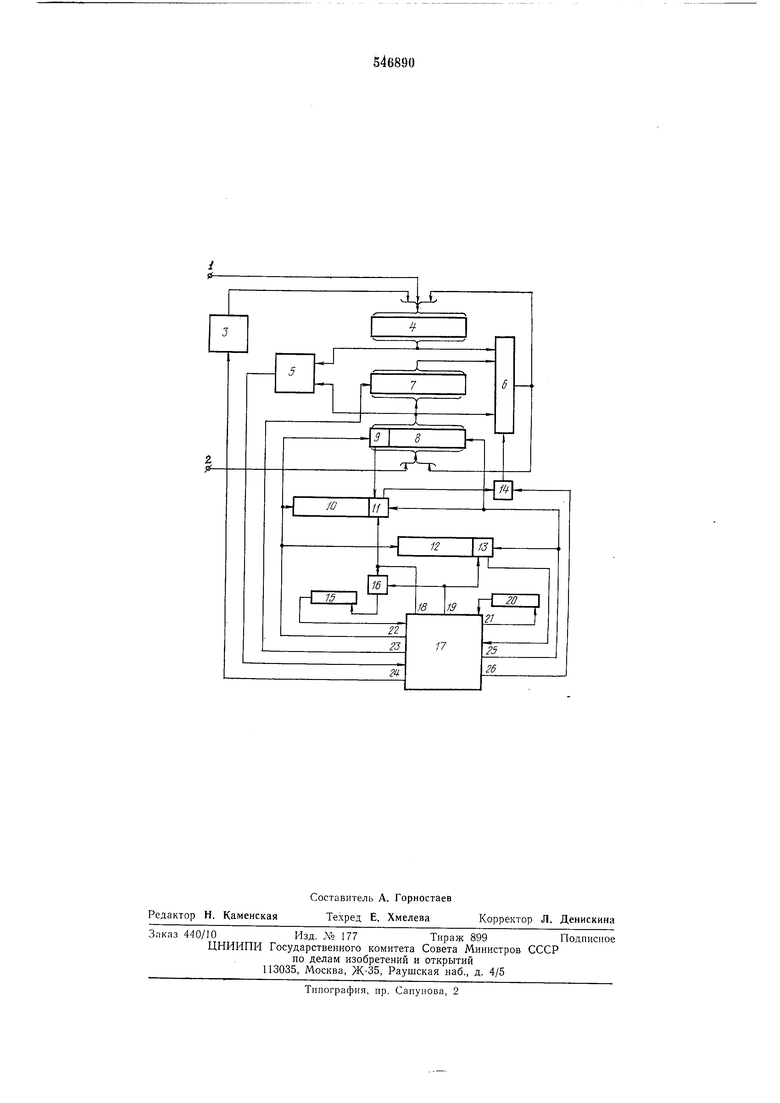

Поставленная цель достигается тем, что в устройство дополнительно введены блок сравнения, счетчик итераций, регистр знаков, сумматор по модулю два и элемент ИЛИ, приче.м первый вход блока односторонней памяти связан с первым выходом блока управления, а выход - с первым информационным входом регистра псевдоделителя, второй вход которого соединен с первой информационной шиной, а третий вход - с выходом сумматора - вычитателя и первым входом регистра делимого, второй вход которого соединен со второй информационной шиной, а выход - с первым входом блока сравнения, с первым входом сумматора- вычитателя и информационным входом регистра модификатора, управляющий вход которого связан со вторым выходом блока управления, а выход - со вторым входом сумматора - вычитателя, третий вход которого соединен с выходом регистра псевдоделителя и вторым входом блока сравнения, выход которого связан с первы.м входом блока управления, третий выход которого соединен с пер3вымп управляющими входами регистра псевдочастного и регистра зиаков и знакового разряда регистра делимого, четвертый выход - с первым входом сумматора по модулю два, пятый выход - с первыми входами5 младших разрядов регистра псевдочастного и регистра знаков и управляющим входом регистра делимого, шестой выход - со входом счетчика шагов, седьмой выход - с первым входом элемента Р1ЛИ и вторым входом млад-10 шего разряда регистра псевдочастного, восьмой выход - со вторым входом элемента ИЛИ и первым установочным входом младшего разряда регистра знаков, второй установочный вход которого соединен с выходом15 знакового разряда регистра делимого, а выход- со вторым входом сумматора по модулю два, выход которого соединен с четвертым входом сумматора - вычитателя, выход младшего разряда регистра псевдочастного20 связан со вторым входом блока управления, третий вход которого соединен с выходом счетчика итераций, вход которого связан с выходом элемента ИЛИ, четвертый вход блока управления соединен с выходом счетчика25 шагов. На чертеже показана блок-схема предлагаемого устройства, где: I-первая информационная шина (для записи информации в ре-30 гистр г евдоделителя /псевдомножимого/, первый вход); 2 - вторая информационная шина (для записи информации в регистр делимого /произведения/, второй вход); 3 - блок односторонней памяти (для хранения35 констант); 4 - регистр псевдоделителя (псевдомножимого); 5 - блок сравнения; 6- сумматор-вычитатель; 7 - регистр модификатора; 8 - регистр делимого (произведения); 9 - знаковый разряд регистра делимого40 (произведения); 10 - регистр знаков (цифр цсевдочастного /псевдомножителя/); 11- младший разряд регистра знаков; 12 - регистр псевдочастного (псевдомножителя); 13 - младший разряд регистра псевдочастно-45 го (псевдомножителя); 14 - сумматор по модулю два; 15 - счетчик итераций; 16 - элемент ИЛИ; 17 - блок управления; 18 - выход устройства управления для передачи сигнала изменения знака преобразования; 19-50 выход устройства управления для передачи сигнала прибавления (вычитания) «1 к (из) младшему разряду регистра псевдочастного (псевдомножителя); 20 - счетчик шагов; 21-выход устройства управления для пере-55 дачи сигнала прибавления (вычитания) «1 к (из) содержимому счетчика шагов; 22 - выход устройства управления для передачи сигнала сдвига вправо регистров 8, 10 и 12; 23- выход устройства управления для передачи60 сигнала сдвига вправо регистра модификатора 7; 24 - выход устройства управления для передачи сигнала выборки очередной константы из постоянного запоминающего устройст.ва; 25 - выход устройства управления для65 . 4 передачи сигнала сдвига влево регистров 8, 10 и 12; 26 - выход устройства управления для передачи сигпала установки знака иреобразования. Ниже приведено описание работы устройства для случая десятичной системы счисле ия, однако, предлагаемое устройство может работать при произвольной значности систе iw счисления. При вычислении функции предлагаемое устройство работает следующим образом. Величины х и у, поступающие на входы 1 и 2, записываются со своими знаками в регистры 4 и 8. Перед началом процесса псевдоделения содержимое счетчика итераций 15 и счетчика шагов 20 обнуляется, а на выходе 26 блока управления 17 появляется сигнал «ЛОГ 1, обеспечивающий режим псевдоделения. В начале каждого шага, на котором вычисляется очередная цифра псевдочастного, производится пересылка содержимого знакового разряда 9 регистра делимого 8 в младший разряд 11 регистра знаков 10. Для осуществления .модификации выход регистра делимого 8 соединен со входом регистра модификатора 7, на сдвиговый выход которого поступает сигнал с выхода 23 блока управления 17. Величина сдвига регистра 7 определяется содержимым счетчика шагов 20. Выходы регистров 8 и 7 соединены со входами сумматора-вычитателя 6, выход которого подключен ко входу регистра 8, для заииси в него нового значения делимою со своим знаком. Выходы регистров 7 и 4 соединены со входами сумматора--вычитателя 6, выход которого подключен ко входу регистра 4, для записи в него нового значения псевдоделителя со своим знаком. Выход младшего разряда 11 регистра 10 соединен ее входом сумматора 14 для задания режима слол ения или вычитания в сумматоре - вычитателе 6. После вычисления новых значений псевдоделителя и делимого на выходе 19 блока управления 17 появляется сигнал, осуществляющий прибавление «1 к младшему разряду 13 регистра 12. Процесс продолжается до тех пор, пока на выходе блока сравнения 5 не появится сигнал о том, что содержимое регистра 8 меньше или равно по абсолютной неличине содержимому регистра 4, после чего происходит анализ содержимого младшего разряда 13 регистра 12 блоком управления 17 на четность; при нечетном значении содержимого разряда 13 цифра псевдочастного считается вычисленной, при четном значении содержимого разряда 13 производится еще одна итерация. После вычисления очередной цифры псевдочастного (каждая цифра меньше или равна 9) осуществляется проверка содержимого счетчика итераций 15; если содержимое счетчика итераций 15 меньше «9, то на выходе 18 блока управления 17 появляется сигнал, осуществляЕощий изменение знака преобразования. Далее итерации продолжаются с той разницей, что на выходе 19 блока

управления 17 не вырабатывается сигнал прибавления «1 к младшему разряду 13 регистра 12. Процесс продолжается до тех пор, пока содержимое счетчика не станет равным «9. Перед началом вычисления следующей цифры псевдочастного на выходе 25 блока управления 17 появляется сигнал, осуществляющий сдвиг влево регистров 8, 10, 12, а на выходе 21 ,блока управления 17 появляется сигнал прибавления «1 к содержимому счетчика щагов 20, выход которого подключен ко входу блока управления 17; содержимое счетчика итераций 15 обнуляется. Описанный процесс псевдоделения продолжается до тех пор, пока не будут вычислены все цифры псевдочастного. По окончании псевдоделения в регистре 4 содержится величина , где К - заранее вычисленная константа.

При вычислении функций Sina и Cosa устройство работает следующим образом. Величина X, поступающая на вход 2, записывается в регистр 8 со своим знаком. Далее следует процесс псевдоделения на константы вида lO-arctg 10, который отличается от обычного деления тем, что перед вычислением каждой цифры псевдочастного в регистр 4 записывается новая константа из блока односторонней памяти 3 с помощью сигнала на выходе 24 блока управления 17. Знакопеременное псевдочастное, представляемое только нечетными цифрами, формируется аналогично описанному выше процессу при вычислении функции ./( Отличие заключается в том, что не выполняются дополнительные знакопеременные итерации. По окончании процесса псевдоделения в регистре 12 содержится псевдочастное. Псевдоумножение иа полученное псевдочастное (псевдомножитель) происходит аналогично описанному выше псевдоделению при вычислении функции . Отличие заключаетсяв том,что на выходе 26 блока управления 17 появляется сигнал «ЛОГ О, обеспечивающий режим псевдоумиожения. При умножении на очередную цифру псевдочастного на выходе 19 блока управления 17 появляется сигнал вычитания «1 из младшего разряда 13 регистра 12. Умножение на очередную цифру псевдочастного заканчивается при обнулении разряда 13, после чего производится анализ содержимого счетчика итераций 15. Если оно не равно «9, то выполняются знакопеременные итерации. Для этого на выходе 18 блока управления 17 появляется сигнал изменения знака преобразования. Знакопеременные итерации выполняются до тех пор, пока содержимое счетчика итераций 15 не станет равным «9. Перед началом следующего шага псевдоумножения происходит сдвиг вправо регистров 8, 10 и 12 с помощью сигнала на выходе 22 блока управления 17. По окончании псевдоумножения в регистре 4 содержится величина /С-Cosa, а в регистре 8 -величина К- Sina.

Формула изобретения

Устройство для вычисления элементарных функций, содержащее блок управления, счетчик шагов, регистры, сумматор-вычитатель и блок односторонней памяти, отличающееся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены блок сравнения, счетчик итераций, регистр знаков, сумматор по модулю два и элемент ИЛИ, причем первый вход блока односторонней памяти связан с первым выходом блока управления, а выход-с первым информационным входом регистра псевдоделптеля, второй вход которого соединен с первой информационной шиной, а третий вход - с выходом сумматора-вычитателя и первым

входом регистра делимого, второй вход которого соединен со второй информационной шииой, а выход - с первым входом блока сравнения, с первым входом сумматора-вычитателя и информационным входом регистра модификатора, управляющий вход которого связан со вторым выходом блока управления, а выход - со вторым входом сумматора-вы читателя, третий вход которого соедииен с выходо.м регистра псевдоделителя и вторым

входом блока сравнения, выход которого связан с первым входом блока управления, третий выход которого соединен с первыми управляющими входами регистра псевдочастного и регистра знаков и знакового разряда регистра делимого, четвертый выход - с первым входом сумматора по модулю два, пятый выход - с первыми входами младших разрядов регистра псевдочастного и регистра знаков и управляющим входом регистра делимого, шестой выход - со входом счетчика шагов, седьмой выход - с первым входом элемента ИЛИ и вторым входом младшего разряда регистра псевдочастного, восьмой выход - со вторым входом элемента ИЛИ и

первым установочным входом младшего разряда регистра знаков, второй установочиы: вход которого соединен с выходом знакового разряда регистра делимого, а выход - со вторым входом сумматора по модулю два,

выход которого соединен с четвертым входом сумматора-вычитателя, выход младшего разряда регистра псевдочастного связан со вторым входом блока управления, третий вход которого соединен с выходом счетчика

итераций, вход которого связан с выходом элемента ИЛИ, четвертый вход блока управления соединен с выходом счетчика шагов.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство С ССР Aib 404082, М. Кл.2 G 06F 7/38, опубл. 16.06.72.

2. /ВМ, Jornal of research and development V. 6 № 2, 1962, стр. 210-216.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ПСЕВДОЧАСТНОГО | 1972 |

|

SU330449A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

Авторы

Даты

1977-02-15—Публикация

1973-08-14—Подача