(54) ОПЕРАЦИОННОЕ УСТЮЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для сопряжения абонентов с магистралью | 1986 |

|

SU1361570A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

1

Изобретение относится к области выгшслительной техники, в частности к операщюнньш устройствам, и может быть использовано в процессорах различного назначения.

Известно операционное устройство, содержащее 1шформационные регистры, единтиые входы триггеров каждого разряда которых подключены к выходам элементов И, блок приема информации, блок управления, элементы НЕ, элементы И с открытым коллектором 1

Недостаток устройства состоит в том, что оно имеет ограниченные функаиоиалъные возможности.

Наиболее близким к и-зобретению по технической сущности и достигаемому результату является операционное устройство, срдержашее блок дешифрации команд, мерный выход которого соединен с первым входом блока управления, блок синхронизацяи, выход которого соединен со вторым «ходом блока управления, регистр результата, пыхои которого соединен с первым входом блока буферной памяти, первый коммутатор, первый и второй входы которого coeniinfiiM с выходами регистipoB соответственно первого и второго операндов, сумматор, выход которого соединен с первым входом второго KOMNiyTaTOpa, и датчик параметров сдвига, выход которого соед1шен с управляющим входом регистра результата, причем выход .блока буферной памяти соединен со входом регистра первого операнда и с первым входом регистра второго операнда, второй вход которого является ш формаодонным входом устройства, первый и второй выходы первого коммутатора соединены соответственно с первым и вторым входами сумматора, третий вход которого, вторые входы блока буферной памяти и второго коммутатора, входы первого коммутатора латшка параметров сдвига соединены с первым выходом блока управления, выходы второго коммутатора и второй выход блока депдифрашш команд соединены соответственно с paiiiisiiiiUiiMU входами регистра результата и со пхолом блока синхронизации, а вход блока ле1И11фр.чиии команд является командным входом устройства 2.

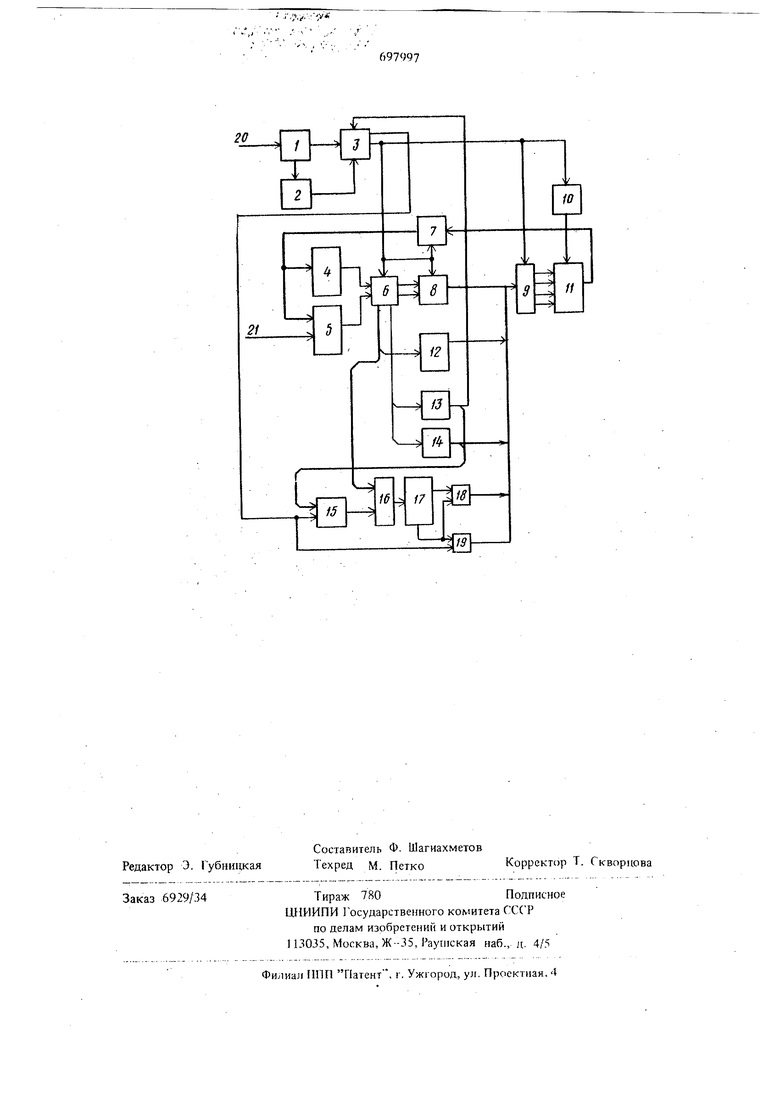

Недостаток устройства-с-чшит в том, что оно имеет незначите1 Ы1(ч nijciinuiciscTBHe. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит первый и второй дешифраторы, преобразователь порядка расположения разрядов, регистр номера приоритетного разряда, формирователь кода границы поиска и три элемента И, причем третий выход первого коммутатора соединен с первым входом перво го элемента И и через преобразователь порядк расположения разрядов - со входом второго коммутатора, четвертый выход первого комму татора соединен со входами первого и второго дешифраторов, выходы которых соединены с первым входом формирователя кода грани(ды поиска, выход которого соединен со вторым входом первого элемента И, вход и первый выход регистра номера приоритетного разряда соединены соответственно с выходом первого элемента И и с первым входом второго элеме та И второй вход которого и первый вход третьего элемента И соединены со вторым выходом регистра номера приоритетного разряда, выход первого дешифратора соедш1ен с третьим входом управления, второй выход которо го соединен со вторыми входами формировател кода границы поиска и третьего :)лемента И, а выходы второго дешифратора, второго и третьего элементов И соединенр) со входом второго кЬммзтатора. Структурная схема устройства представлена на чертеже. Операционное устройство содержит блок 1 дешифратора команд, блок 2 синхронизации, блок 3 управления, регистр 4 первого onepaim регистр 5 второго операнда, первый коммутатор 6, блок 7 буферной памяти, сумматор 8, второй коммутатор 9, датчик 10 параметров сдвига, регистр 11 результата, преобразователь 12порядка расположения разрядов, первьгй 13и второй 14 дешифраторы, формирователь 15 кода границы поиска, первый элемент И 16, регистр 17 номера приоритетного разряда, второй 18 и третий 19 элементы И, командный 20 и информационный 21 входы. Операционное устройство работает следуюшим образом. Операция Шифрация Команда Шифрация в сопровождении сиг.нала Команда готова принимается в блок 1, запускается блок 2 синхронизации, блок 3 управления вырабатывает сигналы обрашения к блоку 7 (два последовательных защюса} и происходит чтение содержимого регистра 4, затем содержимого регистра 5 с гюследуюшей записью в регистр 4 первого операнда и регистр 5 второго операнда. Лалсе производится побайтное выполнение опсрапин. Номер разряда, от которого начинается поиск единицы, задан в разрядах 27-31 регистра 4. Шифруемое число находится в регистре 5. Из регистра 5 побайтно читается шифруемое число. Разряд от которого идет поиск, определяется следующим образом: результат дешифрации старших разрядов параметра {разряды 27, 28) в дешифраторе 13 определяет номер байта, с которого начинается поиск единицы, а на основании дешифрации младших разрядов (разрядов 29, 30, 31) регистра 4 дешифратором 14 для поиска единицы поступают только те разряды байта, которые находятся . по направлению поиска. Результатом работы является двоичный номер первого ненулевого (приоритетного) разряда от границы поиска, если он есть. Обшая совокупность сигналов: номер байта изблока 3 управления и сигналов с дешифраторов 13, -14 организует поиск первой едини1Ц51 в граничном байте. В случае отсутствия первого ненулевого разряда в граничном байте происходит последовательный поиск единицы в последуюших байтах. Эта последовательность сигналов поступает в формирователь 15, который формирует код границы в байте, от которого ведется поиск первого ненулевого разряда. В случае обнаружения единицы на регистре 17 формируется двоичный код первого единичного разряда в байте, в направлении поиска. Два старших разряда, определяюшие номер байта, в котором обнаружена единица, формируются блоком 3 управления. Занесение в регистр 11 сформированного результата шифрации происходит через элементы И 18, 19. В случае отсутствия единицы в части слова от границы поиска, при последовательном переборе всех старших байтов, результат шифра1ши остается нулевым. Далее, результат через коммутатор 9 заносится по байтным информационным стробам записи в регистр 11 результата. Опера1щя Дешифраш{я При вьЕПОлнении команды Дешифрация происходит считывание опера1ща из блока 7 по адресу, содержащемуся в регистре 5, и запись в регистр 5. Через коммутатор 6 пятиразрядный параметр поступает на вход дешифраторов 13, 14. Два старших разряда дешифруются дешифратором 13, выходы которого участвуют в формировапии стробов записи в регистр результата и опреяеляют номер байта, в который необходимо записать результат, дешифрации трех младших разрядов параметра, де1иифрируемых ле111иф11а1Ором 4. Результат деип1фрации записывается в блок 7 ио адресу, содержащемуся я регистре 4. Операция Рефлексия 56 Выполнение операции Рефлексия реализуется преобразователем 12 представляющим собой линейку вентилей, запайка выходов которы проведена зеркально относительно середины байта. Через первый коммутатор 6 рефлектируе мый операнд подается на преобразователь 12, начиная с младшего байта. Занесение результата рефлексии производится в регистр 11 (результата стробированный управляющими сигйалами из блока 3 управления. Изобретение по сравнению с известным устройством имеет более высокое быстродействие. Действительно поиск единичного значения бита от заданного начала отсчета с помощью операций сдвига, перехода условного, перехода по счетчику требует в реднем 3 х 32 2 i 48 операций над 32-х разрядными словами. В изобретении для решения той же задачи требуется всего одна операция. Эта операция в 48 раз увеличивает быстродействие ненулевого бита. При отсутствии операции дешифрация запись числа от О до 31 в таблицу битовых спехщфикаций с помощью операций Вычитание кодов , переход условный , переход по счет чику требует в среднем 3x32:2 48 операш1й над 32-х- разрадными словами. То есть эта операция в 48 раз увеличивает быстродействие записи числа в таблицу битовых спецификаций. Таким образом при нали ии всего 1% от общего числа операций на шифрацию и дешиф рацию тратится 50% эффективного быстродействия при отсутствии этих операций в списке команд. Формула изобретения Операционное устройство, содержащее блок дешифрации команд, первый вьдход которого соединен с первым входом блока управления, блок синхронизации, выход которого соединен со вторым входом блока управления, регистр результата, выход которого соединен с первым входом блока буферной памяти, первый коммутатор, первый и второй входы которого соединены с выходами регистров соответственно первого и второго операндов, сумматор, выход-.. которого соедиг1ен с первым входом второго коммутатора, и датчик параметров сдвига, выход которого соединен с 7 управляющим входом регистра результата, причем выход блока буферной памяти соединен со входом регистра тюрвого опера1ша и с первым входом регистра второго операвда, второй вход которого является Ю1форМацион ым входом устройства, первый и второй выходы первого коммутатора соед1шены соответственно с первым и вторым входами сумматора, третий вход которого, вторые входы блока буферной памяти и второго коммутатора, входы первого коммутатора и датчика параметров сдвига, соединены с первым выходом блока управления, выходы второго коммутатора и второй выход блока дешифрации команд соединены соответственно с разрядными входами регистра результата и со входом блока синхронизации, а вход блока дешифращщ команд является командным входом устройства, о тл и чающееся тем, что, с целью повышения быстродействия, оно содержит первый и второй дешифраторы, 1феобразователь порядка расположения разрядов, регистр номера приоритетного разряда, формирователь кода границы поиска и три элемента И, гфичем третий первого коммутатора соеД1шен с первым входом первого элемента И и через преобразователь порядка расположения разрядов - со входом второго коммутатора, четвертый выход первого коммутатора соединен со входами первого и второго дешифраторов, выходь которых сосдгшеиы с первым входом формирователя кода границы поиска, выход которого со вторым входом первого элемента И, вход и первый выход регистра номера прпор тетного разряда соеди екы соответственно с выходом первого элемента И и с первым входом второго элемента И, второй вход которого и первый вход третьего элемента И со вторым выходом регистра номера приоритетного разряда, выход первого де1пифратора с третьим входом блока управления, второй выход которого соедянеп со вторым входами формирователя кода границ1 поиска и третьего элемента И, а выходы второго дешифратора, второго и третьего элементов И соешшены со входом второго коммутатора. Истощ1икн информации, принять е во внимание при экспертизе 1.Авторское свидетельство СССР № 481899, кл. G 06 F 15/00, 1975. 2.Абонентский пункт АП- 4, КС-8504, ПТ1 320.114. ТО с. 46, рис. 5 (прототип).

Авторы

Даты

1979-11-15—Публикация

1976-12-03—Подача