(54) ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1979 |

|

SU960830A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Операционное устройство процессора | 1979 |

|

SU809189A1 |

| Асинхронное устройство управления | 1979 |

|

SU826351A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для сопряжения группы операционных блоков с общей памятью | 1987 |

|

SU1444790A1 |

Изобретение относится к вычислительной технике, в частности к процессорам цифровых вычислительных машин, оборудование которых используется при работе с большими массивами данных, представленных в табличном виде.

Известен процессор, содержащий блок местной памяти, информационный регистр, сумматор, выходной регистр, узел формирования признаков, первую группу элементов И, регистр признаков, узел управления микропрерываниями, триггер режима, узел микропрограммного управления, содержащий память микрокоманд, регистр адреса, регистр микрокоманды с дешифратором микроопераций,.информационная магистраль каналов, вторая группа злементов И, регистр хранения, третья группа элементов И, второй триггер режима, элементы задержки

Известен также микропрограммный процессор, содержащий блок микро-

программного управления, блок хракв- i ния служебной информации, арифметикологическии блок, блок памяти, блок защиты памяти, блок анализа и подсчета символов данных, блок синхро1щзации, блок управления памятью, блок анализа и подсчета символов, схему сравнения, элемент И, счетчик, узел формирования управляющих сигналов 2,

Однако известные процессоры обладают следукндими недостатками: во-первых, в их структуре отсутствуют элементы, обеспечивающие переадресацию с автоиндексацией, что усложняет программирование и увеличивает время .вычислений; во-вторых, в структурах команд отсутствует формат, который позволяет второй операнд располагать непосредственно-В команде, что снижает эффективное быстродействие процессора.

Наиболее близким к предлагаемому техническому решению является процес38cop Модели 50 системы ВМ-360, содержащий сумматор, основную память, устройство управления, коммутаторы операндов, блок регистров общего назначения, операционный блок и другие специальные регистры. Указанная модель процессора может реализовьюать двухадресную команду и имеет универсальный набор форматов команд (RR, RX, RS, SI, SS). Недостатками процессора являются во-первых, невозможность магазинной обработки операндов без организации данного режима с помощью подпрограммы, что снижает эффективное быстродействие процессора в целом, во-вторых, в формате SI величина операнда, заданного непосредственно в команде, не может превьваать одного байта. И, как следствие указанного недостат ка, - использование формата может осуществляться только для ограниченного количества команд. Цель изобретения - расширение фун циональнь:1х возможностей процессора путем устранения указанных недостатков. Поставленная цель достигается тем что в центральный процессор, содержа щий операционный блок, блок памяти, блок регистров, блок подключения регистров операндов, блок формирования стробов, блок управления, генератор синхросигналов, коммутатор первого операнда, коммутатор второго операнд и коммутатор результата, причем вько коммутатора результатов соединен со входом результата блока регистров, первая и вторая группы выходов которого соединены соответственно с инфо мационными входами коммутатора перво го рперанда и с информационными вход ми коммутатора первого операнда и с информационныкет входами коммутатора второго операнда, выход коммутатора пе вого операнда соединен с первым информ ционным входом операционного блока, вы ход коммутатора второго операнда соеди нен со вторым информационным входом оп I рационного блока, выходы результатов к торого соединены с информационными вхо дами коммутатора результата,тактовы выход генератора синхросигналов соед нен с тактовыми входами блока формирования стробов, блока подключения регистров операндов и блока управления, первый, второй и третий выходы которого соединены соответственно с управляющими входами блока памяти операционного блока и коммутатора результата, адресный вход блока памяти соединен с адресным выходом блока регистров, вход стробов которого соединен с выходом стробов блока формирования стробов, первый кодовый вход которого соединен с управляющим входом коммутатора первого операнда и с первым выходом блока подключения регистров операндов, второй выход которого соединен с управляющим входом коммутатора второго операнда и вторым кодовым входом блока формирования регистров, выход блока памяти соединен с информационным входом блока регистров и с кодовым входом блока подключения регистров операндов, информационный вход блока памяти соединен с информационным выходом коммутатора первого операнда, четвертый выход блока управления, соединен с первым управляющим входом блока формирования стробов, выход окончания команды блока управления соединен со входами окончания команды блока подключения регистров операндов и блока формирования стробов, введены блок режимов и блок дешифрации кодов операций, причем первый и второй выходы блока режимов соединены соответственно с Первым и вторым управляювсими входами блока регистров, третий управляющий вход которого соединен со вторым управляющим входом блока формирования стробов, выходом блока режимов и с первым управляняцим входом блока управления, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходом блока режимов, шестой выход которого соединен с третьим управляющим входом блока формирования стробов, управляющий вход блока подключения регистров операндов., соединен с четвертым управляющим входом блока управления и с седьмым выходом блока режимов, вход признака которого соединен с выходом признака блока подключения регистров операндов, тактовый вход которого соединен с тактовым ;входом блока режимов, вход конца команды которого соединен с выходом конца команды блока управления, кодовый вход которого соединен с выходом блока формирования кодов операций, кодовый вход которого соединен с кодовым входом блока режимов, и выходом блока памяти, синхронизирующий вход блока дешифрации кодов операций соединен с синхронизирующим выходом блока подключения регистров операндов, при этом блок режимов содержит первьЙ, второй и третий сдвиговые регистры,триггер, дешифратор признака адресации, первый, второй, третий, четвертый, пятый шестой и седьмой, элементы И, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, первый, второй и третий инверторы, причем первый и второй входы дешифратора являются кодовым входом блока, первый выход дешифратора соединен с первым входом первого элемента И, второй вход которого является входом окончания команды блока, второй выход дешифратора со единен с первыми входами второго и третьего элементов И, вторые входы которого соединены со вторым входом перового элемента И, третий вход второго элемента И соединен с выходом первого тшвертора, вход которого соединен с третьим входом третьего элемента И и выходом четвертого элемента И, входы которого соединены с входами первого элемента ИЛИ, входы которого являются кодовью4 входом блока, третий выход дешифратора соединен с перв1лш входами пятого и шестого элементов И вторые входы которых соединены со вторьм входом второго элемента И, третий вход пятого элемента соединен с выходом второго инвертора вход которого соединен с третьим входом вюстого элемента И и выходом пер. вого элемента ШШ, выход пятого элемента И соединен с последовательньж - входом первого сдвигового регистра, синхрониэирукщий вход которого соединен с синхронизирующими входами второ го и третьего сдвиговых регистров и триггера, синхронизирующий вход которого является тактовым входом блока, выходы шестого, второго и третьего элементов И соединены соответственно с последовательными входами второго и третьего сдвиговых регистров и триг гера, выходы второго, третьего, четвертого и пятого элементов ИЛИ являются соответственно первым, вторым, третьим н четвертым выходами блока, выход первого элемента И является пя. тым выходом блока, первый выход первого сдвигового регистра является шестым выходом блока, выход шестого элемента ИЛИ является седьмым выходом блока, второй выход первого сдвигового регистра соединен с первыми выходами второго и шестого элементов ИЛИ, 0i первый выход второго сдвигового регистра соединен с первьм выходом первого сдвигового регистра, второй выход второго сдвигового регистра со- единен с первым выходом третьего сдвигового регистра, третий выход второго сдвигового регистра соединен со вторыми входами второго и шестого элементов ИЛИ, первый выход третьего сдвигового регистра соединен с первым выходом первого сдвигового регистра и выходом пятого элемента ИЛИ, второй выход третьего сдвигового регистра соединен с третьими входами второго и шестого элементов ИЛИ и первым вхо-; дом пятого элемента ЮШ, выход триг- гера соединен с первым входом пятого элемента ИЛИ, четвертым входом шестого элемента ИЛИ и первым входом седьмого элемента И, второй вход которого соединен с выходом третьего инвертора, вход которого является входом признака блока, выход седьмого элемента И соединен с выходом второго элемента ИЛИ, первый, второй и третий входы третьего элемента ИЛИ соединены соответственно с первьии входами первого и второго сдвиговых регистров и со вторм входом третьего элемента И, первый, второй, третий, четвертый, пятый и шестой входы четвертого элемента ИЛИ соединены соответственно с первьм и вторым входами п ервого сдвигового регистра, вторым, первым и третьим выходом второго сдвигового регистра, вторым выходом третьего сдвигового регистра и выходом триггера, второй вход пятого элемента ИЛИ соединен с выходом триггера, а выход - с первым выходом третьего сдвигового регистра и вторым входом второго сдвигового регистра, выход шестого элемента ИЛИ соединен с выходом первого элемента И, а блок дешифрации кодов операций содержит деши4фатор кодов операций и m триггеров кодов операций, причем входы дешифратора кодов опершхий являются кодовым входом блока, m выходов дешифратора кодов операторов соединены с входами m триггеров кодов операций, синхронизирующие входы которых являются синхронизирующим входом блока, выходы m триггеров кодов операций являются выходом блока. Введение дополнительных блоков и новых связей позволило организовать магазинную обработку массивов за счет введения формата команды RX+1 и аппаратного продвижения адреса второго операнда при каждом обращении к массиву данных; использовать формат команды RI (в системе 1ВМ-360 этот формат аналогичен RS) не для ограниченного числа команд, а для всех арифметических и логических команд, причем длина второго операнда не ограничена одним байтом, а равна длине машинного слова.

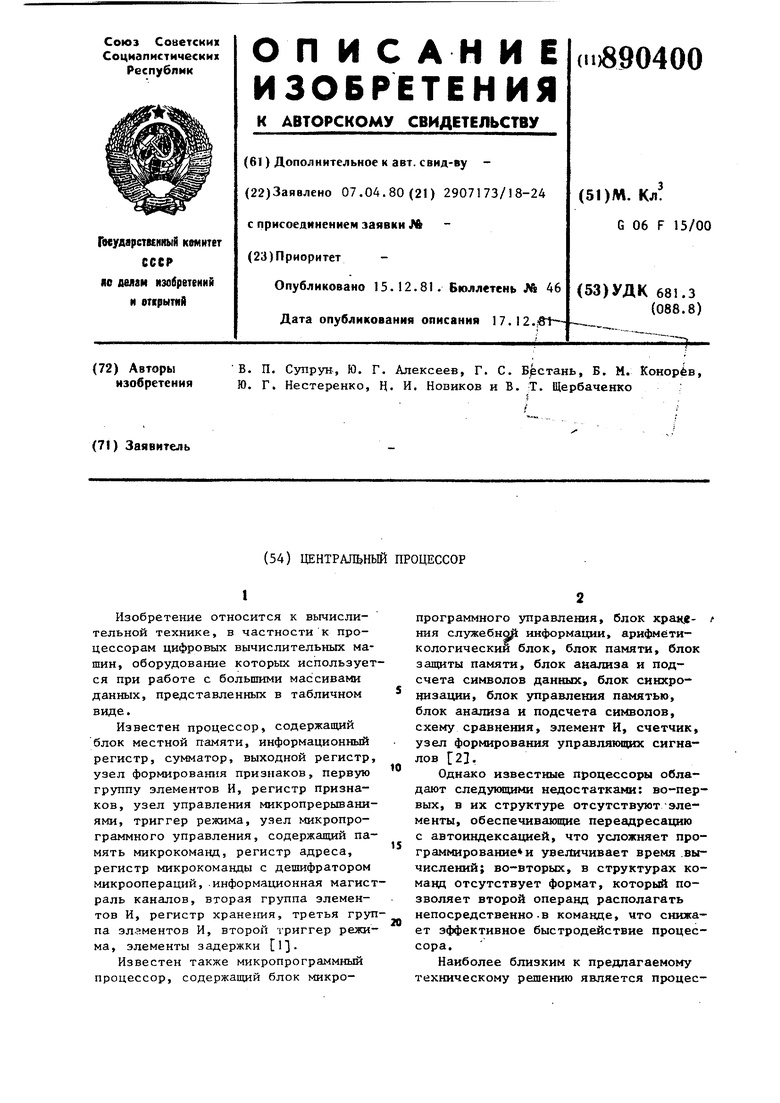

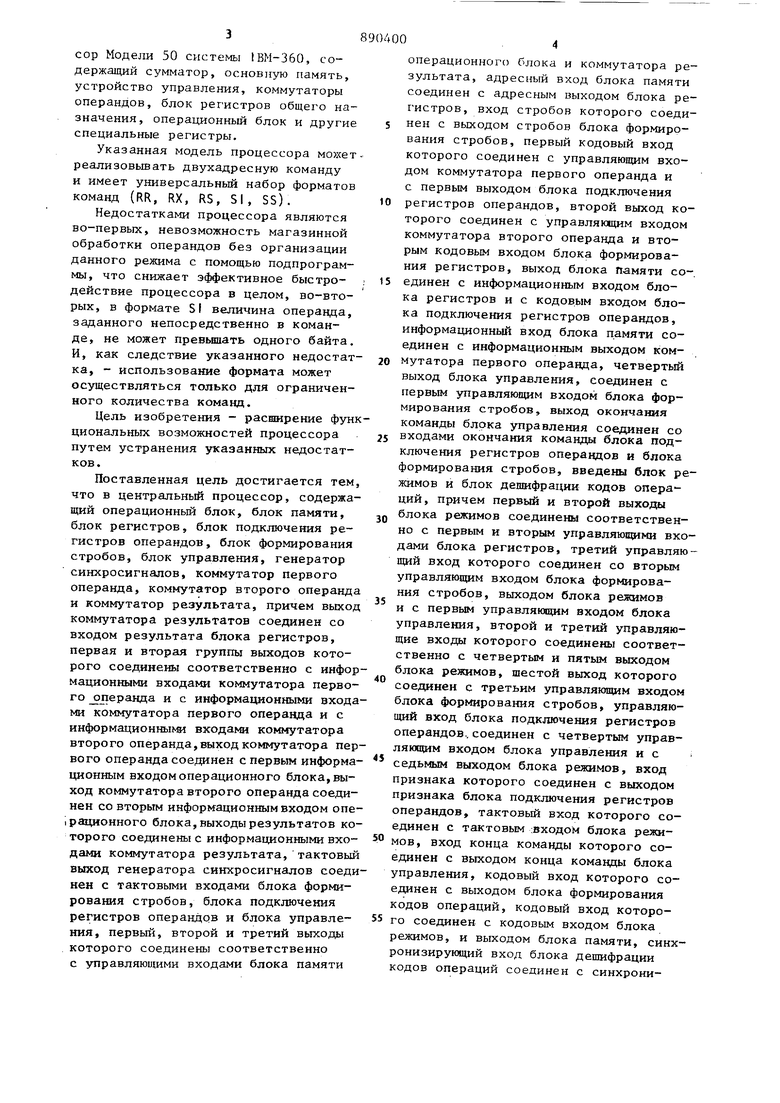

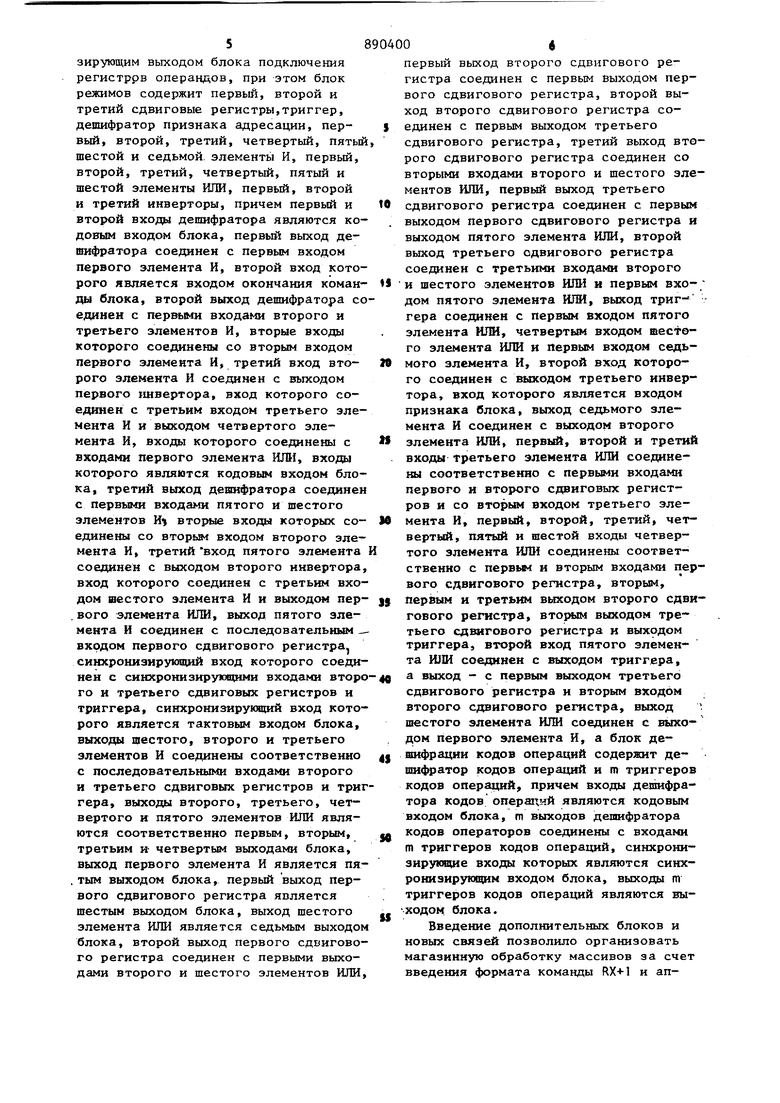

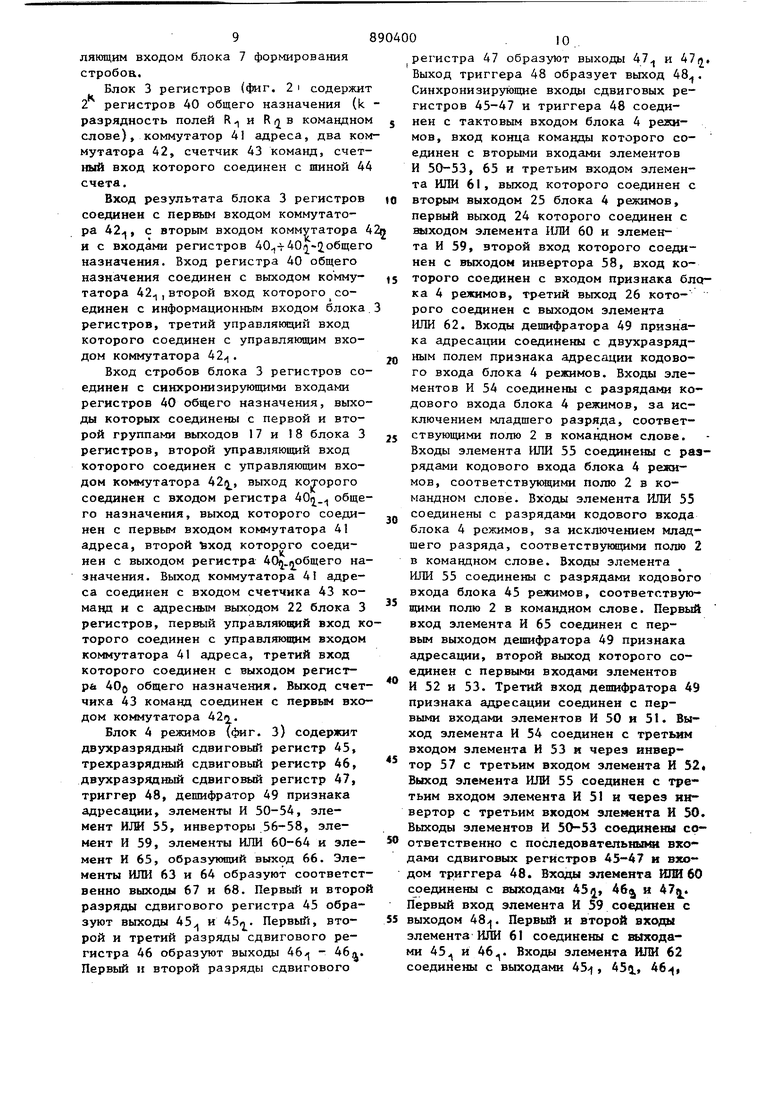

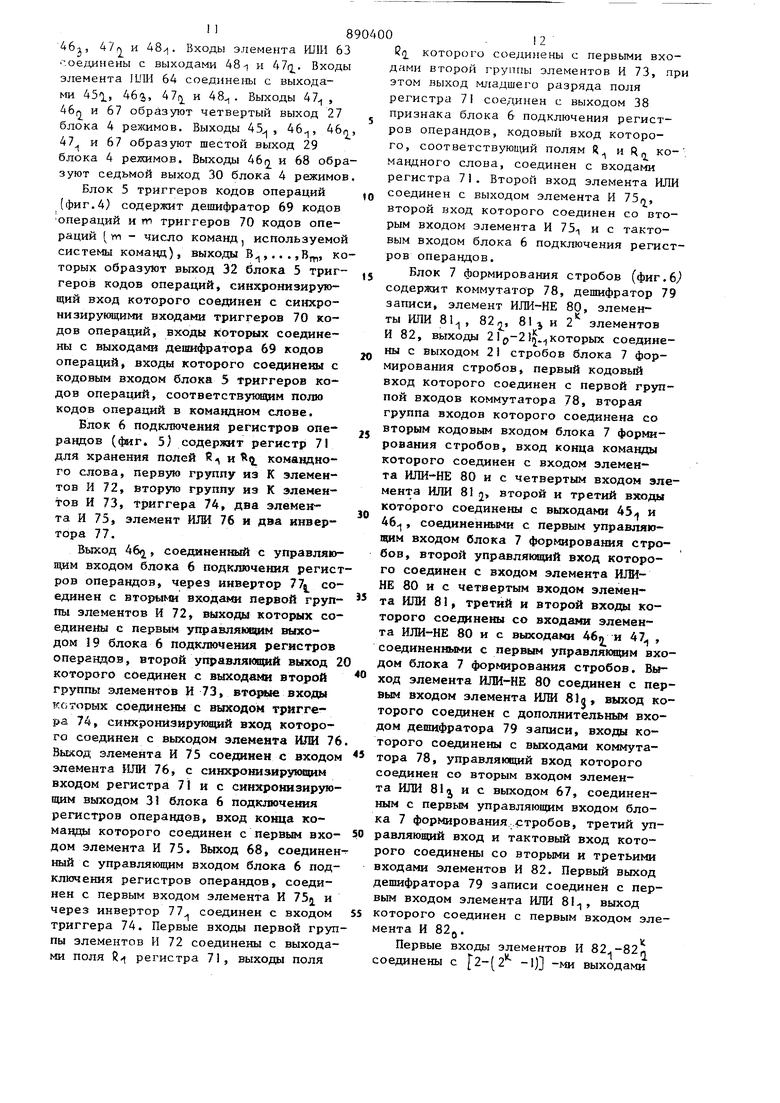

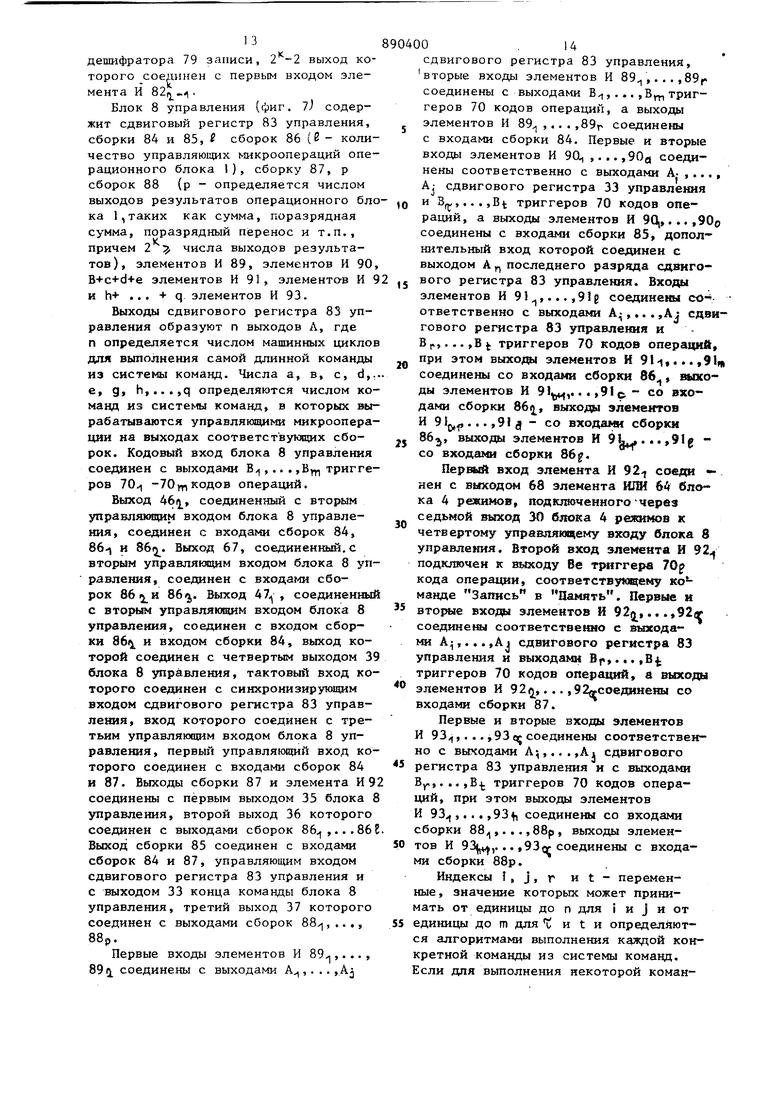

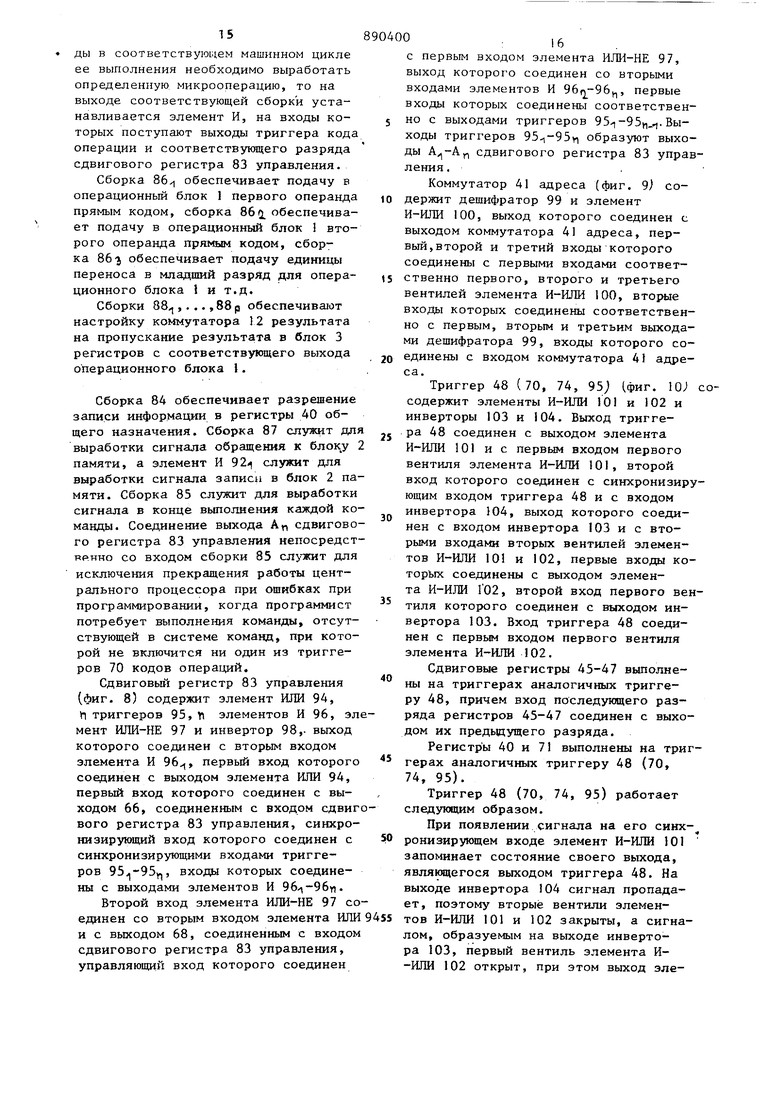

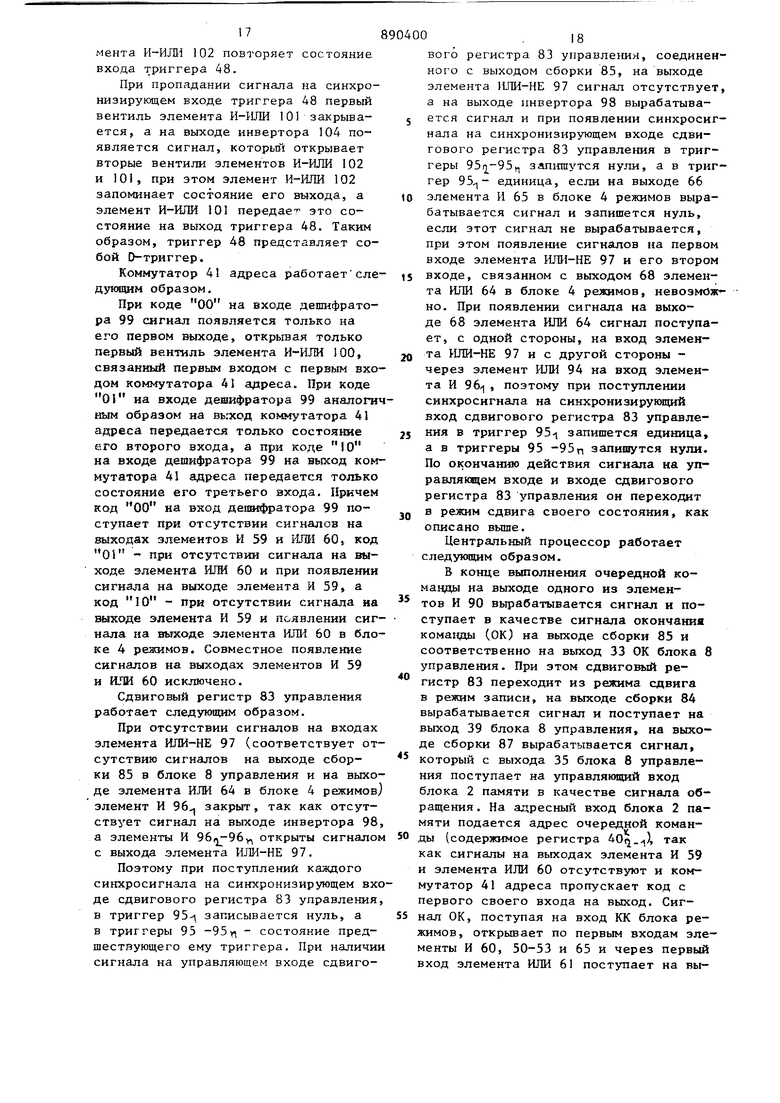

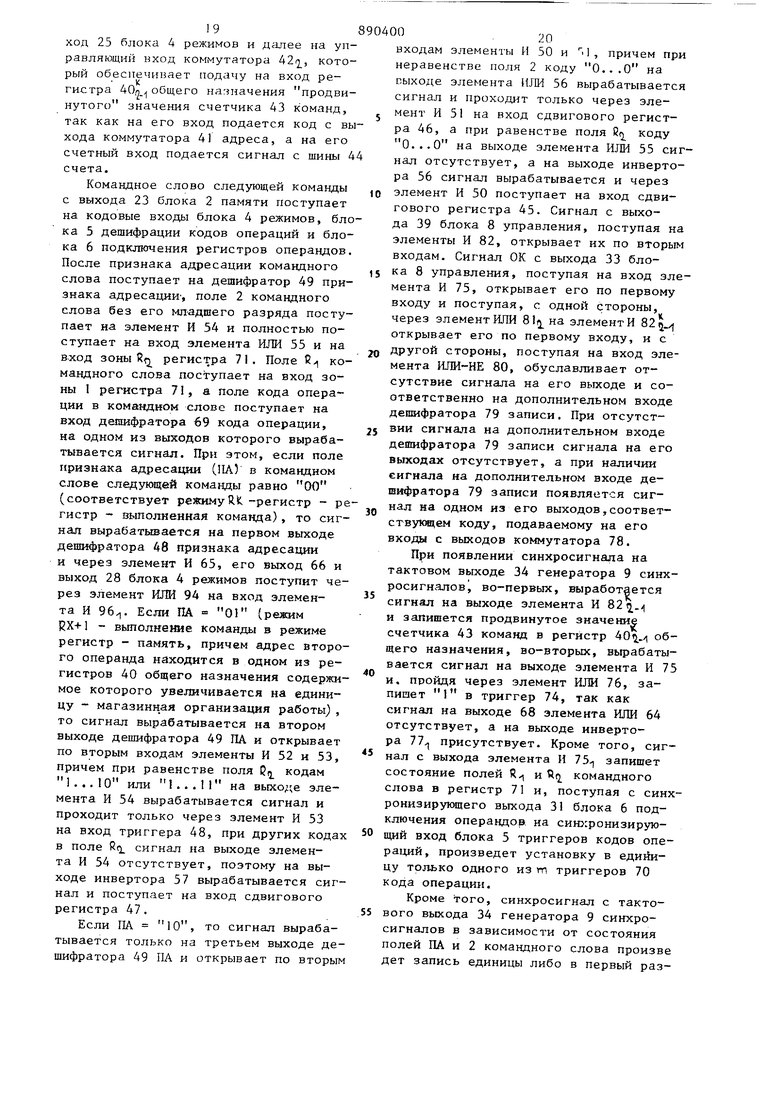

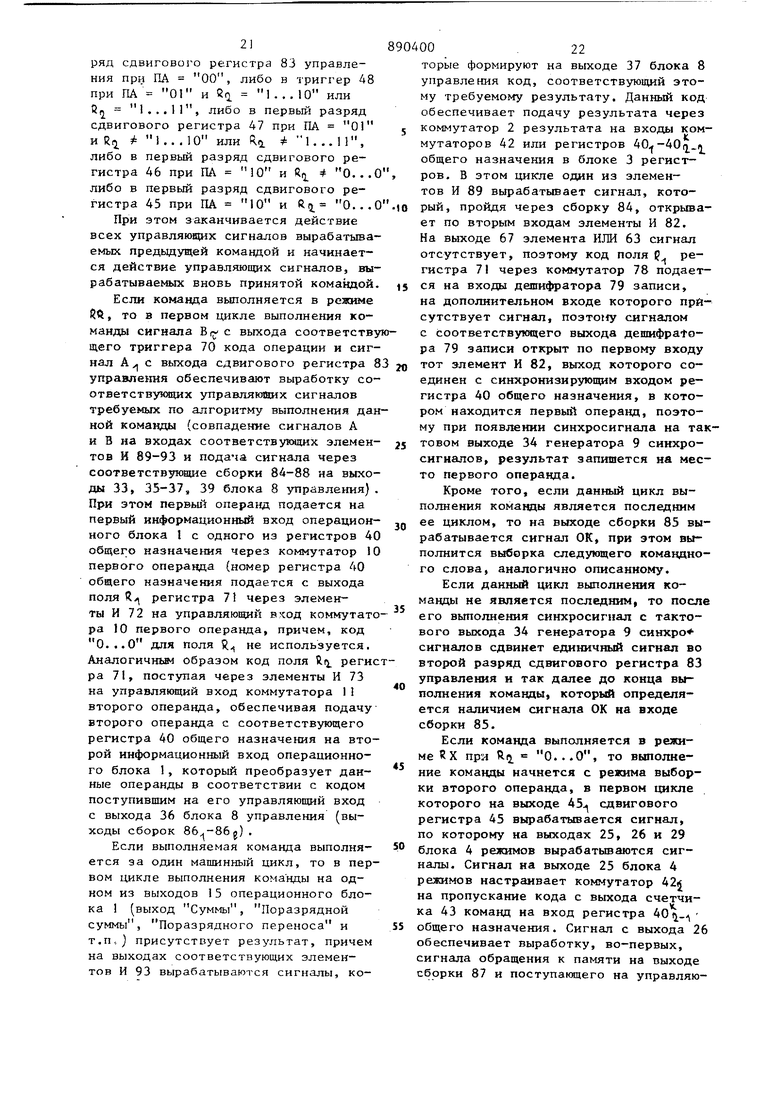

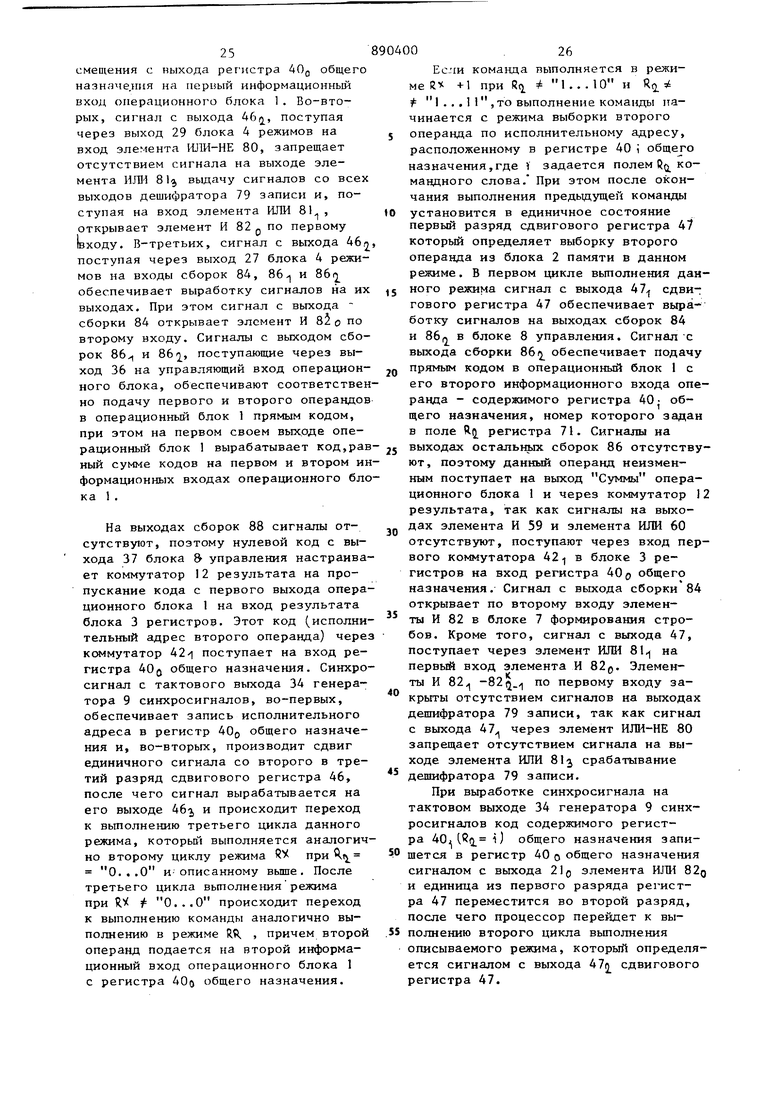

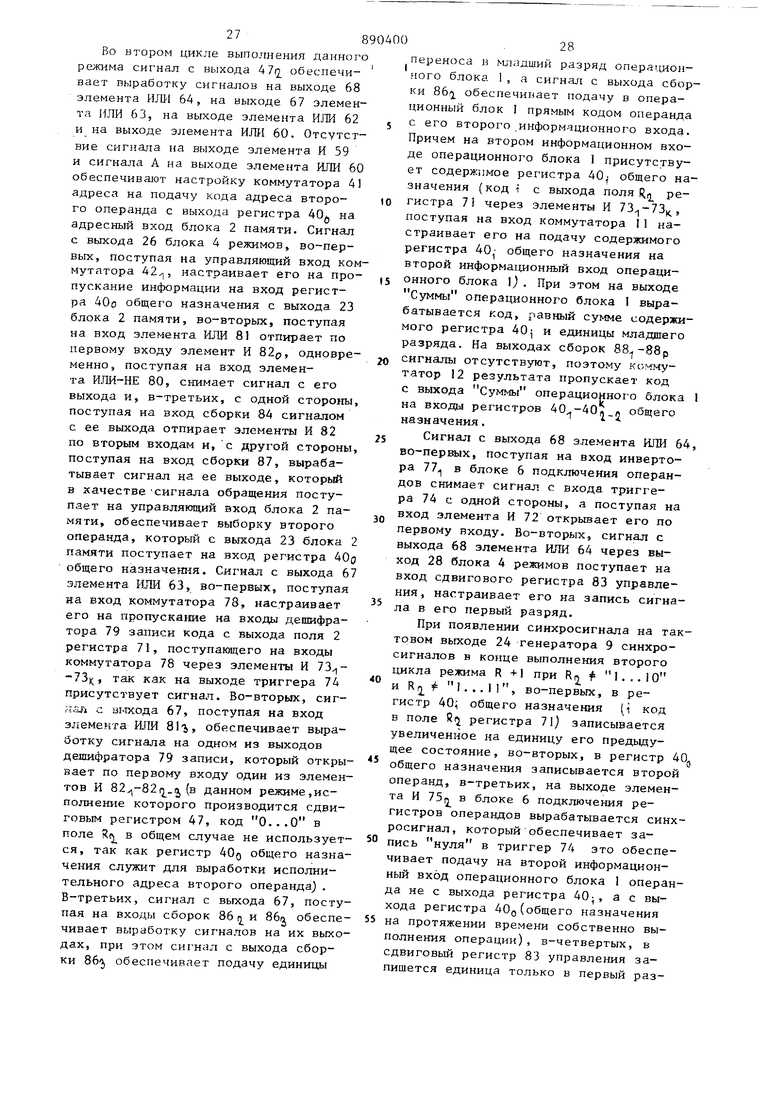

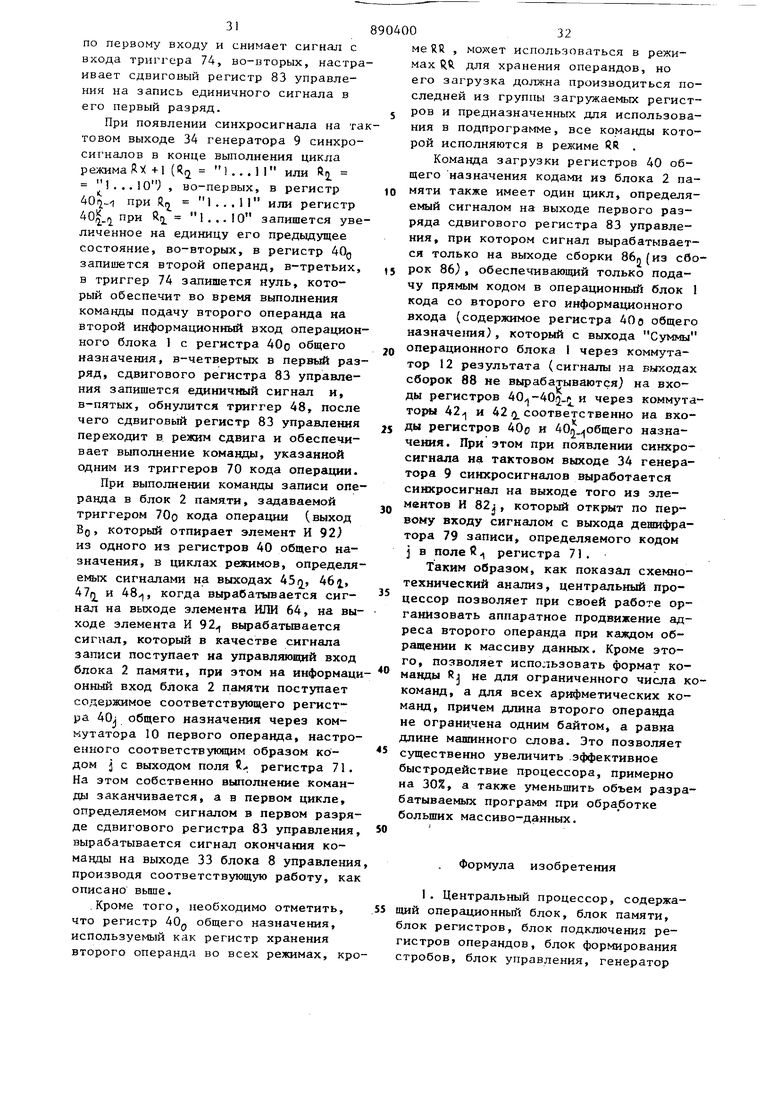

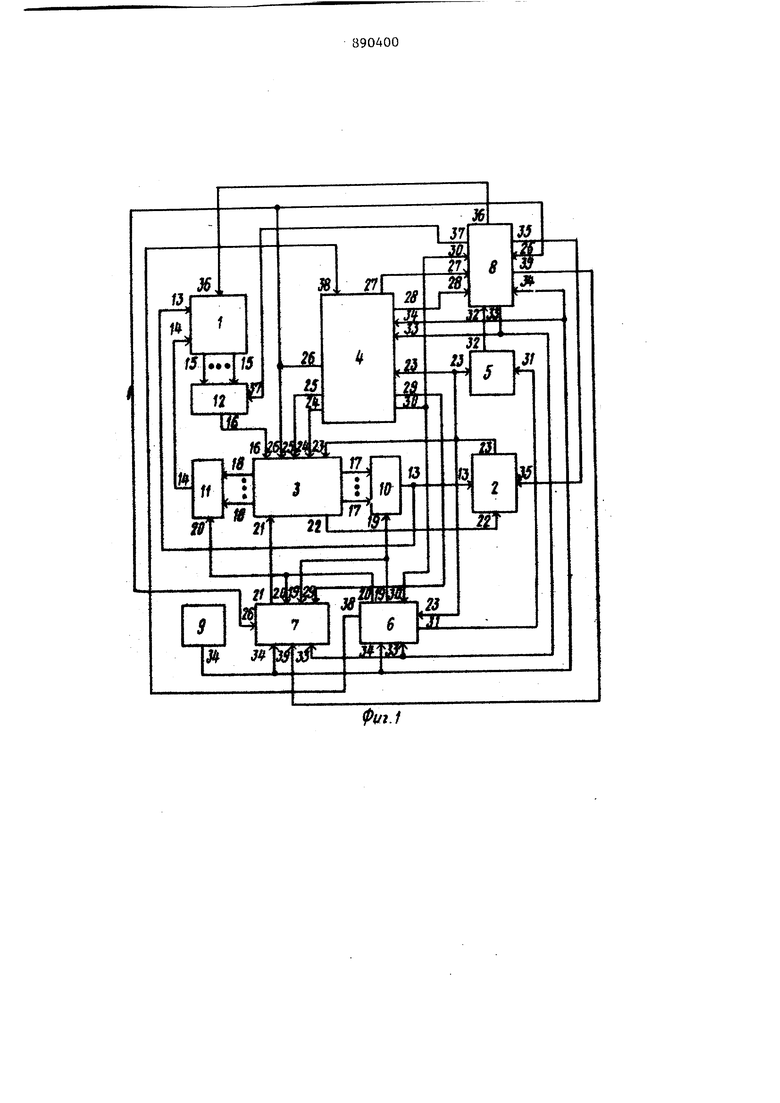

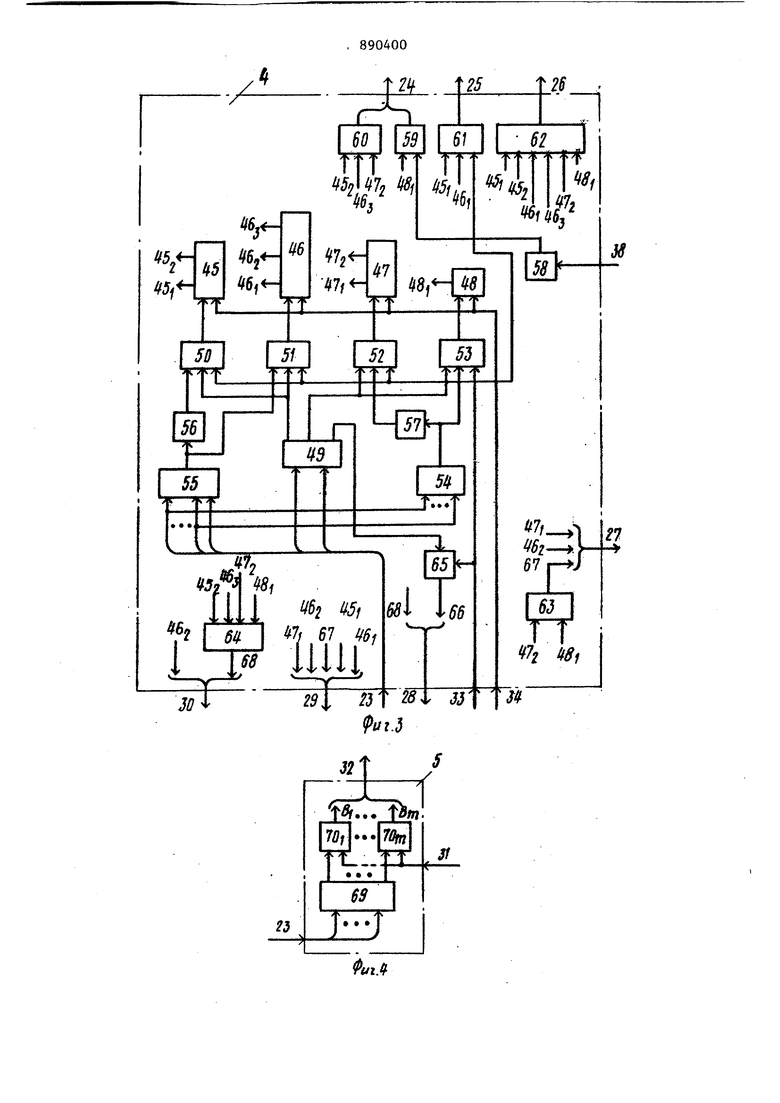

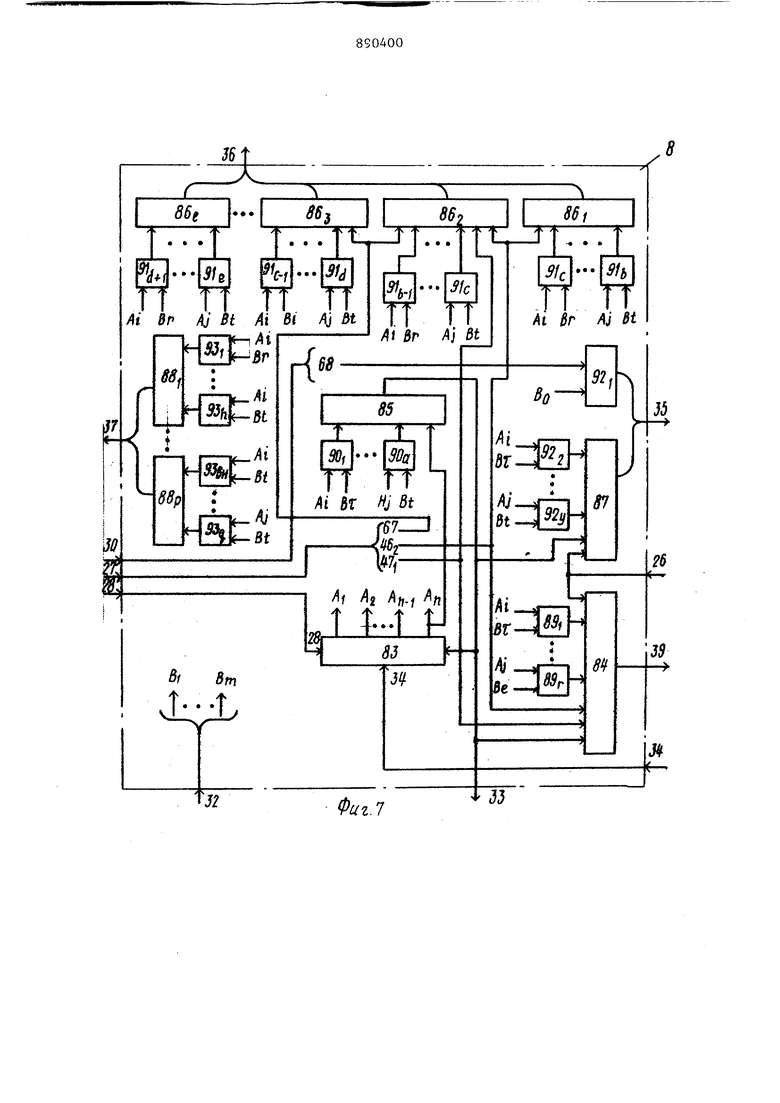

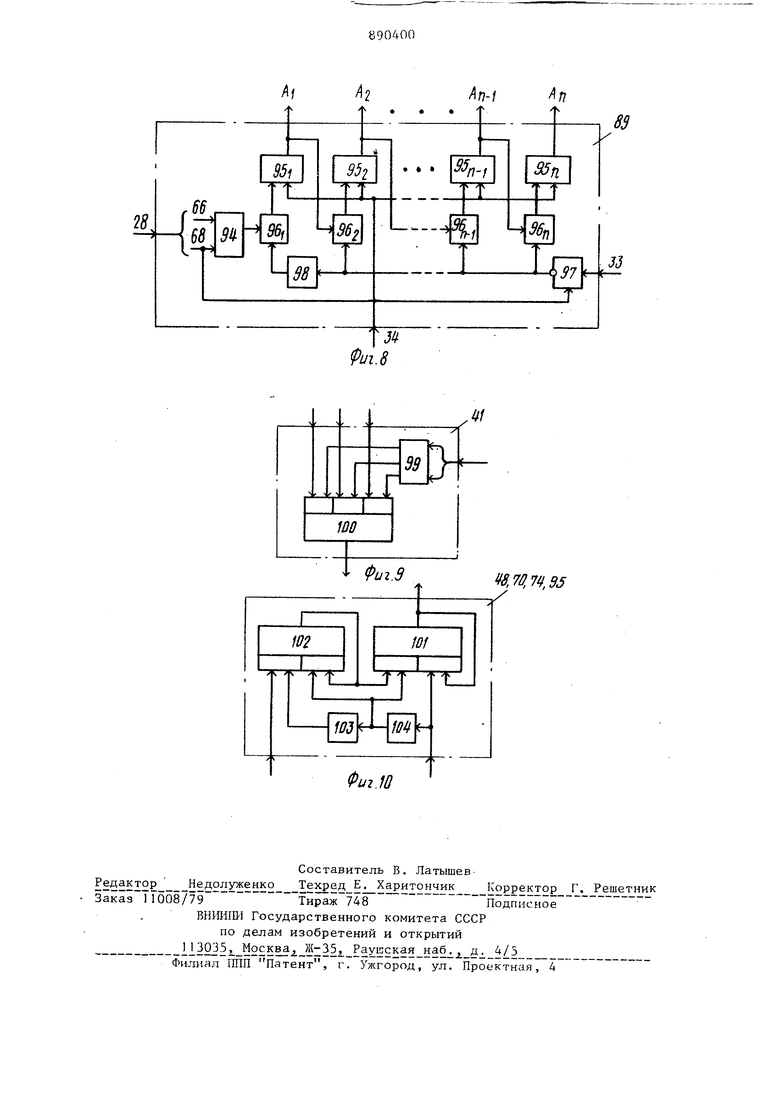

На фиг. 1 представлена блок-схема центрального процессора; на фиг. 2 структурная схема блока регистров; на фиг. 3 - структурная схема блока резкимов; на фиг, 4 - структурная схема блока дешифратора кодов операций; на фиг. 5 - структурная схема блока подключения регистров оЪерандов; на фиг. 6 - структурная схема блока формирования стробов; на фиг. 7 - структурная схема блока управления; на (. 8 - структурная схема сдвигового регистра управления; на фиг. 9 структурная схема коммутатора адреса; на фиг. 10 - структурная схема блока триггеров.

Центральньй процессор (фиг. ) содержит операционный блок 1, блок 2 памяти, блок 3 регистров, блок 4 режимов, блок 5 дешифрации кодов операций блок 6 подключения регистров операндов, блок 7 формирования стробов, блок 8 управления, генератор 9 синхросигналов, коммутатор 10 первого операнда, коммутатор 11 второго операнда и коммутатор 12 результата. Выход 13 коммутатора 10 первого операнда соедииен с информационным входом блока 2 памяти и с первым информационным входом операционного блока 1, второй информационный вход которого соединен с выходом 14 коммутатора 1I второго операнда. Выходы 15 результатов операционного блока 1 соединены с информaщIoнны ш входами коммутатора I2 результата, выход 16 которого соединен со входом результата блока 3 регистров, первая группа выходов 17 которого соединена с информационными входами, а вторая группа выходов 18 с входами коммутатора 11 второго операнда коммутатора 10 первого операнда, первы11 выход 19 блока 6 подключения операндов соединен с управляющим входом коммутатора 10 первого операнда и с первым кодовым входом блока 7 формирования стробов, второй кодовый вход которого соединен с управляющим входом коммутатора 1 1 второго операнда и с выходом 20 блока 6 подключения регистров операндов. Выход 21 стробов блока 7 формирования стробов соединен с входом стробов блока 3 регистров, адресный выход 22 которого соединен с адресным входом блока 2 памяти, выход 23 которого соединен с информационным входом блока 3 регистров и с кодовыми входами блока 4 режимов, блока 5 дешифрации кодов операций и блока 6 подключения регистров операндов. Первый выход 24 блока 4 режимов соединен с первым входом блока 3 регистров, второй вход которого

соединен с вторым выходом 25 блока 4 режимов, третий выход 26 которого соединен с третьим управляющим пходом блока 3 регистров, с вторым управляющим входом блока 7 формирования стробов и с первым управляющим входом блока 8 управления, второй управляющий вход которого соединен с четвертым выходом 27 блока 4 режимов, пятый выход 28 которого соединен с третьим

управляющим входом блока В управления.

Первый управляющий вход блока 7 формирования стробов соединен с шестым выходом 29 блока 4 режимов, седьмой выход 30 которого соединен с четвертым управляющим входом блока 8 управления и с управляющим входом блока 6 подключения операндов, синхронизирующий выход 31 которого соединен с синхронизирукнцим входом блока 5 дешифрации кодов операций, выход 32 которого соединен с кодовым входом блока 8 управления, выход 33 окончания команды которого соединен с входами окончания команды блока 4 режимов,

блока 6 подключения регистров операндов и блока 7 формирования стробов.

Тактовый выход 34 генератора 9 синхросигналов соединен с тактовыми

входами блока 4 режимов, блока 6 подключения регистров операндов, блока 7 стробов и блока 8 управления, первый выход 35 которого соединен с управляющим входом блока 2 памяти. Управляющий вход операционного блока 1 соединен с вторым выходом 36 блока 8 управления, третий выход 37 которого соединен с управляющим входом коммутатора 12 результатов. Выход 38 признака

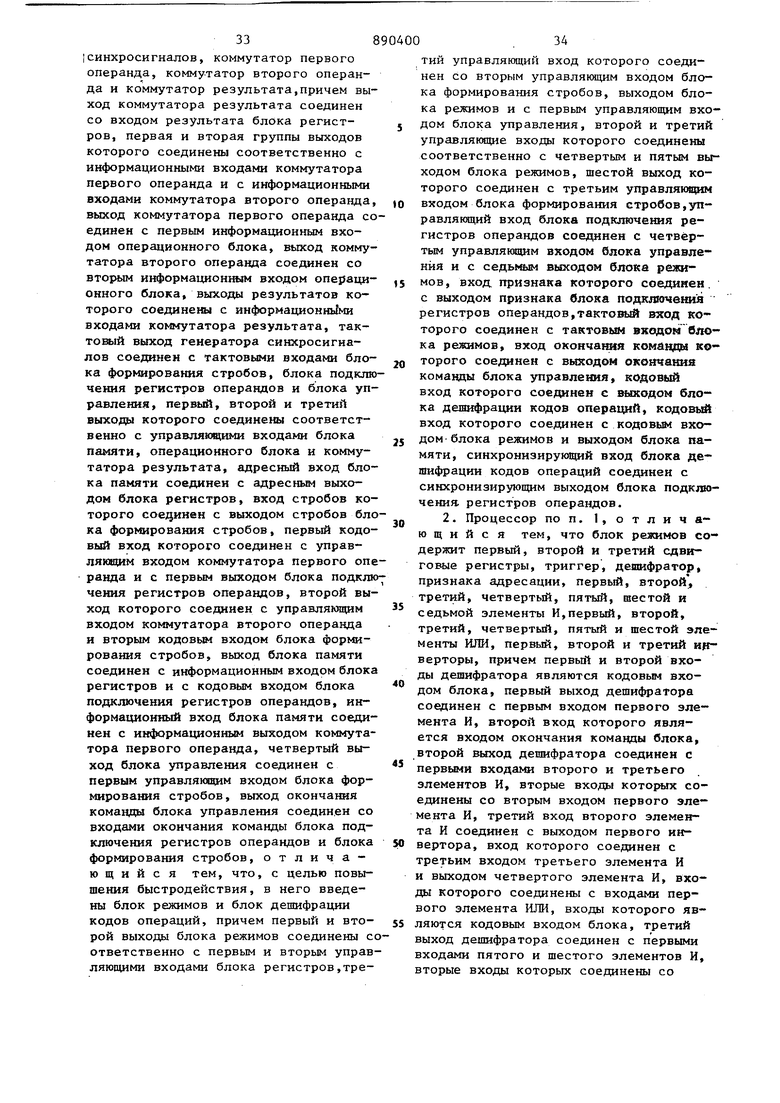

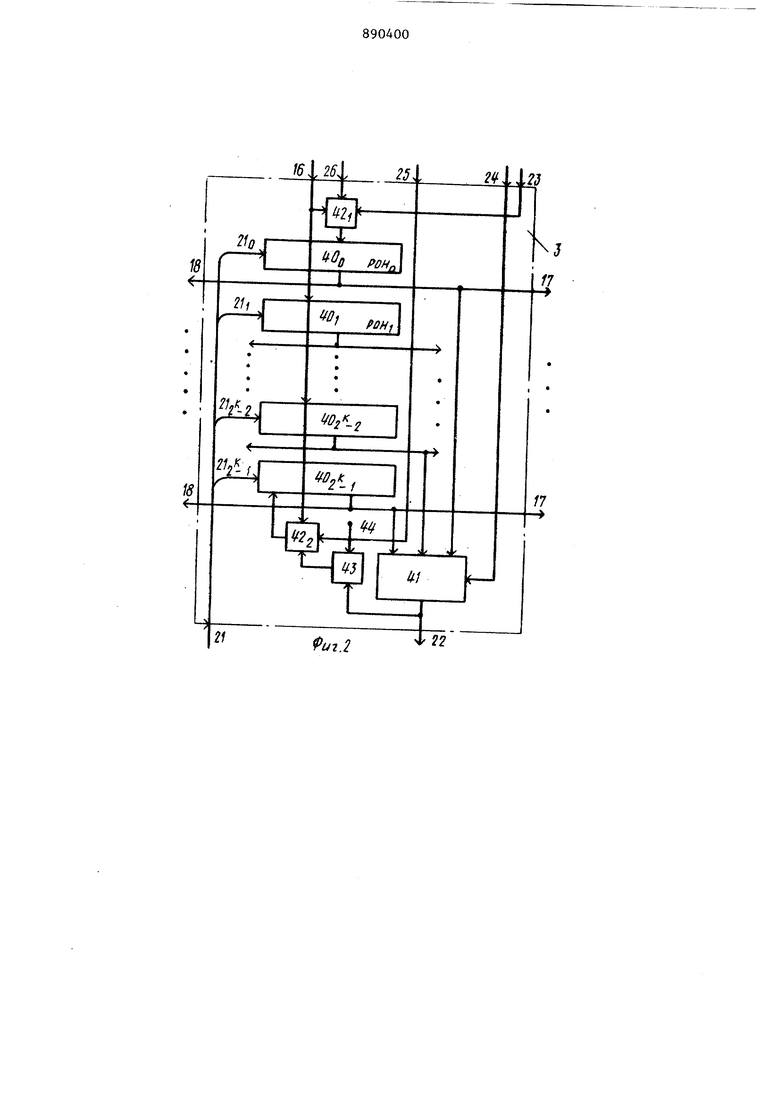

блока 6 подключения регистров операндов соединен с входом признака блока 4 режимов. Четвертьй выход 39 блока 8 управления соединен с третьим управляклцим входом блока 7 формирования стробоа. Блок 3 регистров (фиг. 2 i содержит 2 регистров 40 общего назначения (k разрядность полей R и R ij в командном слове), коммутатор 41 адреса, два ком мутатора 42, счетчик 43 команд, счетный вход которого соединен с вшной 44 счета. Вход результата блока 3 регистров соединен с первым входом коммутатора 42-1, с вторым входом коммутатора и с входами регистров ,eгo назначения. Вход регистра 40 общего назначения соединен с выходом коммутатора 42,второй вход которого соединен с информационным входом блока регистров, третий управляющий вход которого соединен с управляющим входом коммутатора 42/1 . Вход стробов блока 3 регистров соединен с синхронизирующими входами регистров 40 общего назначения, выходы которых соединены с первой и второй группами выходов 17 и 18 блока 3 регистров, второй управляющий вход которого соединен с управляющим входом коьв4утатора 42, выход которого соединен с входом регистра 40i2 обще го назначения, выход которого соединен с первым входом коммутатора 41 второй Ьход которого соедиадреса, нен с выходом регистра 40.общего на значения. Выход коммутатора 4 адреса соединен с входом счетчика 43 команд и с адрес1В 1м выходом 22 блока 3 регистров, первый управляюв й вход к торого соединен с управляющим входом коммутатора 41 адреса, третий вход которого соединен с выходом регистра 40о общего назначения. Выход счет чика 43 команд соединен с первым входом коммутатора 42.. Блок 4 режимов (фиг. З) содержит двухразрядный сдвиговый регистр 45, трехразрядный сдвиговый регистр 46, двухразрядный сдвиговый регистр 47, триггер 48, дешифратор 49 признака адресации, элементы И 50-54, элемент ИЛИ 35, инверторы 56-58, элемент И 59, элементы ИЛИ 60-64 и элемент И 65, образующий выход 66. Элементы ИЛИ 63 и 64 образуют соответст венно выходы 67 и 68. Первый и второ разряды сдвигового регистра 45 образуют выходы 45 и 45,2, Первый, второй и третий разряды сдвигового регистра 46 образуют выходы 46 - 46. Первый и второй разряды сдвигового 0 . 10 регистра 47 образуют выходы 47 и 47, Выход триггера 48 образует выход 48. Синхронизирующие входы сдвиговых регистров 45-47 и триггера 48 соединен с тактовым входом блока 4 режимов, вход конца команды которого соединен с вторыми входами элементов И 50-53, 65 и третьим входом элемента ИЛИ 61, выход которого соединен с вторым выходом 25 блока 4 режимов, первый выход 24 которого соединен с ийходом элемента ИЛИ 60 и элемента И 59, второй вход которого соединен с выходом инвертора 58, вход которого соединен с входом признака блока 4 режимов, третий выход 26 которого соединен с выходом элемента ИЛИ 62. Входы дешифратора 49 признака адресации соединены с двухразр5здным полем признака адресации кодового входа блока 4 режимов. Входы элементов И 54 соединены с разрядами кодового входа блока 4 режимов, за исключением штадшего разряда, соответствующими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 4 режимов, соответствукнцими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 4 режимов, за исключением младшего разряда, соответствующими полю 2 в командном слове. Входы элемента ИЛИ 55 соединены с разрядами кодового входа блока 45 режимов, соответствующими полю 2 в командном слове. Первый вход элемента И 65 соединен с первым выходом дешифратора 49 признака адреса1Д1и, второй выход которого соединен с первыми входами элементов И 52 и 53. Третий вход дешифратора 49 признака адресации соединен с первыми входами элементов И 50 и 51. Выход элемента И 54 соединен с третьим входом элемента И 53 и через инвертор 57 с третьим входом элемента И 52. Выход элемента ИЛИ 55 соединен с третьим входом элемента И 51 и через инвертор с третьим входом элемента И 50. Выходы элементов И 50-53 соедипемы соответственно с последовательшлш входами сдвиговых регистров 45-47 и дом триггера 48. Входы элемента ШШ 60 соединены с выходами 45 j, 4б( и 47. Первый вход элемента И 59 соединен с выходом . Первый и второй входа элемента ИЛИ 61 соединены с выходами 45 и 46. Входы элемента ШШ 62 соединены с выходами 45-( , 45, 46, I 1 48. Входы элемента ИЛИ 63 46., 47r 3 a выходами 48) и 47г2. Входы о.оединены с 64 соединены с выходаэлемента lUU-l ми 451, (Ъ 7| и 48. Выходы 47. 46о и 67 образуют четвертый выход т Выходы 45. PSXOiMOB. .LID1.W/J,D1 fJ./( ) ) , и 67 образуют шестой выход 29 блока 4 режимов. Выходы 46f и 68 обра зуют седьмой выход 30 блока 4 режимов Блок 5 триггеров кодов операций (фиг.4) содержит дешифратор 69 кодов операций и m триггеров 70 кодов операций уп - число команд, используемой системы комавд), выходы В..,,.. . ,В, ко торых образуют выход 32 блока 5 триггеров кодов операций, синхронизирующий вход которого соединен с синхронизирукщими входами триггеров 70 кодов операций, входы которых соединены с выходами дешифратора 69 кодов операций, входы которого соединеШ) с кодовым входом блока 5 tpHrrepoa кодов операций, соответствуквчим полю кодов операций в командном слове. Блок 6 подключения регистров операндов (фиг. 5) содержит регистр 71 для хранения полей Й-, и командного слова, первую группу из К элементов И 72, вторую группу из К элементов И 73, триггера 74, два элемента И 75, элемент ИШ 76 и два инвертора 77, Выход 46, соединенный с управляю щим входом блока 6 подключения регис ров операндов, через инвертор 77j со единен с BToptJtfii входами первой груп пы элементов И 72, выходы которых со единены с первым управлянесим выходом 19 блока 6 подключения регистров операндов, второй управляющий выход которого соединен с выходами второй группы элементов И 73, входы т«з торых соединены с выходом триггера 74, сннхронизирукшшй вход которого соединен с выходом элемента ИЛИ 7 Выход элемента И 75 соединен с входо элемента ИЛИ 76, с синхронизирующим входом регистра 71 и с синхронизирую щим выходом 31 блока 6 подключения регистров операндов, вход конца команды которого соединен с первым вхо дом элемента И 75. Выход 68, соедине ный с управляющим входом блока 6 под ключения регистров операндов, соединен с первым входом элемента И 75 и через инвертор 77 соединен с входом триггера 74. Первые входы первой гру пы элементов И 72 соединены с выхода ми поля Й-1 регистра 71, выходы поля Р(2 которого соединены с первыми входами второй группы элементов И 73, при этом выход младшего разряда поля регистра 71 соединен с выходом 38 признака блока 6 подключения регистров операндов, кодовый вход которого, соответствующий полям R и R« ко-, мандного слова, соединен с входами регистра 71. Второй вход элемента ИЛИ соединен с выходом элемента И 75п, второй вход которого соединен со вторым входом элемента И 75 и с тактовым входом блока 6 подключения регистров операндов. Блок 7 формирования стробов (фиг.6) содержит коммутатор 78, дешифратор 79 записи, элемент ИЛИ-НЕ 80, элементы Ш1И 81. 82п, 81 1, uij, 01 и элементов И 82, выходы 2 lp-2)j..которых соединены с выходом 21 стробов блока 7 формирования стробов, первый кодовый вход которого соединен с первой группой входов коммутатора 78, вторая группа входов которого соединена со вторым кодовым входом блока 7 формирования стробов, вход конца команды которого соединен с входом элемента ИЛИ-ИЕ 80 и с четвертым входом элемента ШШ 81 2) второй и третий входы которого соединены с выходами 45.. и 46 , соединенньв4и с первым управляющим входом блока 7 формирования стробов, второй управляю1дий вход которого соединен с входом элемента HJBfНЕ 80 и с четвертым входом элемента ИЛИ 81, третий и второй входы которого соединены со входами элемента ИЛИ-НЕ 80 и с выходами 4оп и соединенными с первым управляювдам входом блока 7 формирования стробов. Выход элемента ШШ-НЕ 80 соединен с первым входом элемента ШШ ВЬ, выход которого соединен с дополнительным входом дешифратора 79 эаписи, входы которого соединены с выходами коммутатора 78, управляющий вход которого соединен со вторым входом элемента ИЛИ 81j и с выходом 67, соединенным с первым управляющим входом блока 7 формирования.стробов, третий управляющий вход и тактовый вход которого соединеШ) со вторыми и третьими входами элементов И 82. Первьй выход дешифратора 79 записи соединен с первым входом элемента ИЛИ 8Ц, выход которого соединен с первым входом элемента И 82.. К Первые входы элементов И 82.-82п соединены с 2-(2 -1) -ми выходами 13 дешифратора 79 записи, выход которого соединен с первым входом элеitмента И 82(). Блок 8 управления (фиг. l) содержит сдвиговый регистр 83 управления, сборки 84 и 85, сборок 86 (2 - количество управляющих микроопераций операционного блока 1), сборку 87, р сборок 88 (р - определяется числом выходов результатов операционного бл ка 1,таких как сумма, поразрядная поразрядныи перенос и т.п., сумма. причем 2 : числа выходов результатов), элементов И 89, элементов И 90 B-t-c+d+e элементов И 91, элементо-в И и h+ .. . + q элементов И 93. Выходы сдвигового регистра 83 управления образуют п выходов Л, где п определяется числом машинных цикло для выполнения самой длинной команды из системы команд. Числа а, в, с, d, е, д, h,...,q определяются числом ко манд из системы команд, в которых вы рабатываются управляющими микроопера ции на выходах соответствукжцих сборок. Кодовый вход блока 8 управления соединен с выходами В,...,В тригге ров 70 -70УП кодов операций. Выход 46ij, соединенный с вторым управляющим входом блока 8 управления, соединен с входами сборок 84, 86 и 86ij. Выход 67, соединенный, с вторым управляющим входом блока 8 уп равления, соединен с входами сборок 86 и 86IJ. Выход 47 , соединенны с вторым управляющим входом блока 8 управления, соединен с входом сборки 86( и входом сборки 84, выход которой соединен с четвертым выходом 3 блока 8 управления, тактовый вход ко торого соединен с синхронизирующим входом сдвигового регистра 83 управления, вход которого соединен с третьим управляющим входом блока 8 управления, первый управляющий вход ко торого соединен с входами сборок 84 и 87. Выходы сборки 87 и элемента И 9 соединены с первым выходом 35 блока управления, второй выход 36 которого соединен с выходами сборок 86,(,...86 Выход сборки 85 соединен с входами сборок 84 и 87, управляющим входом сдвигового регистра 83 управления и с выходом 33 конца команды блока 8 управления, третий выход 37 которого соединен с выходами сборок 88xi, .. ,, 88р. Первые входы элементов И ,. .. , 89i соединены с выходами А,...,Aj 0 сдвигового регистра 83 управления, вторые входы элементов И 89,...,89 соединены с выходами В,..., триггеров 70 кодов операций, а выходы элементов И 89 ,... ,89г соединены с входами сборки 84, Первые и вторые входы элементов И 9С1, ,...,90а соединены соответственно с выходами А- ,..., А; сдвигового регистрв 33 управления и В, ,Bt триггеров 70 кодов операций, а выходы элементов И 90,, ...,90о соединены с входами сборки 85, дополнительный вход которой соединен с выходом А последнего разряда сдвнгового регистра 83 управления. Входы элементов И 91,...,91g соединены ответственно с выходами А,...,А; сдвигового регистра 83 управления и В,...,Б триггеров 70 кодов операций, при этом выходы элементов И 91i,...,91q) соединены со входами сборки 86, выходы элементов И 91,., . ,91 с. - со входами сборки 86, выходы элементов И 9 ..., 91 а - со входами c6optcH 86,, выходы элементов И 9||,...,91g со входами сборки 86. Первый вход элемента И 92 соеди - иен с вьпсодом 68 элемента ШШ 64 блока 4 режимов, подключенного-через седьмой выход 30 блока 4 режимов к четвертому управляющему входу блока 8 управления. Второй вход элемента И 92 подключен к выходу Be триггера 70 кода операции, соответствующему ко манде Запись в Память. Первый и вторые элементов И 92|j,.. .,92 соедине{ш соответственно с выходами A:J,...,AJ сдвигового регистра 83 управления и выходами В,ч,...,В триггеров 70 кодов операций, а выходы элементов И 92,...,92 соединены со входами сборки 87. Первые и вторые входы элементов И 93,. .. ,93 ( сое.динены соответственно с выходами А,...,А} сдвигового регистра 83 управления и с выходами Bj.,..,,B триггеров 70 кодов операций, при этом выходы элементов И 93,...,93 соединены со входами сборки 88,..J 88р, выходы элементов И 93,... ,93 соединены с входами сборки 88р. Индексы , j, г и t - переменные , значение которых может принимать от единицы до п для i и j и от единицы до m для С и t и определяются алгоритмами выполнения каждой конкретной команды из системы команд. сли для вьтолнения некоторой команды в соответствующем машинном цикле ее выполнения необходимо выработать определенную микрооперацию, то на выходе соответствующей сборки устанавливается элемент И, на входы которых поступают выходы триггера кода операции и соответствукяцего разряда сдвигового регистра 83 управления. Сборка 86-1 обеспечивает подачу в операционный блок 1 первого операнда прямым кодом, сборка 86 обеспечивает подачу в операционный блок } второго операнда прямым кодом, сборка 86-j обеспечивает подачу единицы переноса в младший разряд для операционного блока } и т.д. Сборки 88,...,88р обеспечивают настройку коммутатора 12 результата на пропускание результата в блок 3 регистров с соответствующего выхода операционного блока 1. Сборка 84 обеспечивает разрешение записи информации в регистры 40 общего назначения. Сборка 87 служит дл выработки сигнала обращения к памяти, а элемент И 92 служит для выработки сигнала записи в блок 2 па мяти. Сборка 85 служит для выработки сигнала в конце выполнения каждой ко манды. Соединение выхода АП сдвигово го регистра 83 управления непосредст RP.HHO со входом сборки 85 для исключения прекращения работы центрального процессора при ошибках при программировании, когда программист потребует выполнения команды, отсутствующей в системе команд, при которой не включится ни один из триггеров 70 кодов операций. Сдвиговый регистр 83 управления (фиг. 8) содержит элемент ИЛИ 94, 1 триггеров 95, П элементов И 96, эл мент ИЛИ-НЕ 97 и инвертор 98,- выход которого соединен с вторьм входом элемента И 96, первый вход которого соединен с выходом элемента ИЛИ 94, первый вход которого соединен с выходом 66, соединенным с входом сдвиг вого регистра 83 управления, синхронизирующий вход которого соединен с синхронизирующими входами триггеров , входы которых соединены с выходами элементов И 96/(-96у). Второй вход элемента ИЛИ-НЕ 97 с единен со вторым входом элемента ИЛИ и с выходом 68, соединенным с входом сдвигового регистра 83 управления, управляющий вход которого соединен . ,( с первым входом элемента ИШ1-НЕ 97, выход которого соединен со вторыми входами элементов И 96п-96, первые входы которых соединены соответственно с выходами триггеров 95х,-95ц.. Выходы триггеров 95-,-95у1 образуют выходы сдвигового регистра 83 управления .. Коммутатор 41 адреса (фиг. 9) содержит дешифратор 99 и элемент И-ИЛИ 100, выход которого соединен с выходом коммутатора 41 адреса, первый,второй и третий входы которого соединены с первыми входами соответственно первого, второго и третьего вентилей элемента И-ИЛИ 100, вторые входы которых соединены соответственно с первым, вторым и третьим выходами дещифратора 99, входы которого соединены с входом коммутатора 41 адреса. Триггер 48 (70, 74, 95) (фиг. 10; сосодержит элементы И-ИЛИ 101 и 102 и инверторы 103 и 104. Выход триггера 48 соединен с выходом элемента И-ИЛИ 101 и с первым входом первого вентиля элемента И-ИЛИ 101, второй вход которого соединен с синхронизирующим входом триггера 48 и с входом инвертора Ю4, выход которого соединен с входом инвертора 103 и с вторыми входами вторых вентилей элементов И-ИЛИ 10 и 102, первые входы коTopbix соединены с выходом элемента И-ИЖ Г02, второй вход первого вентиля которого соединен с выходом инвертора 103. Вход триггера 48 соединен с первм4 входом первого вентиля элемента И-ИЛИ 102. Сдвиговые регистры 45-47 выполнены на триггерах аналогичных триггеру 48, причем вход последующего разряда регистров 45-47 соединен с выходом их предьщущего разряда. Регистры 40 и 71 выполнены на триггерах аналогичных триггеру 48 (70, 74, 95). Триггер 48 (70, 74, 95) работает следующим образом. При появлении сигнала на его синхронизирукяцем входе элемент И-ИЛИ 101 запоминает состояние своего выхода, являющегося выходом триггера 48. На выходе инвертора 104 сигнал пропадает, поэтому вторые вентили злементов И-ИЛИ 101 и 102 закрыты, а сигналом, образуемым на выходе инвертора 103, первый вентиль элемента И-ИЛИ 102 открыт, при этом выход элемента И-ИЛИ 102 повторяет состояние входа триггера 48.

При пропадании сигнала на синхронизирующем входе триггера 48 первый вентиль элемента И-1-1ЛИ 101 закрывается, а на выходе инвертора 104 появляется сигнал, которьп открывает вторые вентили элементов И-ИЛИ 102 и 101, при этом элемент И-ИЛИ 102 запоминает состояние его выхода, а элемент И-ИЛИ 101 передает это состояние на выход триггера 48. Таким образом, триггер 48 представляет собой D-триггер.

Коммутатор 41 адреса работаетследуняцим образом.

При коде 00 на входе дешифратора 99 сигнал появляется только на его первом выходе, открьшая только первый вентиль элемента И-ИЛИ 100, связанный nepBhw входом с первым входом коммутатора 41 адреса. При коде 01 на входе дешифратора 99 аналогичным образом на вьлсод коммутатора 41 адреса передается только состояние его второго входа, а при коде 10 на входе дешифратора 99 на выход коммутатора 41 адреса передается только состояние его третьего входа. Причем код 00 на вход дешифратора 99 поступает при отсутствии сигналов на выходах элементов И 59 и HJBi 60 код 01 - при отсутствии сигнала на выходе элемента ИЛИ 60 и при появлении сигнала на выходе элемента И 59, а код 10 - при отсутствии сигнала на выходе элемента И 59 и появлении сигнала на выходе элемента ИЛИ 60 в блоке 4 режимов. Совместное появление сигналов на выходах элементов И 59 и ИЛИ 60 исключено.

Сдвиговый регистр 83 управления работает следующим образом.

При отсутствии сигналов на входах элемента Ш1И-НЕ 97 (соответствует отсутствию сигналов на выходе сборки 85 в блоке 8 управления и на выходе элемента ИЖ 64 в блоке 4 режимов} элемент И 96 закрыт, так как отсутствует сигнал на выходе инвертора 98 а элементы И , открыты сигналом с выхода элемента ИЛИ-НЕ 97.

Поэтому при поступлений каждого синхросигнала на синхронизирующем входе сдвигового регистра 83 управления в триггер 95 записывается нуль, а в триггеры 95 -95 состояние предшествующего ему триггера. При наличии сигнала на управляющем входе сдвигового регистра 83 управления, соединенного с выходом сборки 85, на выходе элемента ИЛИ-НЕ 97 сигнал отсутствует, а на выходе инвертора 98 вырабатывается сигнал и при появлении синхросигнала на синхронизирующем входе сдвигового регистра 83 управления в триггеры , запишутся нули, а в триггер единица, если на выходе 66 элемента И 65 в блоке 4 режимов вырабатывается сигнал и запишется нуль, если этот сигнал не вырабатывается, при этом появление сигналов на первом входе элемента ИЛИ-НЕ 97 и его втором входа, связанном с выходом 68 элемента ИЛИ 64 в блоке 4 режимов, невозмож но. При появлении сигнала на выходе 68 элемента ИЛИ 64 сигнал поступает, с одной стороны, на вход элемента ИЛИ-НЕ 97 и с другой стороны через элемент ИЛИ 94 на вход элемента И 96-1 поэтому при поступлении синхросигнала на синхронизирующий вход сдвигового регистра 83 управления в триггер 95 запишется единица, а в триггеры 95 -95п запишутся нули. По окончанию действия сигнала на управляющем входе и входе сдвигового регистра 83 управления он переходит в режим сдвига своего состояния, как описано выше.

Центральный процессор работает следующим образом.

В конце выполнения очередной команды на выходе одного из элементов И 90 вырабатывается сигнал и поступает в качестве сигнала окончание комагады (ОК) на выходе сборки 85 и соответственно на выход 33 ОК блока 8 управления. При этом сдвиговый регистр 83 переходит из режима сдвига в режим записи, на выходе сборки 84 вырабатывается сигнал и поступает на выход 39 блока 8 управления, на выходе сборки 87 вырабатывается сигнал, который с выхода 35 блока 8 управления поступает на управляющий вход блока 2 памяти в качестве сигнала обращения . На адресный вход блока 2 памяти подается адрес очередной команды (содержимое регистра 40(), так как сигналы на выходах элемента И 59 и элемента ИЛИ 60 отсутствуют и коммутатор 41 адреса пропускает код с первого своего входа на выход. Сигнал ОК, поступая на вход КК блока режимов, открьтает по первым входам элементы И 60, 50-53 и 65 и через первый вход элемента ИЛИ 61 поступает на выход 25 блока 4 режимов и дгшее на управляющий вход коммутатора 42, который обеспечивает подачу на вход регистра 40п общего назначения продвинутого значения счетчика 43 команд, так как на его вход подается код с вы хода коммутатора 41 адреса, а на его счетный вход подается сигнал с шинь 4 счета. Командное слово следующей команды с выхода 23 блока 2 памяти поступает на кодовые входы блока 4 режимов, бло ка 5 дешифрации кодов операций и блока 6 подключения регистров операндов После признака адресации командного слова поступает на дешифратор 49 признака адресации , поле 2 командного слова без его мл-адшего разряда поступает на элемент И 54 и полностью поступает на вход элемента ИЛИ 55 и на вход зоны регистра 71. Поле С/ командного слова поступает на вход зоны 1 регистра 71, а поле кода операции в командном слове поступает на вход дешифратора 69 кода операции, на одном из выходов которого вырабатывается сигнал. При этом, если поле признака адресахщи (11Л5 в командном слове следующей команды равно 00 (соответствует режиму RIK.-регистр - ре гистр - выполненная команда), то сигнал вырабатьшается на первом выходе дешифратора 48 признака адресации и через элемент И 65, его выход 66 и выход 28 блока 4 режимов поступит через элемент ИЛИ 94 на вход элемента И 96. Если ПА 01 (режим RX+1 - выполнение команды в режиме регистр - память, причем адрес второ го операнда находится в одном из регистров 40 общего назначения содержи мое которого увеличивается на единицу - магазинн,ая организация работы) , то сигнал вырабатывается на втором выходе дешифратора 49 ПА и открывает по вторым входам элементы И 52 и 53, причем при равенстве поля Pij кодам 1...10 или 1...П на выходе элемента И 54 вырабатывается сигнал и проходит только через элемент И 53 на вход триггера 48, при других кода в поле R(x сигнал на выходе элемента И 54 отсутствует, поэтому на выходе инвертора 57 вырабатывается сиг нал и поступает на вход сдвигового регистра 47. Если ПА 10, то сигнал вырабатывается только на третьем выходе де шифратора 49 ПА и открывает по вторы 0 входам элементы И 50 и I, причем при неравенстве поля 2 коду 0...0 на пыходе элемента ИЛИ 56 вырабатывается сигнал и проходит только через элемент И 51 на вход сдвигового регистра 46, а при равенстве поля Кг коду 0...0 на выходе элемента ИШ 55 сигнал отсутствует, а на выходе инвертора 56 сигнал вырабатывается и через элемент И 50 поступает на вход сдвигового регистра 45. Сигнал с выхода 39 блока 8 управления, поступая на элементы И 82, открывает их по вторым входам. Сигнал ОК с выхода 33 блока 8 управления, поступая на вход элемента И 75, открывает его по первому входу и поступая, с одной стороны, через элемент ИЛИ 81 на элемент И 821. открывает его по первому входу, и с другой стороны, поступая на вход элемента ИЛИ-НЕ 80, обуславливает отсутствие сигнала на его выходе и соответственно на дополнительном входе депшфратора 79 записи. При отсутствии сигнала на дополнительном входе дешифратора 79 записи сигнала на его выходах отсутствует, а при наличии еигиала на дополнительном входе дешифратора 79 записи появляется сигнал на одном из его выходов,соответствующем коду, подаваемому на его входы с выходов коммутатора 78. При появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов j во-первых, выработается сигнал на выходе элемента И 82 .-( и запишется продвинутое значение счетчика 43 команд в регистр 40./i общего назначения, во-вторых, вырабатывается сигнал на выходе элемента И 75 и. пройдя через элемент ИЖ 76, запишет 1 в триггер 74, так как сигнал на выходе 68 элемента ИЛИ 64 отсутствует, а на выходе инвертора 77 присутствует. Кроме того, сигнал с выхода элемента И 75-j запишет состояние полей R и Uij командного слова в регистр 71 и, поступая с синхронизирующего выхода 31 блока 6 подключения операндов на синхронизирующий вход блока 5 триггеров кодов операций, произведет установку в едийицу только одного из m триггеров 70 кода операции. Кроме Того, синхросигнал с тактового выхода 34 генератора 9 синхросигналов в зависимости от состояния полей ПА и 2 командного слова произве дет запись единицы либо в первый разряд сдвигового регистра 83 управления при ПА 00, либо в триггер 48 при ПА 01 и 1.,.10 или й, 1 . .. 1 Г , либо в первый разряд сдвигового регистра 47 при ПА 01 и RQ t l..,10 или Ra 4t 1...П, либо в первый разряд сдвигового регистра 46 при ПА 10 и RQ 0. ..О либо в первый разряд сдвигового регистра 45 при ПА 10 и Rij О.,.0 При этом заканчивается действие всех управляювщх сигналов вырабатываемых предыдущей командой и начинается действие управляющих сигналов, вырабатываемых вновь принятой командой, Если команда выполняется в режиме Sft, то в первом цикле выполнения команды сигнала В, с выхода соответству щ.его триггера 70 кода операции и сигнал А yj с выхода сдвигового регистра 8 управления обеспечивают выработку соответствукицих управляюасих сигналов требуемых по алгоритму выполнения дан ной команды (совпадение сигналов А и В на входах соответствукмдих элементов И 89-93 и подача сигнала через соответствующие сборки 84-88 на выходы 33, 35-37, 39 блока 8 управления) . При этом первый операнд подается на первый информационный вход операционного блока 1 с одного из регистров 40 общего назначения через коммутатор 10 первого операнда (номер регистра 40 общего назначения подается с выхода поля R регистра 71 через элементы И 72 на управляющий вход коммутато ра 10 первого операнда, причем, код 0. ..О для поля Я.1 не используется. Аналогичнь образом код поля Я| регис ра 71, поступая через элементы И 73 на управляющий вход коммутатора I второго операнда, обеспечивая подачу второго операнда с соответствующего регистра 40 общего назначения на второй информационный вход операционного блока 1, который преобразует данные операнды в соответствии с кодом поступивщим на его управляющий вход с выхода 36 блока 8 управления (выходы сборок 86--86g) . Если выполняемая команда выполняется за один машинный цикл, то в первом iijtiKne выполнения команды на одном из выходов 15 операционного блока 1 (выход Суммы, Поразрядной суммы, Поразрядного переноса и т.п.) присутствует результат, причем на выходах соответствующих элементов И 93 вырабатываются сигналы, ко- торые формируют на выходе 37 блока 8 управления код, соответствующий этому требуемому результату. Данный код обеспечивает подачу результата через коммутатор 2 результата на входы коммутаторов 42 или регистров ( общего назначения в блоке 3 регистров. В этом цикле один из элементов И 89 вырабатывает сигнал, который, пройдя через сборку 84, открьшает по вторым входам элементы И 82. На выходе 67 элемента ИЛИ 63 сигнал отсутствует, поэтому код поля р . регистра 71 через коммутатор 78 подается на входы дешифратора 79 записи, на дополнительном входе которого присутствует сигнал, nosToity сигналом с соответствующего выхода дещифра1ора 79 записи открыт по первому входу тот элемент И 82, выход которого соединен с синхронизируюпщм входом регистра 40 общего назначения, в котором находится первый операнд, поэтому при появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов, результат запишется на место первого операнда. Кроме того, если данный цикл выполнения команды является последним ее циклом, то на выходе сборки 85 вырабатывается сигнал ОК, при этом выполнится выборка следующего командного слова, аналогично описанному. Если данный цикл выполнения комавды не является последним, то после его выполнения синхросигнал с тактового выхода 34 генератора 9 синхро сигналов сдвинет единичный сигнал во второй разряд сдвигового регистра 83 управления и так далее до конца вьгполнения команды, который определяется наличием сигнала ОК на входе сборки 85. Если команда выполняется в режиме Х пр:я Rii 0...0, то вютолнение команды начнется с режима выборки второго операнда, в первом цикле которого на выходе Д5 сдвигового регистра 45 вырабатглвается сигнал, по которому на выходах 25, 26 и 29 блока 4 релсимов вырабатываются сигналы. Сигнал на выходе 25 блока 4 режимов настраивает коммутатор 42j на пропускание кода с выхода счетчика 43 команд на вход регистра 401 общего назначения. Сигнал с выхода 26 обеспечивает выработку, во-первых, сигнала обращения к памяти на выходе сборки 87 и поступающего на управляющий вход блока 2 памяти, во-вторых, сигнала на выходе 39 блока 8 управления, обеспечивающего отпирание элемен тов И 82 по второму входу, в-третьих настраивает коммутатор 42i на пропускание информации с выхода 23 блока 2 памяти на вход регистра 40 о общего на значения, в-четвертых, сигнал на выхо де элемента ИЛИ 81/ обеспечивает отпи рание элемента И 82о по первому входу в-пятых, обеспечивает отсутствие сигнала на выходе элемента ИЛИ-НЁ 80 и соответственно на дополнительном входе дешифратора 79 записи, что обеспечивает отсутствие сигналов на всех его выходах. Кроме того, сигнал с выхода 45/1 , поступая на вход элемента ИЛИ 81 о, обеспечивает отпирание эле мента И 82(),по первому входу. Отсутствие сигнала на выходе 24 блока 4 режимов обеспечивает подачу адреса Смещения с выхода регист ра 40п через коммутатор 4J адреса н адресный вход блока 2 памяти и на вход счетчика 43 команд, на счетш }й вход которого с шины 44 счета поступает сигнал. Командное слово и Смещение для формата R X занимают две смежных ячейки памяти, причем, в фор мате Я X при RQ 0...0 Смещение является исполнительным адресом второго операнда. При появлении синхросигнала на тактовом выходе 34 генера тора 9 синхросигналов, во-первых, вы рабатывается синхросигналы на выходах 21« и 2( элементов И 82о и 82 и производится запись Смещения в регистр 40д общего назначения и про двинутого значения счетчика 43 команц в регистр 40(j,x, и, во-вторых, сдвигает единичный сигнал с первого во второй разряд сдвигового регистра 45, после .чего начинается второй цикл выполнения режима ЯХ при Rij. П П - V/ « k V « Во втором цикле режима RX при Яс O...D сигнал с выхода 45 сдвигового регистра 45 обеспечивает, вопервых, выработку сигнала на выходе элемента ИЛИ 60, по которому коммутатор 41 адреса пропускает исполнительный адрес второго операнда с регистра 40(3 общего назначения на адресный вход блока 2 памяти. Во-вторых, вырабатывается сигнал на выходе 68 элемента ИЛИ 64, который с вых да 30 блока 4 режимов поступает на первый вход элемента И 75Q и открывает его по этому входу, а на входе 024 триггера 74 сигнал снимается. Кроме того, сигнал с выхода 68 поступает на входы элемента И 92 и элементов ИЛИ 94 н ИЛИ-НЕ 97. В-третьих, вырабатывается сигнал на выходе элемента ИЛИ 62 и соответственно на выходе 26 блока 4 режимов. Работа, производимая сигналом на вьгходе 26 блока 4 режимов, описана выше. При появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов, во-первых, вырабатывается синхросигнал на выходе 21 о элемента И 82(5, по которому второй операнд с выхода 23 блока 2 памяти записывается в регистр 40о общего назначения, во-вторых, вырабатывается сигнал на выходе элемента И 75ij и, пройдя через элемент ИЛИ 76, запишет нуль в триггер 74, который при этом закроет элементы И 73, в-третьих, выдвинет единицу из сдвигового регистра 45 и запишет единицу в первый разряд сдвигового регистра 83 управления, после чего процессор начнет выполнение команды, которое происходит аналогично ранее описанному выполнению команды в режиме Rft , за исключением того, что второй операнд подается ла операционный блок 1 не из регистра 40,- общего назначения, определяемого кодом в поле R , а из регистра 40о общего назначения, так как на выходе элементов И 73 сигналы отсутствуют (нулевой код) . Если комавда выполняется в режиме RX при Я(1 ф 0...0, то выполнение команды начнется с режима выборки второго операнда по исполнительному адресу являющемуся суммой Смещения и индекса - содержимого регистра 40 общего назначения, где i - код в поле Йг1 командного слова (поле R(j регистра 71) В первом цикле выполнения данного режима сигнал присутствует на выходе 461 сдвигового регистра 46. Выполнение первого цикла в данном режиме производится аналогично выполнеютю первого цикла режима RX при ti 0...0, после чего происходит переход к выполнению второго цикла, который определяется наличием сигнала на выходе 46 сдвигового регистра 46. Во втором цикле сигнал с выхода во-первых, через выход 30 блока 4 режимов поступает на вход инвертора 77л и запрещает срабатывание элементов И 72, что обеспечивает подачу 25 смещения с выхода регистра 40д общего назначе.ния на первый информационный вход операционного блока 1. Во-вторых, сигнал с выхода 6i, поступая через выход 29 блока 4 режимов на вход элемента Ш1И-НЕ 80, запрещает отсутствием сигнала на выходе элемента ИЛМ ВЦ выдачу сигналов со всех выходов дешифратора 79 записи и, поступая на вход элемента ИЛИ 81, открывает элемент И 82 по первому (входу. В-третьих, сигнал с выхода 46 поступая через выход 27 блока 4 режимов на входы сборок 84, 86- и 86 обеспечивает выработку сигналов на их выходах. При этом сигнал с выхода сборки 84 открывает элемент И 82 о по второму входу. Сигналы с выходом сборок 86,, и 862 поступаюпше через выход 36 на управляющий вход операционного блока, обеспечивают соответствен но подачу первого и второго операндов в операционный блок 1 прямым кодом, при этом на первом своем выходе операционный блок 1 вырабатывает код,рав- 5 ный сумме кодов на первом и втором информационных входах операционного блока 1.

На выходах сборок 88 сигналы отсутствуют, поэтому нулевой код с выхода 37 блока 8- управления настраивает коммутатор 12 результата на пропускание кода с первого выхода операционного блока 1 на вход результата блока 3 регистров. Этот код (исполнительный адрес второго операнда) через коммутатор 42i поступает на вход регистра 40(j общего назначения. Синхросигнал с тактового выхода 34 генератора 9 синхросигналов, во-первых, обеспечивает запись исполнительного адреса в регистр 40о общего назначения и, во-вторых, производит сдвиг единичного сигнала со второго в третий разряд сдвигового регистра 46, после чего сигнгш вырабатывается на его выходе 46о, и происходит переход к вьтолнению третьего цикла данного режима, который выполняется аналогично второму циклу режима при Я) 0.. .0 и-описанному вьше. После третьего цикла вьтолнения режима при Я 0...0 происходит переход к выполнению команды аналогично выполнению в режиме RR, , причем второй операнд подается на второй информационный вход операционного блока 1 с регистра 40о общего назначения.

дах элемента И 59 и элемента ИЛИ 60 отсутствуют, поступают через вход первого коммутатора 42 в блоке 3 регистров на вход регистра 40р общего назначения. Сигнал с выхода сборки 84 открывает по второму входу элементы И 82 в блоке 7 формирования стробов. Кроме того, сигнал с выхода 47, поступает через элемент ШИ 8 Ц на первый вход элемента И 82р. Элементы И 82 -82( по первому входу закрыты отсутствием сигналов на выходах дешифратора 79 записи, так как сигнал с выхода 47. через элемент ИЛИ-НЕ 80 запрещает отсутствием сигнала на выходе элемента ИЛИ 81з срабатывание дешифратора 79 записи.

При выработке синхросигнала на тактовом выходе 34 генератора 9 синхросигналов код содержимого регистра 40(R( общего назначения запишется в регистр 40 о общего назначения сигналом с выхода 21Q элемента ИЛИ 82Q и единица из первого разряда регистра 47 переместится во второй разряд, после чего процессор перейдет к выполнению второго цикла выполнения

описываемого режима, который определяется сигналом с выхода 475 сдвигового регистра 47. 0 Ес:ш комагзда выполняется в режиме И -И при R(i 1...10 и RQ 5 I . . , 1 1 , то выполнение команды начинается с режима выборки второго операнда по исполнительному адресу, расположенному в регистре 40 i общего назначения,где V задается полем R командного слова. При этом после окончания выполнения предыдущей команды установится в единичное состояние первый разряд сдвигового регистра 47 который определяет выборку второго операнда из блока 2 памяти в данном режиме. В первом цикле вьтолнения данного режима сигнал с выхода 47 сдвигового регистра 47 обеспечивает выработку сигналов на выходах сборок 84 и 86о Б блоке 8 управления. Сигналс выхода сб-орки 86 ij обеспечивает подачу прямьм кодом в операционный блок 1 с его второго информационного входа операнда - содержимого регистра 40 общего назначения, номер которого задан в поле RQ регистра 71. Сигналы на выходах остальньтх сборок 86 отсутствуют, поэтому данный операнд неизменным поступает на выход Суммы операционного блока 1 и через коммутатор 12 результата, так как сигналы на выхоВо втором цикле выполнения данног режима сигнал с выхода 47/2 обеснечивает выработку сигналов на выходе 68 элемента ИЛИ 64, на выходе 67 элемен та ИЛИ 63, на выходе элемента ИЛИ 62 и на выходе элемента ИЛИ 60. Отсутствие сигнала на выходе элемента И 59 и сигнала А на выходе элемента ИЛИ 60 обеспечивают настройку коммутатора 4 адреса на подачу кода адреса второго операнда с выхода регистра 40 на адресный вход блока 2 памяти. Сигнал с выхода 26 блока 4 режимов, во-первьгх, поступая на управляющий вход ком мутатора 42, настраивает его на пропускание информации на вход регистра 40о общего назначения с выхода 23 блока 2 памяти, во-вторых, поступая на вход элемента ИЛИ 81 отпирает по первому входу элемент И 82р, одновре менно, поступая на вход элемента 80, снимает сигнал с его выхода и, в-третьих, с одной стороны поступая на вход сборки 84 сигналом с ее выхода отпирает элементы И 82 по вторым входам и, с другой стороны поступая на вход сборки 87, вырабатывает сигнал на ее выходе, который в качествесигнала обращения поступает на управляющий вход блока 2 памяти, обеспечивает выборку второго операнда, который с выхода 23 блока памяти поступает на вход регистра 40 общего назначения. Сигнал с выхода 6 элемента ИЛИ 63, во-первых, поступая на вход коммутатора 78, нас.траивает его на пропускание на входы дешифратора 79 записи кода с выхода поля 2 регистра 71, поступакндего на входы коммутатора 78 через элементы И 73 -73j(, так как на выходе триггера 74 присутствует сигнал. Во-вторых, сигл;ш с выхода 67, поступая на вход элемента ИЛИ 81l, обеспечивает выработку сигнала на одном из выходов дешифратора 79 записи, который откры вает по первому входу один из элемен тов И ( (в данном режиме,исполнение которого производится сдвиговым регистром 47, код 0...0 в поле Rft в общем случае не использует ся, так как регистр 40 общего назна чения служит для выработки исполнительного адреса второго операнда). В-третьих, сигнал с выхода 67, посту пая на входы сборок 86 ij и 860, обеспе чивает выработку сигналов на их выхо дах, при этом сигнал с выхода сборки 86 обеспечивает подачу единицы . 28 переноса в штадший разряд операционяого блока 1, а сигнал с выхода сборки 86f обеспечивает подачу в операционный блок I прямым кодом операнда с его второго информационного входа. Причем на втором информационном входе операционного блока I присутствует содержимое регистра 40 общего назначения (код i с выхода поля регистра 71 через элементы И ,, поступая на вход коммутатора I1 настраивает его на подачу содержимого регистра 40, общего назначения на второй информа1Д1онный вход операционного блока ). При этом на выходе Суммы операционного блока I вырабатывается код, равный сумме содержимого регистра 40| и единицы младшего разряда. На выходах сборок сигналы отсутствуют, поэтому комнутатор 12 результата пропускает код с выхода Суммы операционного блока 1 на входы регистров 40 -40 « общего назначения. Сигнал с выхода 68 элемента ИЛИ 64, во-пери 1х, поступая на вход инвертора 77 в блоке 6 подключения операндов снимает сигнал с входа триггера 74 с одной стороны, а поступая на вход элемента И 72 открывает его по первому входу. Во-вторых, сигнал с выхода 68 элемента ИЛИ 64 через выход 28 блока 4 режимов поступает на вход сдвигового регистра 83 управления, настраивает его на запись сигнала в его первый разряд. При появлении синхросигнала на тактовом выходе 24 генератора 9 синхросигналов в конце выполнения второго цикла режима R +1 при Rn 1...1 О и Rf I...lt, во-первых, в регистр 40, общего назначения (i код в поле RIJ регистра 71) записывается увеличенное на единицу его предыдущее состояние, во-вторых, в регистр 40, общего назначения записывается второй операнд, в-третьих, на выходе элемента И 75п в блоке 6 подключения регистров операндов вырабатывается синхросигнал, который обеспечивает запись нуля в триггер 74 это обеспечивает подачу на второй информационный вход операционного блока 1 операнда не с выхода регистра 40, а с выхода регистра 40(общего назначения на протяжении времени собственно выполнения операции), в-четвертых, в сдвиговый регистр 83 управления запищется единица только в первый разряд и, в-пятых, выталкивается сигнал со второго разряда сдвигового регистра 47, после чего сдвиговый регистр 8 управления, переведенный в режим сдвига, обеспечивает собственно выполнение самой операции (тип операции указывает сигнал с выхода одного из триггеров 70 кода операции).

Если команда выполняется в режиме RX+1 при RI 1...10 или Ri 1 ,. . 1 1 , то выполнение команды начинается с режима выборки второго операнда по исполнительному адресу,расположенному в регистре 40пп или регистра 40п,общего назначения.

Если в этом режиме R г 1 . ., 11 , то исполнительный адрес второго операнда указывается в регистре 40а., являкяцшся регистром хранения для счетчика 43 команд поэтому этот случай данного режима соответствует режиму RI, когда второй операнд располагается в самом командном слове и командное слово занимает две смежных ячейки памяти. Таким образом, номинально, не имея режима Я в режимах выполнения команд, предложенный процессор реализует и этот режим.

Для выполнения режима R X +1 при R 1.,.10 или Ri 1. ..П. в конце выполнения предыдущей команды включается триггер 48, сигнал с выхода 48 которого управляет данным режимом и обеспечивает выработку сигналов на выходе 68 элемента ИЛИ 64, выходе 67 элемента ШШ 63 и выходе элемента ИЖ 62 (выход 26 блока Д режимов). Если в данном режиме RQI 1...10, то на выходе младшего раряда поля К регистра 71 сигнал от, сутствует, а на выходе инвертора 5§ в блоке 4 режимов сигнал присутствует, поэтому сигнал с выхода 48 обеспечивает выработку сигнала на выходе элемента И 59, который, поступая на управляющий вход коммутатора 41 адреса, обеспечивает подачу адреса второго операнда с регистра 401.г ° щего назначения на адресный вход блока 2 памяти. Если Rrj 1...11, то на выходе 24 блока 4 реяммов сигналы отсутствуют и на адресный вход блока 2 памяти поступает адрес с выхода регистра 40(j. общего назначения .

Сигнал с выхода 26 блока 4 режимов, во-первых, поступая через сборку 84, выход 39 блока 8 управления на входы элементов И 82 в блоке 7

стробов, открьшает их по вторым входам, во-вторых, поступая через сборку 87, выход. 35 блока 8 управления на управляюпшй вход блока 2 памяти,

обеспечивает выборку второго операнда, который с выхода 23 блока 2 памяти через коммутатор 42, настроенный сигналом с выхода 26 блока 4 режимов, поступает на вход регистра 40 о общего назначения. В-третьих, сигнал с выхода 26 блока 4 режимов, поступая на вход элемента ИЛИ 81, в блоке 7 формирования стробов, откривает по первому входу элемент И 82, одновременно снимается сигнал с выхода элемента ИЛИ-НЕ 80.

Сигнал с выхода 67 элемента ИЛИ 63, во-первых, поступая через выход 29 блока 4 режимов на вход коммутатора 78, разрешает поступление содержимого поля R( регистра 71, прошедшего через элементы И 73, через коммутатор 78, на входа дешифратора 79 эаписи. Так как сигнал с выхода 67 по ступает через элемент ИШ1 8Ц на дополнительный вход дешифратора 79 записи, то он вырабатывает сигнал на последнем выходе при г 1 ... 11 или на предпоследнем выходе при Rij 1.,.10, который соответственно откроет по первому входу элемент И 82 пройдя через элемент ИЛИ 81п или элеt

мент И 821.. Во-вторых, сигнал с выхода 67 элемента ИЛИ 63, поступая-через выход 27 блока 4 режимов на входы сборок 861J,, обеспечивает, аналогично описанному ранее второму циклу режима Ry+ при Rij. Ф 1...1I или RQ 1...10, увеличение на единицу в операционном блоке I содержимого регистра 40.ij (.при 5. 1 . .. или регистра 40Q(j (.при . .. 10 , которое подается на второй информационный вход операционного блока 1 через коммутатор 1, настроенный соответствующим образом содержимым поля 2 регистра 71. Это увеличенное на единицу содержимое регистра 40(.,, () с выхода Суммы операционного блока 1 через коммутатор 12 результата, настроенный соответствующим образом отсутствием сигналов на выходах сборок 88, поступает на входы регистров 40-40ij-ft и через коммутатор 2г, так как сигнал на выходе 25 блока 4

5 режимов отсутствует, на вход регистра 40п. общего назначения.

Сигнал с выхода 68 элемента ИЛИ 64, во-первых, открьшает элемент И 75, по первому входу и снимает сигнал с входа триггера 74, во-нторых, настра ивает сдвиговый регистр 83 управления на запись единичного сигнала в его первый разряд. При появлении синхросигнала на та товом выходе 34 генератора 9 синхросигналов в конце выполнения цикла режима R У +1 (RQ 1 ,. .11 или Rj, . .. 10) , во-первых, в регистр 40г;) при Яг 1...1I или регистр QO-I Р Ч - 1...IO запишется уве личенное на единицу его предьщущее состояние, во-вторых, в регистр 40Q запишется второй операнд, в-третьих, в триггер 74 запишется нуль, который обеспечит во время выполнения команды подачу второго операнда на второй информационный вход операцион ного блока 1 с регистра 40о общего назначения, в-четвертых в первый раз ряд, сдвигового регистра 83 управления запишется единичный сигнал и, в-пятых, обнулится триггер 48, после чего сдвиговый регистр 83 управления переходит в режим сдвига и обеспечивает выполнение команды, указанной одним из триггеров 70 кода операции. При выполнении команды записи опе ранда в блок 2 памяти, задаваемой триггером 70о кода операции (выход BO, который отпирает элемент И 92) из одного из регистров 40 общего назначения, в циклах режимов, определя сигналами на выходах 45 Q, 46 j, 47n и 48xj, когда вырабатывается сигнал на выходе элемента ИЛИ 64, на вы ходе элемента И 92 вырабатьгоается сигнал, который в качестве сигигша записи поступает на управляющий вход блока 2 памяти, при зтом на информац онный вход блока 2 памяти поступает содержимое соответствующего регистра 40j общего назначения через коммутатора 10 первого операнда, настро енного соответствующим образом кодом j с выходом поля 1 регистра 71. На этом собственно выполнение команды заканчивается, а в первом цикле, определяемом сигналом в первом разря де сдвигового регистра 83 управления вырабатывается сигнал окончания команды на выходе 33 блока 8 управлени производя соответствующую работу, ка описано вьппе. .Кроме того, необходимо отметить, что регистр 40,j общего назначения, используемый как регистр хранения второго операнда во всех режимах, кр 0 использоваться в режимах Rft. для хранения операндов, но его загрузка должна производиться последней из группы загружаемых регистров и предназначенных для использования в подпрограмме, все команды которой исполняются в режиме ftR . Команда загрузки регистров 40 общего назначения кодами из блока 2 памяти также имеет один цикл, определяемый сигналом на выходе первого разряда сдвигового регистра 83 управления, при котором сигнал вырабатывается только на выходе сборки 86л(из сборок 86), обеспечивающий только подачу прямым кодом в операционный блок 1 кода со второго его информационного входа (содержимое регистра 40о общего назначения), который с выхода Суммы операционного блока 1 через коммутатор 12 результата (сигналы на выходах сборок 88 не вырабатываются) на входы регистров 40/, и Р коммутаторы и 42 (j соответственно на входы регистров 40о и 40л общего назначения. При этом при появлении синхросигнала на тактовом выходе 34 генератора 9 синхросигналов выработается синхросигнал на выходе того из элементов И 82;, который открыт по первому входу сигналом с выхода дешифратора 79 записи, определяемого кодом j в полеЙ, регистра 7). Таким образом, как показал схемнотехннческий анализ, центральный процессор позволяет при своей работе организовать аппаратное продвижение адреса второго операнда при каждом обращении к массиву данных. Кроме этого, позволяет использовать формат команды RJ не для ограниченного числа кокоманд, а для всех арифметических команд, причем длина второго операнда не ограничена одним байтом, а равна длине машинного слова. Это позволяет существенно увеличить эффективное быстродействие процессора, примерно на 30%, а также уменьшить объем разрабатываемых программ при обработке больших массиво-данных. Формула изобретения 1. Центральный процессор, содержащий операционный блок, блок памяти, блок регистров, блок подключения регистров операндов, блок формирования стробов, блок управления, генератор 338 I синхросигналов, коммутатор первого операнда, коммутатор второго операнда и коммутатор результата,причем выход коммутатора результата соединен со входом результата блока регистров, первая и вторая группы выходов которого соединены соответственно с информационными входами коммутатора первого операнда и с информационными входами коммутатора второго операнда, выход коммутатора первого операнда со единен с первым информационным входом операционного блока, выход коммутатора второго операнда соединен со вторым информационным входом операционного блока, выходы результатов которого соединеша с информационнь{ми входами коммутатора результата, тактовый выход генератора синхросигналов соединен с тактовыми входаьш блока формирования стробов, блока подклю чения регистров операндов и блока управления, первый, второй и третий выходы которого соединены соответственно с управляйщими входами блока памяти, операционного блока и коммутатора результата, адресный вход блока памяти соединен с адресньи выходом блока регистров, вход стробов которого соединен с выходом стробов бло ка формирования стробов, первый кодовый вход которого соединен с управляющим входом коммутатора первого опе ранда и с первым выходом блока подклю чения регистров операндов, второй выход которого соединен с управлянзщим входом коммутатора второго операнда и вторым кодовым входом блока формирования стробов, выход блока памяти соединен с информационным входом блока регистров и с кодовым входом блока подключения регистров операндов, информационный вход блока памяти соединен с информационным выходом коммутатора первого операнда, четвертый выход блока управления соединен с первым управлякядим входом блока формирования стробов, выход окончания команды блока управления соединен со входами окончания команды блока подключения регистров операндов и блока формирования стробов, отличающийся тем, что, с целью повышения быстродействия, в него введены блок режимов и блок дешифрации кодов операций, причем первый и второй выходы блока режимов соединены с ответственно с первым и вторым управ ляющими входами блока регистров,третии управляющин вход которого соединен со вторым управляющим входом блока формирования стробов, выходом блока режимов и с первым управляющим входом блока управления, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходом блока режимов, шестой выход которого соединен с третьим управляющим входом блока формирования стробов,управляющий вход блока подключения регистров операндов соединен с четвёрTbBvj управляющим входом блока управления и с выходом блока режимов , вход, признака которого соединен. с выходом признака блока подключенна регистров операндов,тактовый вход которого соединен с тактов№ вкодомблока режимов, вход окончашя команда которого соединен с выходом окончания команды блока управления, кодовый вход которого соединен с выходом блока дешифрации кодов операций, кодовь Й вход которого соединен с кодовым входом блока режимов и выходом блока памяти, синхронизирующий вход блока дешифрации кодов операций соединен с синхронизирующим выходом блока подключения, регистров операндов. 2. Процессор по п. 1, о т л и ч аю щ и и с я тем, что блок режимов содержит первый, второй и третий сдвиговые регистры, триггер, дешифратор, признака адресации, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И,первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, первый, второй и третий инверторы, причем nepBbrit и второй входы дешифратора являются кодовым входом блока, первый выход дешифратора соединен с первым входом первого элемента И, второй вход которого является входом окончания команды блока, второй выход дешифратора соединен с первыми входами второго и третьего элементов И, вторые входы которых соединены со вторым входом первого элемента И, третий вход второго элемента И соединен с выходом первого инвертора, вход которого соединен с третьим входом третьего элемента И и выходом четвертого элемента И, входы которого соединены с входами первого элемента ИЛИ, входы которого являются кодовым входом блока, третий выход дешифратора соединен с первыми входами пятого и шестого элементов И, вторые входы которых соединены со

вторым входом второго элемента И,третий вход пятого элемента И соединен с выходом второго инвертора, вход которого соединен с третьим входом шестого элемента И и выходом первого элемента ИЛИ, выход пятого элемента И соединен с последовательным входом первого сдвигового регистра, синхронизирующий вход которого соединен с синхронизирующими входами второго и третьего сдвиговых регистров и триггера, синхронизирующий вход которого является тактовым входом блоки,иахо- ды шестого, второго и третьего элементов И соединены соответственно с последовательными входами второго и третьего сдвиговых регистров и триггера, выходы второго, третьего, четвертого и пятого элементов ИЛИ являются соответственно первым, вторьач, третьим и четвертым выходами блока, выход первого элемента И является пятым выходом блока, первый выход первого сдвигового регистра является шестым выходом блока, выход шестого элемента ИЛИ является выходом блока, второй выход первого сдвигового регистра соединен с лервш и выходами первого сдвигового регистра соединен с первыми выходами второго и шестого элементов ИЛИ, первый выход второго сдвигового регистра соединен с первым выходом первого сдвигового регистра, второй выход второго сдвигового регистра, третий выход второго сдвигового регистра соединен со вторыми входами второго и шестого элементов ИЛИ, первый выход третьего сдвигового регистра соединен с первым выходом первого сдвигового регистра и выходом пятого элемента ИЛИ, второй выход третьего сдвигового регистра соединен с третьими входами второго и шестого элементов ИЛИ и с первым входом пятого элемента ИЛИ, выход триггера соединен с первым входом пятого элемента ИЛИ, четвертым входом шестого элемента ИЛИ и с первым вхоДОМ седьмого элемента И, второй вход которого соединен с выходом третьего инвертора, вход которого является входом признака блока, выход седьмого элемента И соединен с выходом второго элемента ИЛИ, первый, второй и третий входы третьего элемента ИЛИ соединены соответственно с первыми входами первого и второго сдвиговых регистров и со вторым входом третьего элемента И, первый, второй, третий, четвертый, пятый и шестой входы четвертого элемента ИЛИ соедииены соответственно с первым и вторым входами первого сдвигового регистра, вторым, пералм и третьим выходом второгб сдвигового регистра, вторым выходом третьего сдвигового регистра и выходом триггера, второй вход пятого элемента ИЛИ соединен с выходом триггера, а выход - с первым выходом третьего сдвигового регистра и вторым входом второго сдвигового регистра, выход шестого элемента НШ соединен с выходом первого элемента И.

Источники информации,

Принятые во внимание при экспертизе

557366, кл. G 06 F 15/00, 05.05.77.

G 06 F 9/16, 15.11.78.

J

JJ

J

Фиг.5

36

/

/If

An

Ап-1

Авторы

Даты

1981-12-15—Публикация

1980-04-07—Подача