(54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО

Ш.: ключены к выходciM второго счетчика, первые, вторые и третьи входы первых схем поразрядного сравнения присоединены соответственно к выходам первых .vaтopoв по модулю два, первым, .выходам вторых дешифраторов и выходам многока:нального переключателя, а выходы - к первым входам одноименных элементов И

, вторые входы которых соединены с вторыми выходами вТо рых дешифраторов, а выходы - с входами . элемента ИЛИ , а также тем, что второй дешифратор содержит генератор корректирующего кода, блок контроля четности, генератор логического нуля, вторую схему поразрядного сравнения, .два дополнительных элемента И , вторые сумматоры по модулю два, вторые и третьи двухканальные переключатели и два дополнительных дешифратора, при этом входы второго дешифратора соединены с соответствующими входами генератора корректирующего кода и блока контроля четности, а первые выходы - с выходами генератора корректирующего кода, первые, вторые и третьи входы второй схемы поразрядного сравнения соединены соответственно с выходами генератора логического нуля, генератора корректирующего кода и второго счетчика, а прямой и обратный выходы с вторыми выхода1«1и второго дешифратора, а также с первыми входами соответственно первого и второго дополнительных элементов И, вторые входи которых присоединены к обратному выходу .блока контроля четности первые и вторые входы .вторых двухканальных переключателей подключены соответственно к прямым и обратным выходам триггеров регистра информа-ции, а первые и вторые управляющие входы - соответственно к выходам первого и в,торого дополнительных дешифраторов, входы этих дешифраторов сдединены соответственно с выходами третьих двухканальных переключателей и вторых сумматоров по модулю два, первые и вторые входы которых при-соединены соответственно к выходам генератора корректирующего кода и второго счетчика, а управляю1вие входы- первого и второго дополнительных дешифраторов соединены соответственrto с обратным выходом первого дополнительного элемента И и прямым выходом второго дополнител.ьного элемента И, обратный выход которого подключен к управляющим входам третьих двухканальных .переключателей.

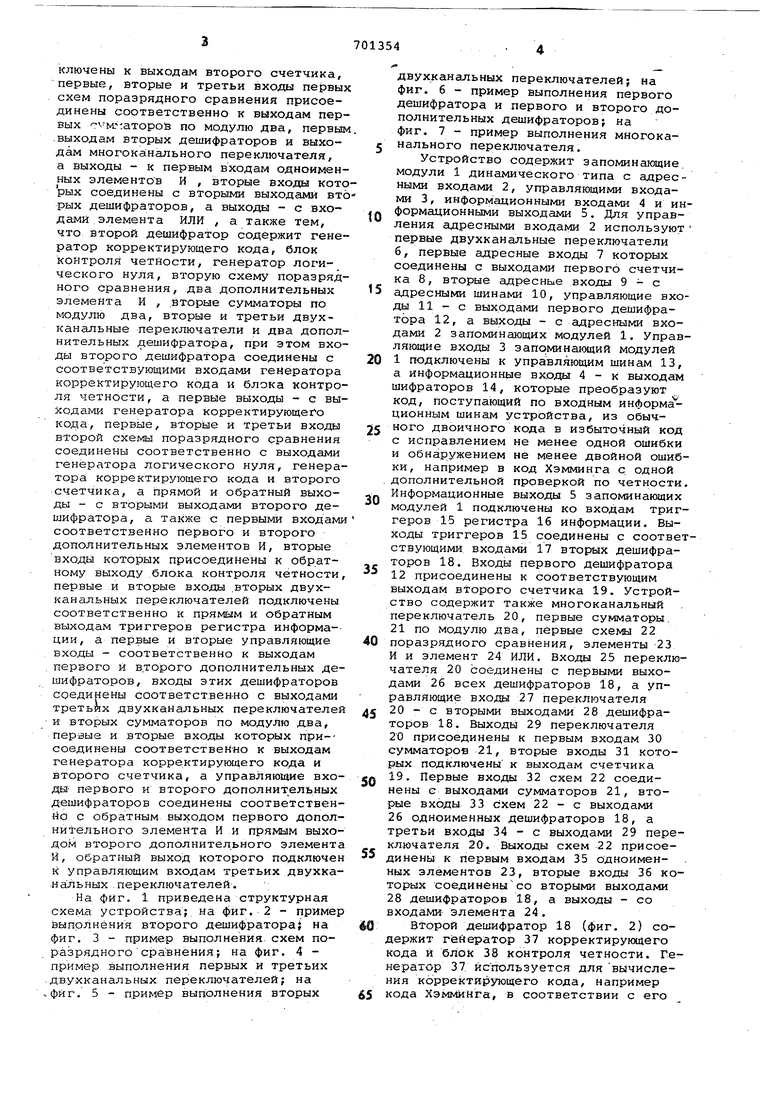

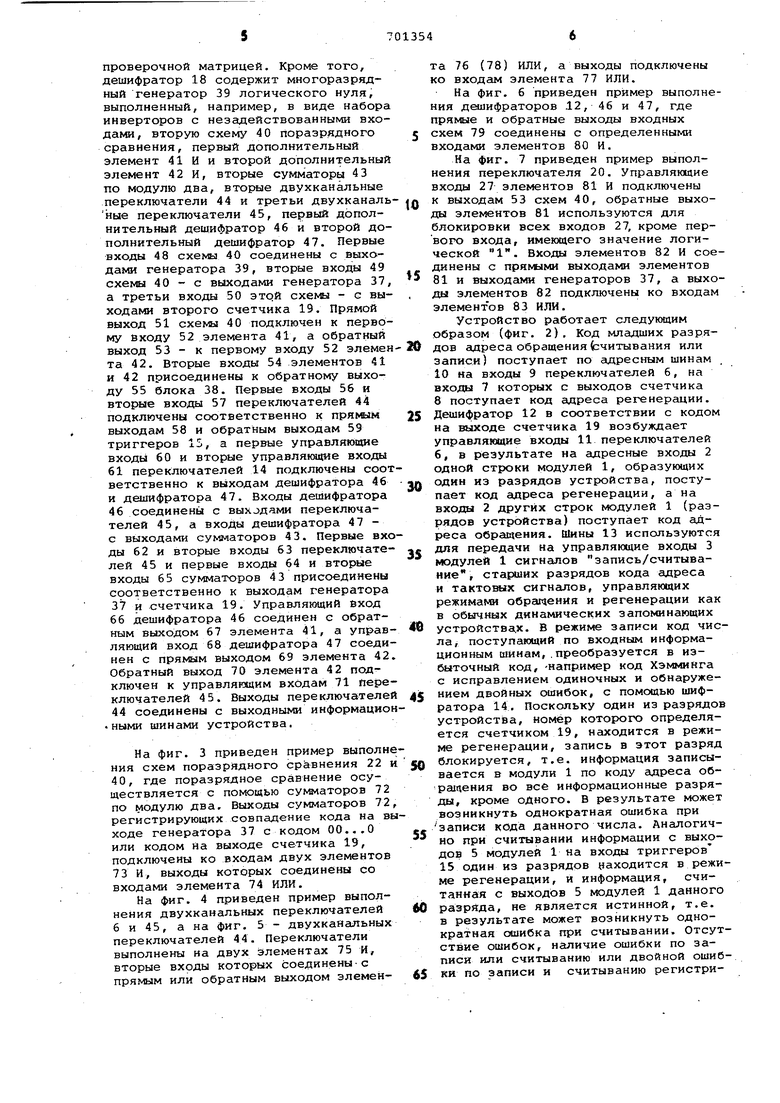

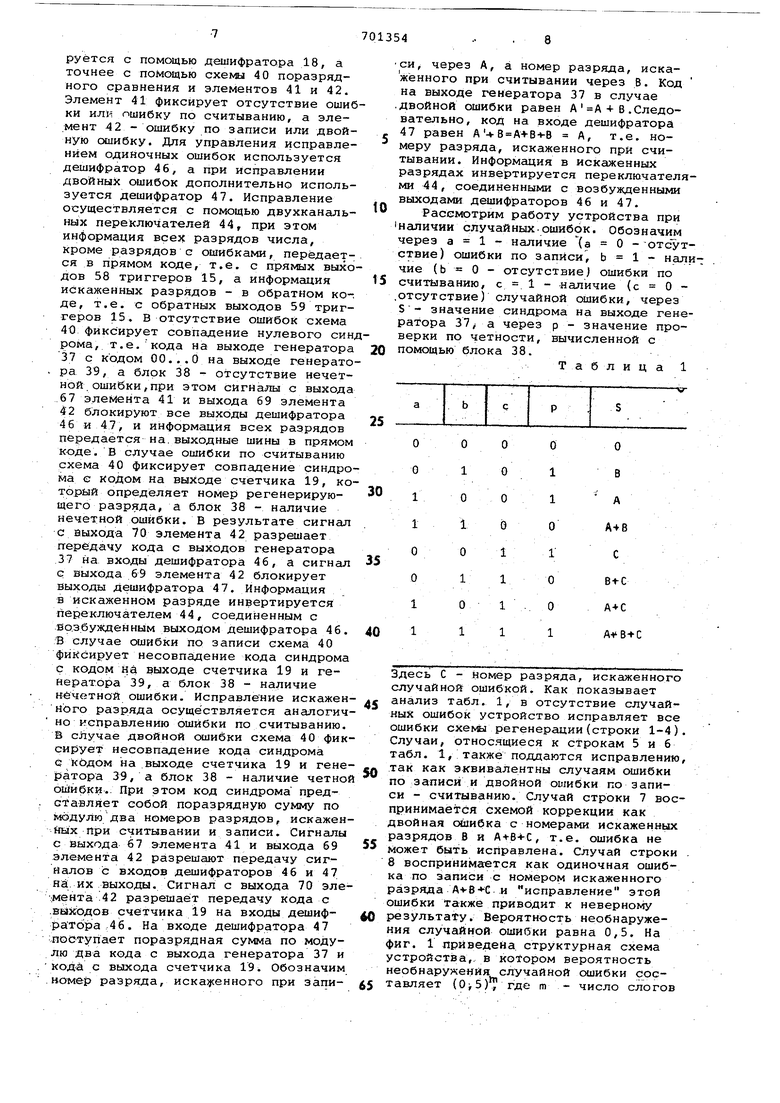

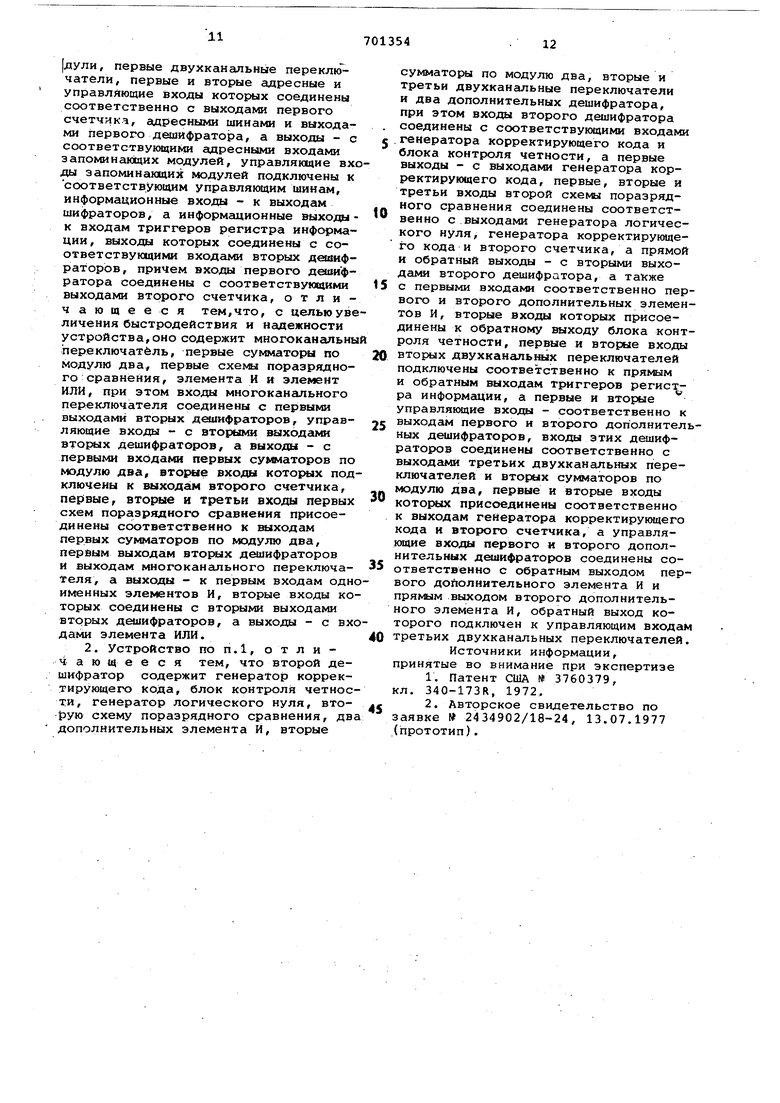

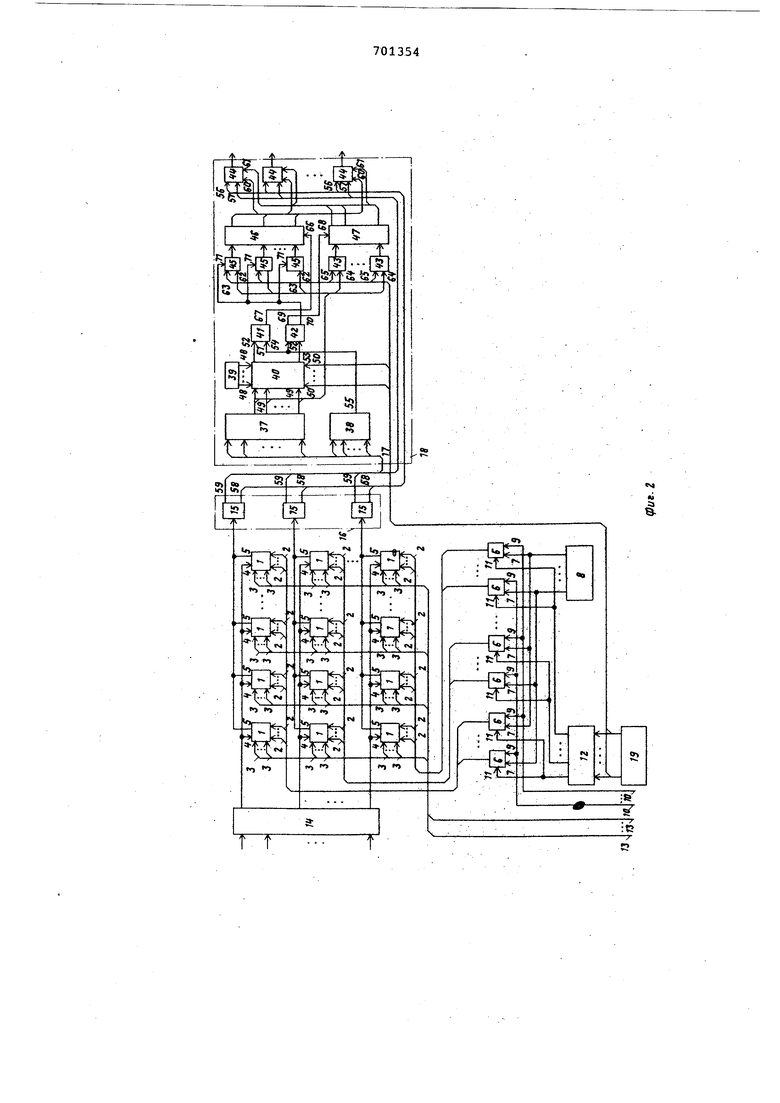

На фИг. 1 приведена структурная схема устройства;, на фиГ. 2 - пример выполнения второго дешифратора; на фиг, 3 - пример выполнения, схем поразрядногосравнения; на фиг. 4 пример выполнения первых и третьих .дв.ухканальных переключателей; на , фйГ. 5 - пример выполнения вторых

двухканальных переключателей; на фиг. 6 - пример выполнения первого дешифратора и первого и второго дополнительных дешифраторов; на фиг, 7 - пример выполнения многоканального переключателя.

Устройство содержит запоминающие, модули 1 динамического типа с адресными входами 2, управляющими входами 3, информационными входами 4 и информационными выходами 5. Для управления адресными входами 2 используют первые двухканальные переключатели 6, первые адресные входы 7 которых соединены с выходами первого счетчика 8, вторые адресные входы 9 - с адресными шинами 10, управляющие входы 11 - с вых.одами первого дешифратора 12, а выходы - с адресными входами 2 запоминающих модулей 1. Управляющие входы 3 запоминающий модулей 1 подключены к управляющим шинам 13, а информационные входаг 4 - к выходам шифраторов 14, Которые преобразуют код, поступающий по входным информа ционным шинам устройства, из обычного двоичного кода в избыточный код с исправлением не менее одной ошибки и обнаружением не менее двойной ошибки, например в код Хэмминга с одной дополнительной проверкой по четности Информационные выходы 5 запоминающих модулей 1 подключены ко входам триггеров 15 регистра 16 информации. Выходы триггеров 15 соединены с соотвествующими входами 17 вторых дешифраторов 18. Входы первого дешифратора 12 присоединены к соответствующим выходам второго счетчика 19. Устройство содержит также многоканальный переключатель 20, первые сумматоры. 21 по модулю два, первые схемы 22 поразрядного сравнения, элементы -23 И и элемент 24 ИЛИ. Входы 25 переключателя 20 соединены с первыми выходами 26 всех дешифраторов 18, а управляющие входы 27 переключателя 20 - с вторыми выходами 28 дешифраторов 18. Выходы 29 переключателя 20 присоединены к первым входам 30 сумматоров 21, вторые входы 31 которых подключены к выходам счетчика 19. Первые входы 32 схем 22 соединены с выходами сумматоров 21, вторые входы 33 схем 22 - с выходами 26 одноименных дешифраторов 18, а третьи входы 34 - с выходами 29 переключателя 20. Выходы схем 22 присоединены к первым входам 35 одноименных элементов 23, вторые входы 36 которых соединенысо вторыми выходами 28 дешифраторов 18, а выходы - со входами элемента 24.

второй дешифратор 18 (фиг. 2) содержит гёйератор 37 корректирующего кода и блок 38 контроля четности. Генератор 37 йспользуется для вычисления корректирующего кода, например кода Хэ1 о№нга, в соответствии с его

проверочной матрицей. Кроме того, дешифратор 18 содержит многоразрядный генератор 39 логического нуля, выполненный, например, в виде набора инверторов с незадействованными входами, вторую схему 40 поразрядного сравнения, первый дополнительный элемент 41 И и второй дополнительный элемент 42 И, вторые сумматоры 43 по модулю два, вторые двухканальные переключатели 44 и третьи двухканальные переключатели 45, первый дополнительный дешифратор 46 и второй дополнительный дешифратор 47. Первые входы 48 схемы 40 соединены с выходами генератора 39, вторые входы 49 схемы 40 - с выходами генератора 37, а третьи входы 50 этой - с выходами второго счетчика 19. Прямой выход 51 схемы 40 подключен к первому Входу 52 элемента 41, а обратный выход 53 - к первому входу 52 элемен та 42. Вторые входы 54 элементов 41 и 42 присоединены к обратному выходу 55 блока 38. Первые входы 56 и вторые входы 57 переключателей 44 подключены соответственно к пря№1М выходам 58 и обратным выходам 59 триггеров 15, а первые управляющие входь 60 и вторые управлякнцие входаа 61 переключателей 14 подключены сооТ ветственно к выходам дешифратора 46 и дешифратора 47. Входы дешифратора 46 соединены с выходами переключателей 45, а входы дешифратора 47 с выходами сумматоров 4 3. Первые входы 62 и вторые входы 63 переключателей 45 и первые входы 64 и вторые входы 65 сумматоров 43 присоединены соответственно к выходам генератора 37 и счетчика 19. Управляющий вход 66 дешифратора 46 соединен с обратным выходом 67 элемента 41, а управляющий вход 68 дешифратора 47 соединен с прямым выходом 69 элемента 42.. Обратный выход 70 элемента 42 подключен к управляющим входам 71 переключателей 45. Выходы переключателей 44 соединены с выходными информацион .ными шинами устройства.

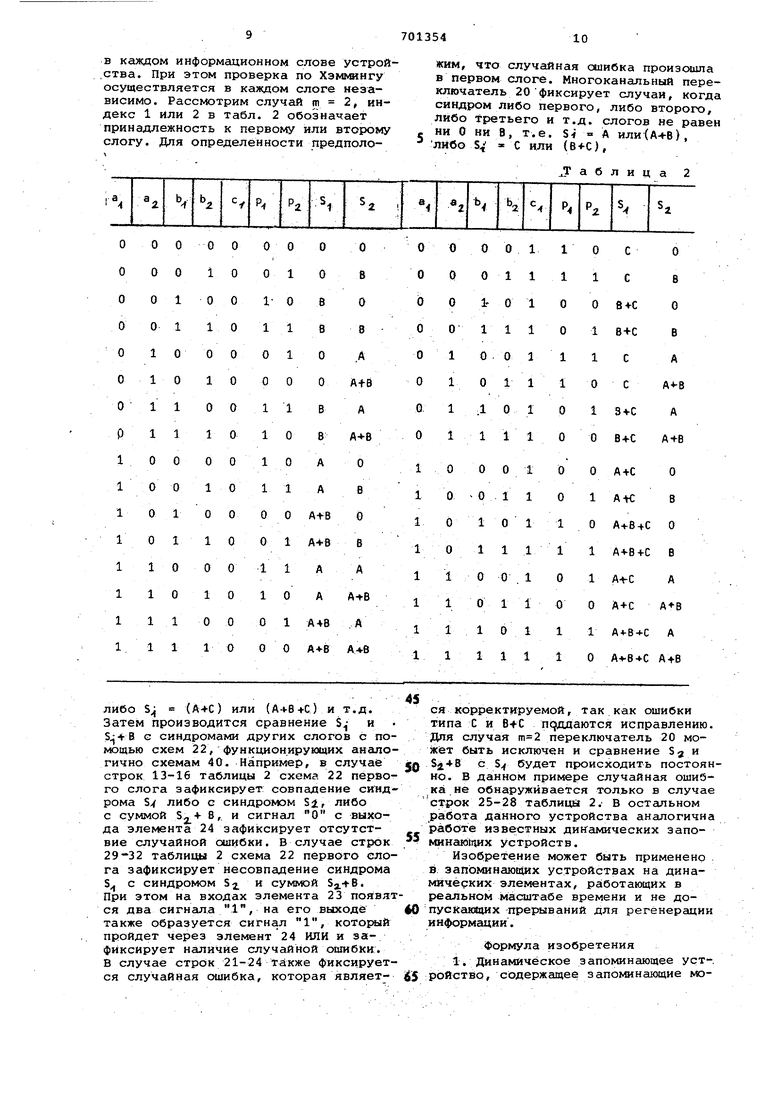

На фиг. 3 приведен пример выполнения схем поразрядного сравнения 22 и 40, где поразрядное сравнение осуществляется с помощью суквлаторов 72 по модулю два. Выходы сумматоров 72, регистрирующих совпадение кода на выходе генератора 37 с кодом 00...О или кодом на выходе счетчика 19, подключены ко входам двух элементов 73 И, выходы которых соединены со входами элемента 74 ИЛИ.

На фиг. 4 приведен пример выполнения двухканальных переключателей 6 и 45, а на фиг. 5 - двухканальных переключателей 44. Переключатели выполнены на двух элементах 75 И, вторые входы которых соединены-с прямым или обратным выходом элемента 76 (78) ИЛИ, а выходы подключены ко входам элемента 77 ИЛИ.

На фиг. 6 приведен пример выполнения дешифраторов 12, 46 и 47, где прямые и обратные выходы входных 5 схем 79 соединены с определенными входами элементов 80 И.

На фиг. 7 приведен пример выполнения переключателя 20. Управляющие входы 27 элементов 81 И подключены 10 к выходам 53 схем 40, обратные выходы элементов 81 используются для блокировки всех входов 27, кроме первого входа, имеющего значение логической 1. Входы элементов 82 И соединены с прямыми выходами элементов

5 81 и выходами генераторов 37, а выходы элементов 82 подключены ко входам элементов 83 ИЛИ.

Устройство работает следующим образом (фиг. 2), Код младших разрядов адреса обращения ;читывания или записи) поступает по адресным шинам 10 на входы 9 переключателей 6, на входы 7 которых с выходов счетчика 8 поступает код адреса регенерации.

25 Дешифратор 12 в соответствии с кодом на выходе счетчика 19 возбуждает управляющие входы 11 переключателей 6, в результате на адресные входы 2 одной строки модулей 1, образующих

30 ° разрядов устройства, поступает код адреса регенерации, а на входы 2 других строк модулей 1 (разрядов устройства) поступает код адреса обращения. Шины 13 используются для передачи на управляющие входы 3

35 модулей 1 сигналов запись/считывание старних разрядов кода адреса и тактовых сигнгшов, управляющих peжимa вI обрагаения и регенерации как в обычных динамических запоминающих

№ устройствах. В режиме записи код числа, поступающий по входным информационным шинам,.преобразуется в избыточный код, -например код Хэмминга с исправлением одиночных и обнаружением двойных ошибок, с помощью шифратора 14. Поскольку один из разрядов устройства, номер которого определяется счетчиком 19, находится в режиме регенерации, запись в этот разряд еп блокируется, т.е. информация записывается в модули 1 по коду адреса обращения во все информационные разряды, кроме одного. В результате может возникнуть однократная ошибка при

, записи кода данного числа. Аналогично при считывании информации с выходов 5 модулей 1 на входы триггеров 15 один из разрядов (}аходится в режиме регенерации, и информация, считанная с выходов 5 модулей 1 данного

60 разряда, не является истинной, т.е. в результате может возникнуть однократная ошибка при считывании. Отсутствие ошибок, наличие ошибки по записи или считыванию или двойной ошибки по записи и считыванию регистрируётся с помощью дешифратора 18, а точнее с помощью схемы 40 поразрядного сравнения и элементов 41 и 42. Элемент 41 фиксирует отсутствие ошибки или ошибку по считыванию, а эле.мент 42 - ошибку по записи или двойную ошибку. Для управления исправлением одиночных ошибок используется дешифратор 46, а при исправлении двойных ошибок дополнительно используется дешифратор 47. Исправление осуществляется с помощью двухканальных переключателей 44, при этом информация всех разрядов числа, кроме разрядов с ошибками, передается в прямом коде, т.е. с прямых выходов 58 триггеров 15, а информация искаженных разрядов - в обратном ко-, да, т.е. с обратных выходов 59 триггеров 15. В отсутствие ошибок схема 40 фиксирует совпадение нулевого синдрома, т.е. кода на выходе генератора 37 с кодом 00...О на выходе генератора 39, а блок 38 - отсутствие нечетной ошибки, при этом сигналы с выхода 67 элемента 41 и выхода 69 элемента 42 блокируют все выходы дешифратора 46 и 47, и информация всех разрядов передается на.выходные шины в прямом коде. В случае ошибки по считыванию схема 40 фиксирует совпадение синдрома с кодом на выходе счетчика 19, который определяет номер регенерирующего разряда, а блок 38 - наличие нечетной ошибки. В результате сигнал с выхода 70 элемента 42 разрешает передачу кода с выходов генератора 37 на входы дешифратора 46, а сигнал с выхода 69 элемента 42 блокирует выходы дешифратора 47. Информация в искаженном разряде инвертируется переключателем 44, соединенным с во.збужденным выходом дешифратора 46. В случае ошибки по записи схема 40 фиксирует несовпадение кода синдрома с кодом ча выходе счетчика 19 и генератора 39, а блок 38 - наличие нечетной ошибки. Исправление искаженного разряда осуществляется аналогично исправлению ошибки по считыванию. В случае двойной ошибки схема 40 фиксирует несовпадение кода синдрома с кодом на выходе счетчика 19 и генеjpaTopa 39, а блок 38 - наличие четной ошибки.. При этом код синдрома предСГавляет собой поразрядную сумму по модулюдва номеров разрядов, искаженных при считывании и записи. Сигналы с 1выхода 67 элемента 41 и выхода 69 элемента 42 разрешают передачу сигналов с входов дешифраторов 46 и 47 на. их выходы. Сигнал с выхода 70 элемента 42 разрешает передачу кода с .вйходов счетчика 19 на входы дешифратора 46. На входе дешифратора 47 поступает поразрядная сумма по модулю два кода с выхода генератора 37 и кода с выхода счетчика 19. Обозначим .номер разряда, искаженного при записи, через А, а номер разряда, искажённого при считывании через В. Код на выходе генератора 37 в случае .двойной ошибки равен А .Следовательно, код на входе дешифратора 47 равен В А, т.е. номеру разряда, искаженного при считывании. Информация в искаженных разрядах инвертируется переключателями 44, соединенными с возбужденными выходами дешифраторов 46 и 47.

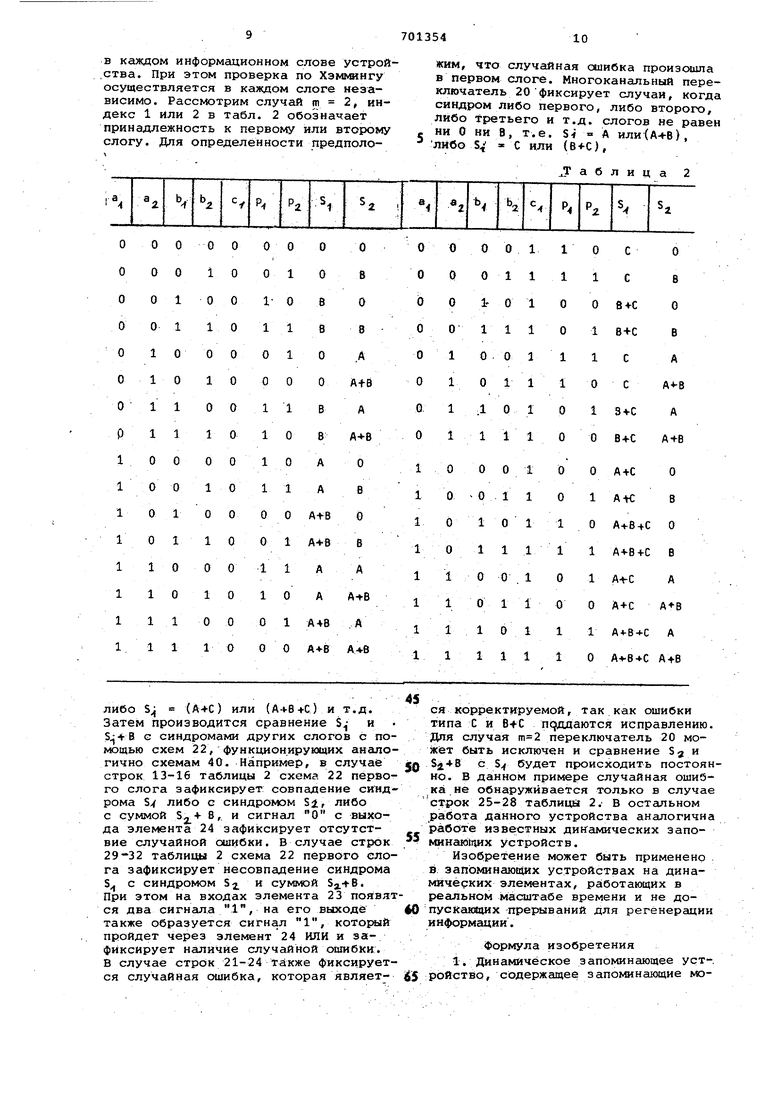

Рассмотрим работу устройства при наличии случайных-ошибок. Обозначим через а 1 - наличие (а О - отсутствие) ошибки по записи, Ь 1 - наличие (Ь О - отсутствие) ошибки по считыванию, с .1 - наличие (с О .отсутствие) случайной ошибки, через S- значение синдрома на выходе генератора 37j а через р - значение проверки по четности, вычисленной с помощью блока 38.

Таблица 1

Здесь С - Номер разряда, искаженного случайной ошибкой. Как показывает анализ табл. 1, в отсутствие случайных ошибок устройство исправляет все ошибки cxeNtJ регенерации(строки 1-4). Случаи, относящиеся к строкам 5 и 6 табл. 1,:также поддаются исправлению, так как эквивалентны случаям ошибки по записи и двойной ошибки по записи - считыванию. Случай строки 7 воспринимается схемой коррекции как двойная ошибка с номерами искаженньдх разрядов В и А- -В-«-С, т.е. ошибка не может быть исправлена. Случай строки . 8 воспринимается как одиночная ошибка по записи с номером искаженного разряда AvB-«-С и исправление этой ошибки также приводит к неверному результату. Вероятность необнаружения случайной ошибки равна 0,5. На фиг. 1 приведена, структурная схема устройства,, в котором вероятность необнаружения случайной ошибки составляет (0;5) где т - число слогов

в каждом информационном слове устрой,ства. При этом проверка по Хэмлингу осуществляется в каждом слоге независимо. Рассмотрим случай m 2, индекс 1 или 2 в табл. 2 обозначает принадлежность к первому или второму слогу. Для определенности предположим, что случайная сшибка проиэсмила в первом слоге. Многоканальный переключатель 20 фиксирует случаи, когда синдром либо первого, либо второго, либо третьего и т.д. слогов не равен ни О ни В, т.е. Sf А или(),

пЧЛп У 3 Г и пы I R

С ИЛИ (BfC),

либо S

таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Запоминающее устройство | 1979 |

|

SU873276A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| ОТКАЗОУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297035C2 |

(А+С) или (А+В+С) и т.д.

либо S

Затем производится сравнение и с синдромами других слогов с помощью схем 22, функционирую(цих аналогично схемам 40. Например, в случае строк 13-16 таблицы 2 схема 22 первого слога зафиксирует совпадение синдрома S либо с синдромом Si, либо с суммой В,, и сигнал О с выхода элемента 24 зафиксирует отсутствие случайной ошибки. В случае строк 29-32 таблицы 2 схема 22 первого слога зафиксирует несовпадение синдрома S с синдромом S. и суммой Sj-t-B. При этом на входах элемента 23 появятся два сигнала 1, на его выходе также образуется сигнал 1, который пройдет через элемент 24 ИЛИ и зафиксирует наличие случайной ошибки. В случае строк 21-24 также фиксируется случайная ошибка, которая являет ся корректируемой, так как ошибки типа С и B-fC п9ДДаются исправлению. Для случая переключатель 20 может быть исключен и сравнение S и Si-4-В с S будет происходить постоянно. В данном примере случайная ошибка не обнаруживается только в случае строк 25-28 таблица 2. В остальном работа данного устройства аналогична работе известных динамических запоминак)1пих Устройств.

Изобретение может быть применено в. эапоминаюЕцих устройствах на динамичёрких элементах, работающих в реальном масштабе времени и не допускающих прерываний для регенерации информации.

Формула изобретения 1. Динамическое запоктнающее уст-. ройство, содержащее запоминающие мо|дули, первые двухканальные переключатели, первые и вторые адресные и управляющие входы которых соединены соответственно с выходами первого счетчика, адресными шинами и выходами первого дешифратора, а выходы - с соответствующими адресными входами запоминающих модулей, управлякадие входы эапоминаюцих модулей подключены к соответствующим управлякндим шинам, информационные входы - к выходам шифраторов, а информгщионные выходык входам триггеров регистра информации , выходы которых соединены с соответствующими входами вторых дешифраторов, причем Bxojya первого дешифратора соединены с соответствующими выходами второго счетчика, отличающееся тем/что, с целью увеличения быстродействия и надежности устройства,оно содержит многоканальный переключатель, первые сумматоры по модулю два, первые cxei-bj поразрядного сравнения, элемента И и элемент ИЛИ, при этом входы многоканального переключателя соединены с первыми выходами вторых дешифраторов, управляющие входы - с вторыми выходами вторых дешифраторов, а выходы - с первыми входами первых суквлаторов по модулю два, вторые входы которых подключены к выходам второго счетчика, первые, вторые и третьи входы первых схем пора:зрядного сравнения присоединены соответственно к выходам первых сумматоров по модулю два, первым выходам вторых дешифраторов и выходам многоканального переключателя, а выходы - к первым входам одноименных элементов И, вторые входы которых соединены с вторыми выходами вторых дешифраторов, а выходы - с входами элемента ИЛИ.

сумматоры по модулю два, вторые и третьи двухканальные переключатели и два дополнительных дешифратора, при этом входы второго дешифратора соединены с соответствующими входами .генератора корректирующего кода и блока контроля четности, а первые выходы - с выходами генератора корректирующего кода, первые, вторые и третьи входы второй схемы поразрядного сравнения соединены соответственно с выходами генератора логического нуля, генератора корректирующего кода и второго счетчика, а прямой и обратный выходы - с вторыми выходами второго дешифратора, а также с первыми входами соответственно первого и второго дополнительных элементов И, вторые входы которых присоединены к обратному выходу блока контроля четности, первые и вторые входы вторых двухканальных переключателей подключены соответственно к прямлм и обратным выходам триггеров регистра информации, а первые и вторые управляющие входы - соответственно к выходам первого и второго дополнителных дешифраторов, входы этих дешифраторов соединены соответственно с выходами третьих двухканальных переключателей и вторых сукматоров по модулю два, первые и вторые входы которых присоединены соответственно к выходам генератора корректирующего кода и второго счетчика, а управляющие входы первого и второго дополнительных д аифраторов соединены соответственно с обратным выходом первого дополнительного элемента И и прямам выходом второго дополнительного элемента И, обратный выход которого подключен к управляющим входа третьих двухканальных переключателей

Источники информации, принятые во внимание при экспертизе

«ч

W

t

Е

-

Ъ-Г

с

W5; A 53(3S) W «31; ,5V ,% Й (rt) Y«; /«;

(Olsj) еф) (ф) «o((i) W ff 5S S7 iput.f

Авторы

Даты

1981-09-07—Публикация

1977-12-29—Подача