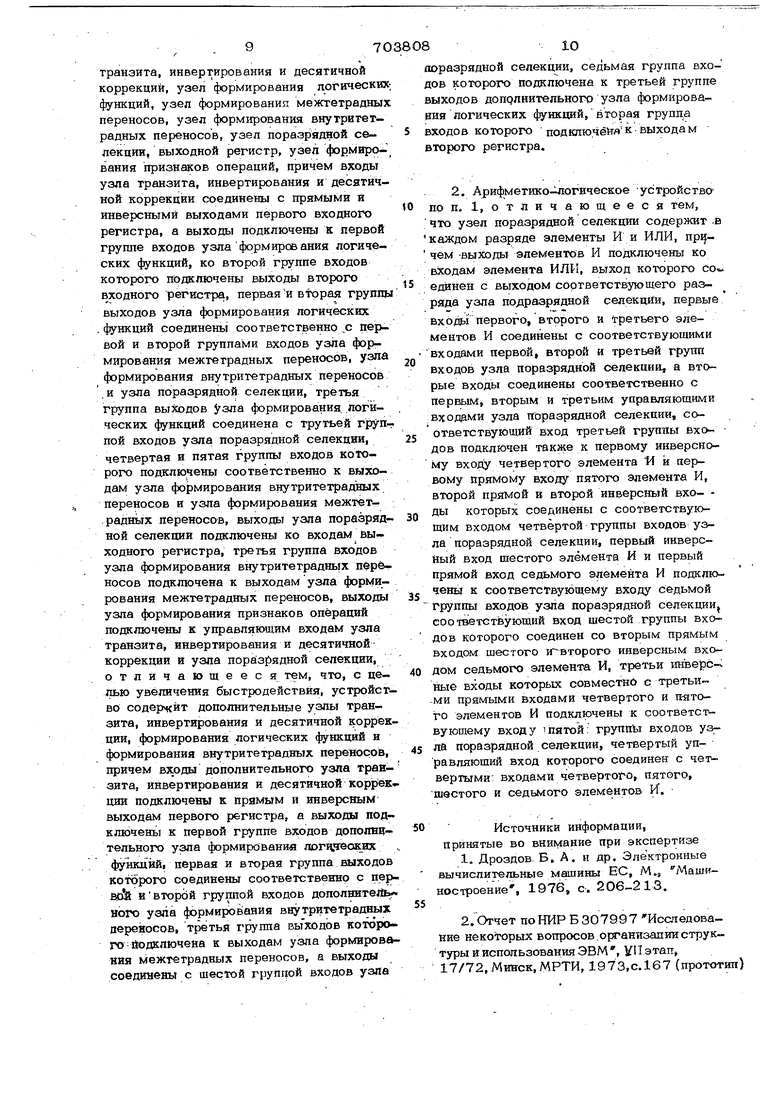

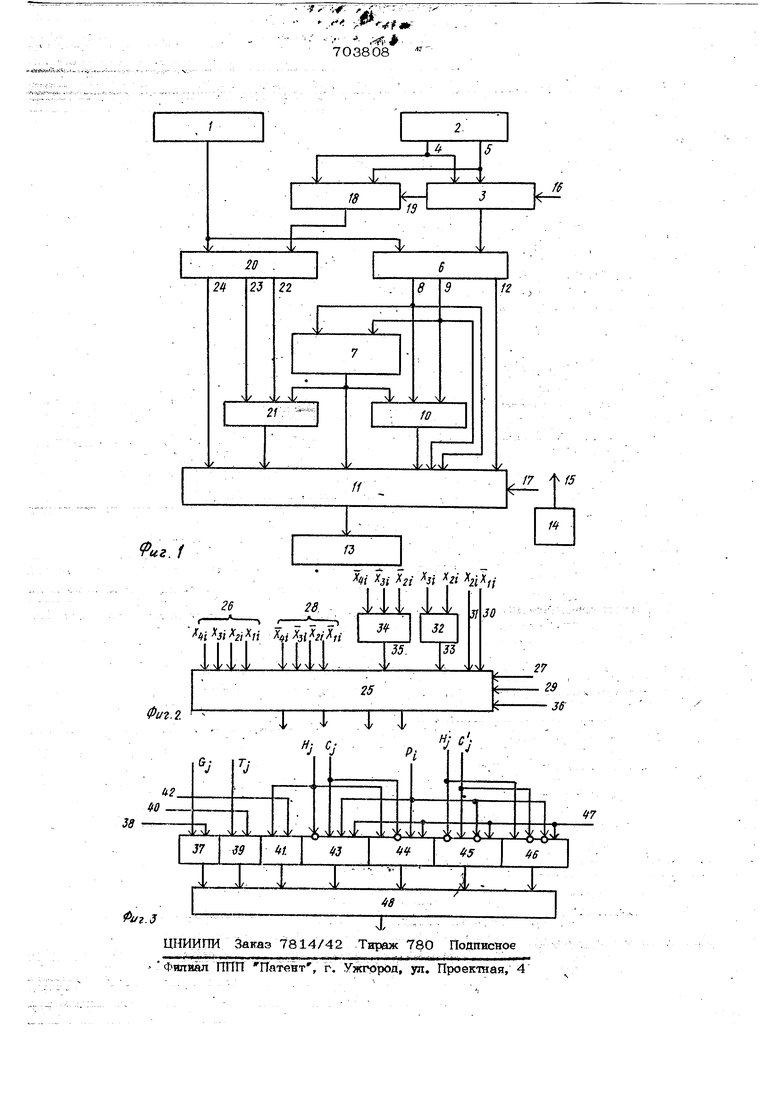

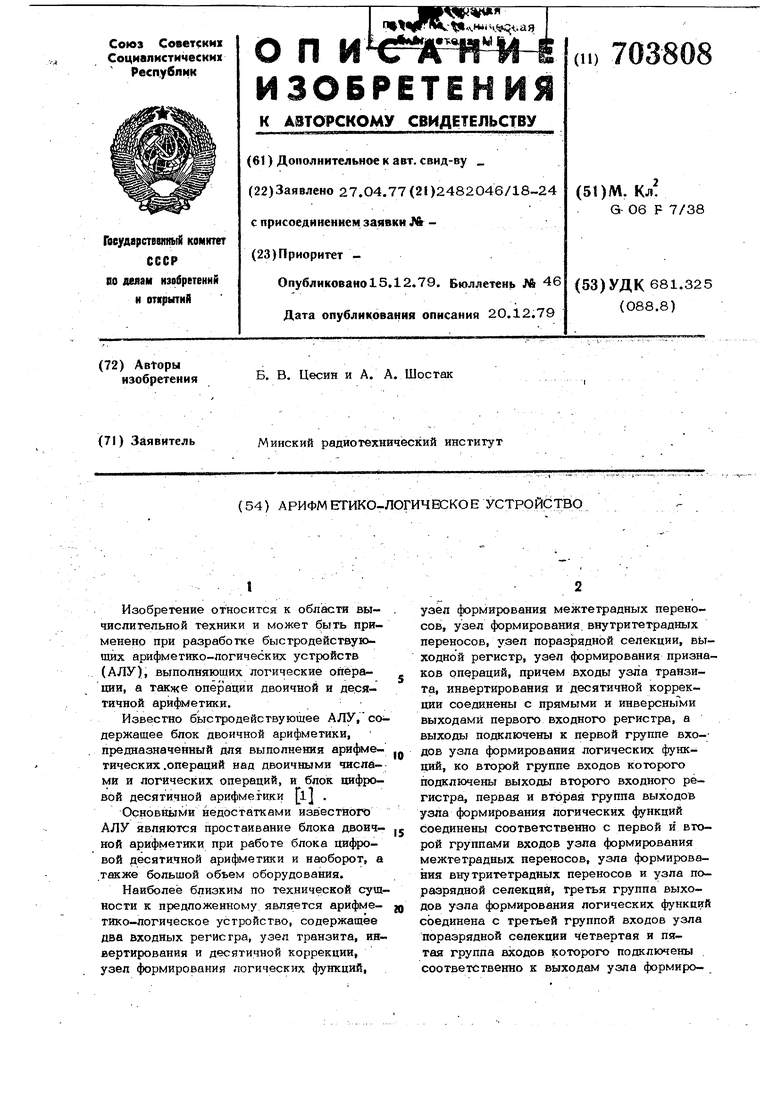

-.. .1. Изобретение относится к области вычислительной техники и может быть применено при разработке быстродействующих арифметико-логических устройств (АЛУ), выполняющих логические операции, а также операции двоичной и десятичной арифметики. Известно быстродействующее АЛУ, со держащее блок двоичной арифметики, предназначенный для выполнения арифметических .операций над двоичными числами и логических операций, и блок цифровой десятичной арифметики l . Основными недостатками известного АЛУ являются простаивание блока двоичной арифметики при работе блока цифровой десятичной арифметики и наоборот, а также большой объем оборудования. Наиболее близким по технической сущности к предложенному является арифме- тико-логическое устройство, содержащее два входных регистра, узел транзита, инвертирования и десятичной коррекции, узел формирования логических функций. уэел формирования межтетрадных переносов, узел формирования, внутритетрадных переносов, узел поразрядной селекции, вЫходной регистр, узел формирования признаков операций, причем входы узла транзита, инвертирования и десятичной коррекции соединены с прямыми и инверсными выходами первого входнотх регистра, а выходы подключены к первой группе вхо-дов узла формирования логических функций, ко второй группе входов которого подключены выходы второго входного регистра, первая и втчэрай группа выходов узла формирования логических функций соединены соответственно с первой и второй группами входов узла формирования межтетрадных переносов, узла формирования внутритетрадных переносов и узла поразрядной селекции, третья группа выходов узла формирования логических функций соединена с третьей группой входов узла поразрядной селекции четвертая и пятая группа входов которого подключены соответственно к выходам узла формирования внутритетрадных переносов и узла формирования межтетра-дных переносов, выходыузла поразрядной селекции подклю ченьГкд вхЬд)эм выходного регистра, третья группа входов узла формирования внутритетрадных переносов подключена к выходам узла формирования межтетрадных переносов, выходы узла формирования признаков операций подкпйчены к управляющим входам узла транзита, инвертиррч вания и десятичной коррекции и узла поразрядйой селекции . Основнымнедостатком известного АЛУ является влияние узлов выходного десяти ного корректора и поразрядной селекции на временной цикл АЛУ. Целью изобретения является увеличение быстродействия арифметико-логического устройства.: Поставпенная цель достигается тем, что устройство содержит дополнительньш узлы транзита, инвертирования и десятичной коррекции, формирования логических функций л формирования внутритетрадных переносов, причем входы дополнительного узпа транзита, инвертирования и десятичной коррекции подключены к прямым и инверсным выходам первого регистра, а выходы подключены к первой группе входов дополнительного узла формирования логическихфункций, первая и вторая груп пы выходов которого соединены соответственно с первой и второй группой входов дополни те льног о узла формирования, внутритетрадных переносов, третья группа выходов которого подключены к ВЬ1ХОдам узла формирования межтетрадных переносов, а выходы соединены с шестой группой входов узла поразрядной селекции седьмая группа входов которого подключе на к третьей группе выходов дополнительного узла формирования логических функций, вторая rpyntia входов которого иодключена к выходам второго регистра. Кроме того, узел поразрядной селекции содержит в каждом разряде элементгы И и ИЛИ, причем выходы элементов И.подключены ко входам элемента ИЛИ, выход которого соединен с выходом с.оответству юшего разряда узла поразрядной селекции, первые входы первого, второго и тре тьего элементов И соединещл с соответствующими входами первой, второй и третьей групп входов узпа поразрядной селек ции, а вторые входы соединены соответс-г венно с первым, вторым и третьим управ ляющими входами узпа поразрядной сепек ии, соответствующий вход третьей группы ходов подключен также к первому инверсному ходу четвертого элемента И и первому рямому входу пятого элемента И, второй рямой и второй инверсный входы которых соединены с соответствующим входом четвертой группы входов узла поразрядной селекции, первый инверсный вход шестого элемента И и первый прямой вход седьмого элемента И подключены к соответствующему вх-оду седьмой группы входов узла поразрядной селекции, соответствующий вход шестой группы входов которого соединен со вторым прямым входом шестого и вторым инверсным входом седьмого элемента И, третьи инверсные входы которых совместно с третьими прямыми входами четвертого и пятого элементов И подключены к соответствующему входу пятой группы входов узла поразрядной селекции, четвертый управляющий вход которого соединен с четвертыми входами четвертого, пятого, шестого и седьмогоэлементов И, Сущность изобретения поясняется чертежами, где на фиг. 1 приведена структурная схема АЛУ, на фиг. 2 - функциональная схема узла транзита, инвертирования и десятичной коррекции (для определенности рассматривается i-я тетрада), на фиг. 3 - функциональная схема узла поразрядной селекции (для определенности рассматривается j-и разряд i-ой тетрады узла поразрядной селекции). Устройство содержит два регистра 1 и 2, узел 3 транзита, инвертирования и десятичной коррекции, входьх которого соединены с прямым 4 и инверсным 5 выходами входного регистра 2, узел 6 формирования логических функций И, ИЛИ, исключающее ИЛИ, входы которого соединены с выходом входного регистра 1 с выходом узла 3 транзиста, инвертирования и десятичной коррекции, узел 7 формирования межТетрадных переносов,, входы которого соединены с выходами 8 и 9 значений функций соответственно И и Или узла 6 формирования логических функшй, узел Ю формирования внутритетрадных переносов, входы которого соединены с выходом узла 7 формирования межтетрадных переносов, а также с выходами 8 и 9 значений функции соответственно И и ИЛИ узла 6 формирования логических функций, узел 11 поразрядной селекции, входы которого соединены с выходами 8, 9 и 1.2 значений 57038 функции соответственно И, ИЛИ, исключающее ИЛИ узла 6 формирования логических функций, выходной регистр 13 узел 14 формирования признаков операций выходы 15 которого соединены с упра&ляюшими входами 16 и 17 соответственно узла транзита, инвертирования и десятичной коррекции и узла 11 узел 18 транзита, инвертирования и деся тичной .коррекции, входы которого соединены с прямым 4 и инверсным 5 выходами входного регистра 2, а управляющий вход 19 соединен с выходом 15 узла 14 формирования- признаков операции, дополнительный узел 20 формирования логических функций И, ИЛИ, исключающее ИЛИ, входы которого соединены с выходом входного регистра 1 и с выходом дополнительного узла 18 транзита, инвертирования и-десятичной коррекции, дополнител ный узел 21 формирования внутритетрадных переносов, входы которого.соединены с выходами 22 и 23 значений функций соответственно И и ИЛИ узла 20 форми- рования логических функций, а также с выходом узла 7 формирования межтетрадных переносов. Дополнительные входы узла 11 поразрядной селекции соединены с выходом 24 значения функции исключающее ИЛИ узла 20 формирования логических функций, с выходами узлй 7 формирования межтетрадных переносов и узлов 10 и 21 формирования внутритетрадных переносов. Выход узла 11 поразрядной селекции соединен со входом выходного регистра 13. Узел 18 транзита; инвертирования и десятичной коррекции (фиг, 2) содержит выходной коммутатор 25, входы 26 которого соединены с прямыми ( (Х, входами входного регистра 2 значе ргя которых поступают на выходы коммутатора 25 при наличии управляющего сигнала со входа 27, Входы 28 коммутатора 25 соединены с инверсными (Xi, t) выходами вход ного регистра 2, значения которых поступают на выходы коммутатора 25 при наличии упр авляющегр сигнала coJgxoдa 29. Вход ЗО коммутатода 25.с ёдинёа с выхода значения вход: кого регистра 2, вход 31 - с выходом . значения к „: входного регистра 2. В узел 18 входят также элемен исключающее ИЛИ 32, входы которого соединены с выходами значений X , Х -л входного регистра 2, а его выход соединен со входом 33 коммутатора 25, элемент И 34, входы которого соединены с выходами значений ,- входного регистра 2, а его выход соединен со входом 35 коммутатора 25, значения с входов 30, 31, 33 и 35 которого поступают на выходы коммутатора 2 5 при наличии управляющего сигнала со входа 36. . . Узел 11 поразрядной селекции (фиг. 3) содердит элемент.И 37, прямой вход которой соединен с выходом значения функции И узла 6 формирования логических функций, значение Q « поступает на выход узла 11 поразрядной селекции при наличии на втором прямом входе элемента И 37 управляющего сигнала со входа 38, элемент И 39, прямой вход которого соединен с выходом значения Tj функции ИЛИ узла 6 формирования логических функций, поступающего на выход узла 11 поразрядной селекции при наличии на втором прямом входе элемента И 39 управляющего сигнала со входа 40, элемент И 41, прямой ВХО.Д которого соединен с выходом значения Ни функции- исключающее ИЛИ узла 6 формирования логических функций, поступающего на выход узла 11 поразрядной селекции при наличии на втором прямом входе элемента И 41 .управляющего,сигнала со входа 42. Выход значения Иj функции исключающее ИЛИ узла 6 формирования логических функций соединен с инверсным входом элемента И 43 и с прямым входом элемента И 44. Выход C-j узла 10 формирования внутритетрадных переносов соединен с прямым входом элемента И 43 и с инверсным входом элемента И 44. Выход значения Hj функции исключаю-, щее ИЛИ узла 20 формирования логи.чеСК.КХ. функций соединен с инверсным входом элемента И 45 и с прямым входом эле-, мента И 46. Выход 2j узла 21 формирования внутритетрадных переносов соединен с прямым входом элемента И 45 и с инверсным входом элемента И 46. Выход узла 7 формирования межтетрадных переносов, формирующего перенос из i -ой тетрады, в которой находится j -и разряд, соединен с прямыми входами элемента И 43 и элемента И 44, а также с инверсными входами элемента И 45 и элемента И 46. При наличии управляющего сигнала со входа 47 на прямых Входах элементов И 43-46 происходит передача информации с их входов на выход узла 11 поразрядной селекции и элемент ИЛИ 48, входы которого соединены свыходами элементов И 37, 39, 41 и 43-46. АЛУ работает следующим образом. При выполнений логических операций операнды поступают на входные регистры 1 и 2. Узлы 3 и 18 транзита, инвертирования и десятичной коррекции пропускают информацию транзитом (без преобразования). С помощью узла 6 формированйя логических функций выполняются, логические операции И ИЛИ, исключающее ИЛИ ,.Выходы 8, 9 и 12 соединены с узлом 11 поразрядной селекции, на управляющий вход 17 которого подан сигнал Нужной логической операции, после чего на выходе узла 11 появится результат, который записывается в выходной регистр 13.-,,При выполнении операций десятичной, арифметики в случае, когда-операндь имеют одинаковые знаки, они обрабатываются в прямых кодах . Операнды посту пайуг на .входные регистры 1 и.2. Узел 18 транзита, инвертирования идесятичной коррекции пропускает информацию транзитбм, а узел 3 транзита,инвертирования и десятичной коррекции осу-щест, вляёт увеличение каждой десятичной цифры на шесть. Межтетрадные переносы в узле 7 формируются сучетом избытка, введенного в каждую десятичную цифру. Внутритетрадные переносы , сформированные узлом 10 формирования внутритетрадных переносов, формируются с учетом избытка шесть, а внутрнтетрадные переломы, сформированные узлом 21 формирования внутри тетрадных переносов - без учета избытка, шесть. Узел 6 формирования логических функций формирует резуль тат поразр адногосл68 :ёния по модулю дв с учетом введенного избытка Шесть, а узел 20 формирования логических функций - без учета избытка шесть. В узле 11 поразрядной селекции осуществляется поразрядное сложение по модулю два результата, сформированного .узлом 10 фор мирования внутритетрадных переносов, и значения функции исключающее ИЛИ, сформированного узлом 6 формирования логических ф} шсций, а тжжё поразрядное слежение по модулю два результата,сфор мированного узлом 21 формирования, внутритетрадных переносов, и значения х})ункции исключаюш.ее ИЛИ, сформиро: ванного узлом 20 формирования логических функций. При этом, если возник перенос из ,i ой тетрады, на выход посту пает результат тетрады, учитывающий введенный избыток шесть, а если такого переноса не возникло - неучитывающий избыток щесть. Знак результата определяется знаком операндов. В случае, когда операнды имеют разные знаки, операнд с положительным знаком подается в входной регистр 1, операнд со знаком минус - во входной ре- j гистр 2. При этом узел 3 транзита; инвертирования и десятичной коррекции осуществляет инвертирование операнда, а узел 18 транзита, инвертирования и десятичной коррекции - формирование дополшения до девяти казкдой десятичной цифры. Далее вычислительный процесс происходит аналогично рассмотренному выше.Если результат получается со знаком минус, TQ для получения прямого кода отрицательно1Ч числа .последний -поступает во входной регистр 2, а во входной регистр 1 записываются нули Затем все происходит аналогично сложению десятичных чисел. . При выполнении операций двоичной арифметики при-сложении операндов узлы 3 и 18 транзита, инвертирования и десятичной коррекции пропускают информацию транзитом, а при вычитании - осуШёствдяют инверсию операнда (при вычитании операнд поступает на входной регистр 2). В дальнейшем процесс происходит аналогично роцессу выполнения операций десятичной арифметики при одинаковых знаках операндов. Однако,независимо от того, возник перенос из i-ой тетрады, где находится j-и разряд, или нет, результат получится одинаковый, так как узлы 3 и 18 транзита, инвертирования и десятичной коррекции дают на вйхбде одинаковые Значеййя. Данное арифметико-логическое устройство позволяет повысить быстродействие .примерно на 25% при увеличении объема оборудования на 20% (формат обрабатываемой информации двухбайтный, формирование разрядных переносов по параллельно-параллельному способу). Это достигнуто за счет того, что из .АЛУ исключен узел выходного десятичного корректора, вносящий временную задержку при выполнении всех операций, а узел пора ядной селекции объединен с узлом поразрядного формирования суммы, что фактически исключило временную задержку и на редакцию информации. Формула из о«б р е т е н и я 1. Ари(} летико-лргическое устройство, содержащее два входных регистра, узел транзита, инвертирования и десятичной коррекций, узел формирования погических функций, узел формирования межтетрадных переносов, узел формирования внутритет- радных переносов, узел поразрядной селекции, выходной регистр, узел формирования признаков операций, причем входы узла транзита, инвертирования и десятичной коррекции соединены с прямыми н инверсными выходами первого входного регистра, а выходы подключены к первой группе входов узла формирования логиче ских функций, ко второй группе входов которого подключены выходы второго входного регистра, первая-и вторая группы выходов узла формирования логических . функций соединень соответственно с первой и второй группами входов узла формирования межтетрадных переносов, узла формирования внутритетрадных переносов .и узла поразрядной селекции, третья группа выходов узла формирования, логических функций соединена с трутьей группой входов узла поразрядной селекции, четвертая и пятая группы входов которого подключены соответственно к выходам узла формирования внутритетрадных переносов и узла формирования межтетраднь1х переносов, выходы узла поразрядной селекции подключены ко входам выходного регистра, третья группа входов узла формирования внутритетраднь Х переносов подключена к выходам узла формирования межтетрадных переносов, выходы узла формирования признаков операций подключены к управляющим входам узла транзита, инвертирования и десятичной коррекции и узла поразрядной селекции, отличающееся тем, что, с целью увеличения быстродействия, устройство содержит дополнительные узлы транзита, инвертирования и десятичной коррек ции, формирования логических функций и формирования внутри те традньтх переносов, причем входы дополнительного узла транзита, инвертирования и десятичной коррек ции подключены к прямым и инверсным выходам первого регистра, а выходы подключень к первой группе входов дополнцтельного узла формирования логнягеоких функций, первая и вторая группа выходов которого соединены соответственно с перBtfe ивторЬй группой входов дополннтей него узла формирования внутритетрадных переносов, третья группа выходов которого -йодключена к выходам узла формирова ния межтетрадных переносов, а выходы соединены с шестой группой входов узла 70 10 поразрядной селекции, седьмая группа вхоов которого подключена к третьей группе выходов допрлнительного узла формирования логических функций,вторая группа ходов которого подключё тяк выходам торого регистра. 2. Арифметико-логическое -устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел поразрядной селекции содержит .в каждом разряде элементы И и ИЛИ, -выходы элементов И подключены ко входам элемента ИЛИ, выход которого со, единен с выходом соответствующего разряда узла подразрядной селекции, первые входьГ первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла поразрядной селекции, а вторые входы соединены соответственно с nepEbiM, вторым и третьим управляющими входами узла поразрядной селекции, соответствующий вход третьей группы вхо-. дов подключен также к первому инверсному Bxojc четвертого элемента М и первому прямому входу пятого элемента И, второй прямой и второй инверсный вхо- ды которых соединены с соответствующим входом четвёртой группы входов узла поразрядной селекции, первый инверсйый вход шестого элемента И и первый прямой вход седьмого элемента И подключены к соответствующему входу седьмой группы входов узла поразрядной селекции, соответствующий вход шестой группы входов которого соединен со вторым прямым входом шестого и второго инверсным входом седьмого элемента И, третьи ifflBepc-: ные входы которых совместно с третьи.ми прялл1ым;и входами четвертого и п-ятого элементов И подключены к соответствующему входу ПЯТОЙ: группы входов узла поразрядной селекции, четвертый управляющий вход которого соединен с четвертыми: входами четвертого, пятого, шестого и седьмого элементов И. Источники информации, Принятые во внимание при экспертизе 1,Дроздов. Б. А. и др. Электронные вычислительны® машины ЕС, М., Машиностроение, 1976, с. 206-213. 2.Отчет по НИР Б 30799 7 Исследование некоторых вопросов,организации структуры и использования ЭВМ , УП этап, 17/72, Мийск,МРТИ, 1973,С.167 (прототип)

X /-Vf) .- ...703808

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

Ы

2И 2Ъ 22

2f.

«г./

J

/if

в 9

12

fO

/7 ф/5

Авторы

Даты

1979-12-15—Публикация

1977-04-27—Подача